#### ZHCS185A - SEPTEMBER 2011 - REVISED JANUARY 2012

度以获得脉宽调制频谱定型的额外的灵活性。

双通道,高压-多级输出完全集成超声波发射机 查询样品: TX517

|                                                                                         | 说明                                                                                                          |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

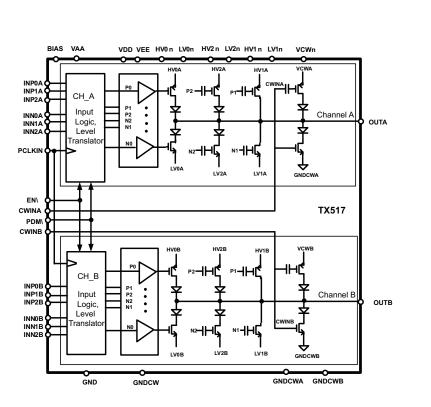

| <ul> <li>输出电压:</li> <li>差分模式下,高达 200Vpp</li> <li>峰值输出电流: ±2.5A</li> <li>多级输出</li> </ul> | TX517 是一款完全集成,双通道,高压发射器。它特别设计用于高要求的医疗超声波应用,此应用要求一个多级高压脉冲波形。此输出级设计传送典型值为±2.5A的峰值输出电流,摆幅200Vpp。               |

| <ul> <li>差分: 17级</li> <li>单端: 5级</li> <li>集成:</li> <li>电平转换器</li> <li>驱动器</li> </ul>    | TX517 是一个完整发射器解决方案,此方案每通道含<br>低压输入逻辑,电平转换器,栅极驱动器和P通道,N<br>通道金属氧化物半导体场效应晶体管 (MOSFET)。<br>TX517 还包含一个 CW 输出级。 |

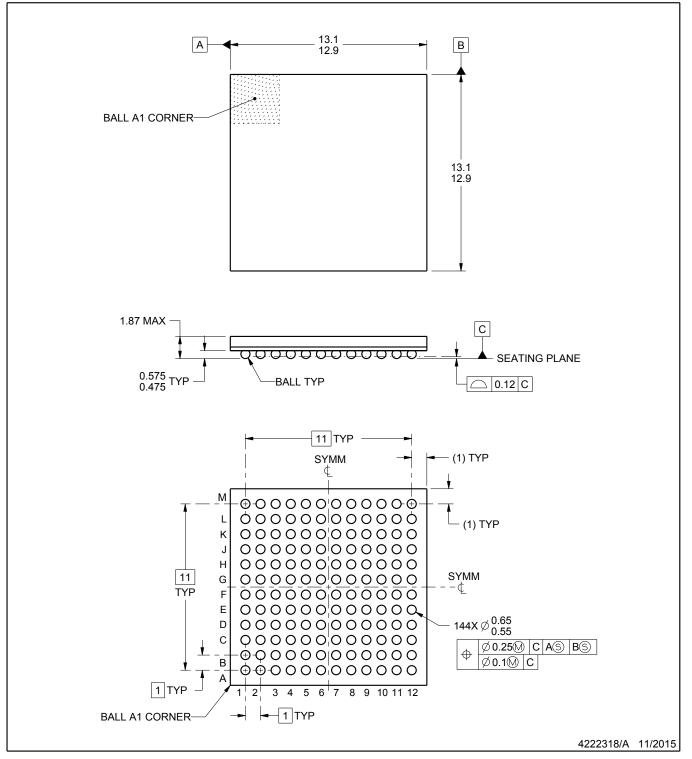

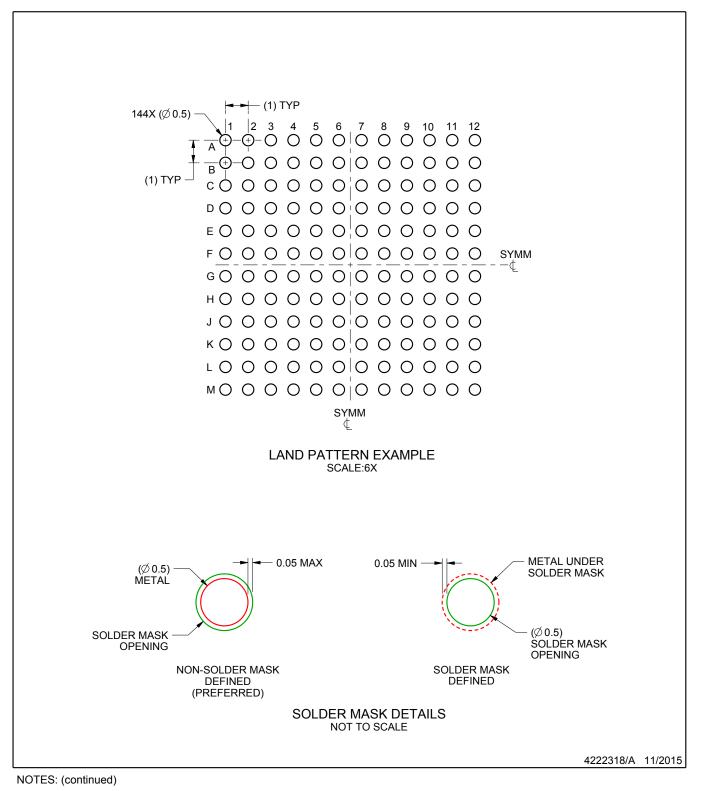

| <ul> <li>高压输出级</li> <li>CW 输出</li> <li>TX 输出更新率</li> </ul>                              | TX517 采用球状引脚栅格阵列 (BGA) 封装,此封装是<br>无铅 (RoHS兼容) 并且绿色环保。 它的额定运行温<br>度为0℃ 至 85℃。                                |

| <ul> <li>最高 100MSPS</li> <li>最小外部组件</li> <li>小型封装: 13 x 13mm球状引脚栅格阵列(BGA)封装</li> </ul>  | 17个电平脉冲发生器芯片:<br>当与变压器一同使用时,此芯片包含2个5级通道来<br>形成一个单一17级发射器单元。此器件设计用于驱动<br>处于不同输出电平上的变送器,而且能调制输出脉冲宽            |

# 应用范围

- 医疗超声波

- 高压信号生成器

TEXAS INSTRUMENTS

#### ZHCS185A-SEPTEMBER 2011-REVISED JANUARY 2012

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# PACKAGING/ORDERING INFORMATION<sup>(1)</sup>

| PACKAGED DEVICES | PACKAGE TYPE PACKAGE MARKING TRANSPORT MEDIA, QUANTITY |       | ECO STATUS <sup>(2)</sup> |                |

|------------------|--------------------------------------------------------|-------|---------------------------|----------------|

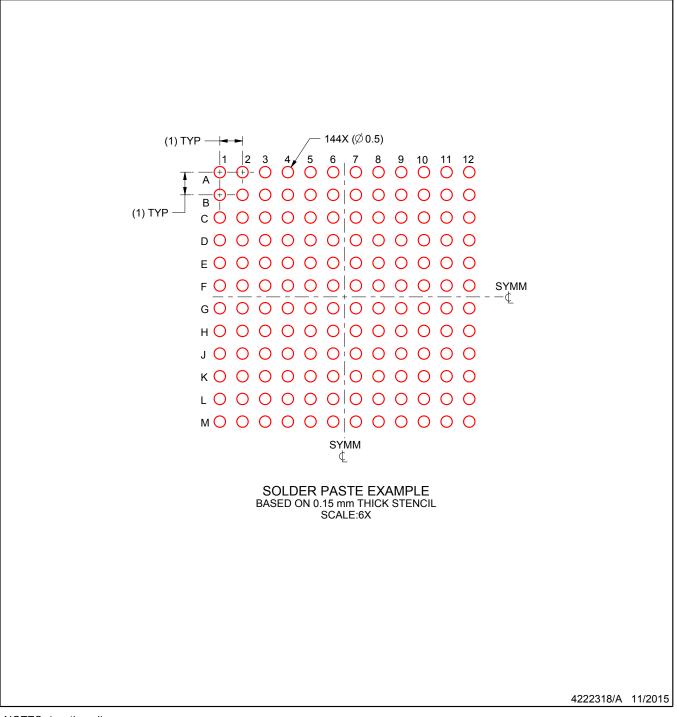

| TX517IZCQ        | BGA-144                                                | TX517 | Tray                      | Pb-Free, Green |

(1) NOTE: These Packages conform to Lead-Free and Green Manufacturing Specifications

(2) Eco-Status information: Additional details including specific material content can be accessed at www.ti.com/leadfree

**GREEN:** Ti defines Green to mean Lead (Pb)-Free and in addition, uses less package materials that do not contain halogens, including bromine (Br), or antimony (Sb) above 0.1% of total product weight.

N/A: Not yet available Lead (Pb)-Free; for estimated conversion dates, go to www.ti.com/leadfree.

**Pb-FREE:** Ti defines Lead (Pb)-Free to mean RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and, if designed to be soldered, suitable for use in specified lead-free soldering processes.

### **DEVICE INFORMATION**

|   |      |      |      |      | I    | -    | 44 PINS<br>VIEW |      |     |       |       |        |   |

|---|------|------|------|------|------|------|-----------------|------|-----|-------|-------|--------|---|

|   | 1    | 2    | 3    | 4    | 5    | 6    | 7               | 8    | 9   | 10    | 11    | 12     |   |

| Α | HV2B | GND  | HV1B | HV0B | VCWB | EN\  | VAAB            | NC   | NC  | INP1B | INN1B | INP2B  | A |

| в | NC   | LV1B | LV1B | LV1B | LV1B | LV1B | GND             | NC   | NC  | GND   | VAAC  | INN2B  | в |

| с | OUTB | LV1B | LV1B | LV1B | LV1B | LV1B | CWINB           | VEE  | VEE | VEE   | VEE   | INNOB  | С |

| D | NC   | LV1B | LV1B | LV1B | LV1B | LV1B | GNDCWB          | VEE  | VEE | VEE   | VEE   | INPOB  | D |

| Е | LV2B | LV1B | LV1B | LV1B | LV1B | LV1B | VDDB            | VEE  | VEE | VEE   | VEE   | PCLKIN | Е |

| F | LV1B | LV1B | LV1B | LV1B | LV1B | LV1B | LV0B            | VEE  | VEE | VEE   | VEE   | GND    | F |

| G | LV1A | LV1A | LV1A | LV1A | LV1A | LV1A | LV0A            | VEE  | VEE | VEE   | VEE   | VDD    | G |

| н | LV2A | LV1A | LV1A | LV1A | LV1A | LV1A | VDDA            | VEE  | VEE | VEE   | VEE   | CWINA  | н |

| J | NC   | LV1A | LV1A | LV1A | LV1A | LV1A | GNDCWA          | VEE  | VEE | VEE   | VEE   | INP0A  | J |

| к | OUTA | LV1A | LV1A | LV1A | LV1A | LV1A | GND             | VEE  | VEE | VEE   | VEE   | INNOA  | к |

| L | NC   | LV1A | LV1A | LV1A | LV1A | LV1A | GND             | NC   | NC  | GND   | VAAD  | INN2A  | L |

| м | HV2A | GND  | HV1A | HV0A | VCWA | PDM\ | VAAA            | BIAS | NC  | INP1A | INN1A | INP2A  | м |

|   | 1    | 2    | 3    | 4    | 5    | 6    | 7               | 8    | 9   | 10    | 11    | 12     |   |

#### ZHCS185A – SEPTEMBER 2011 – REVISED JANUARY 2012

| PIN | FUNCTIONS |  |

|-----|-----------|--|

| PIN NAME       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLIES       |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VAAx           | Input Logic Supply (+2.5V)                                                                                                                                                                                                                                                                                                                                                                                         |

| VDD            | +5V Driver Supply                                                                                                                                                                                                                                                                                                                                                                                                  |

| VEE            | -5V Driver Supply                                                                                                                                                                                                                                                                                                                                                                                                  |

| HV0A, HV0B     | Positive Supply of Low-voltage FET Output stage; Channel A and B                                                                                                                                                                                                                                                                                                                                                   |

| LV0A, LV0B     | Negative Supply of Low-voltage FET Output stage; Channel A and B                                                                                                                                                                                                                                                                                                                                                   |

| HV2A, HV2B     | Positive Supply of Intermediate voltage FET Output stage; this stage includes an internal de-glitcher circuit.Channel A and B                                                                                                                                                                                                                                                                                      |

| LV2A, LV2B     | Negative Supply of Intermediate voltage FET Output stage; this stage includes an internal de-glitcher circuit.Channel A and B                                                                                                                                                                                                                                                                                      |

| HV1A, HV1B     | Positive Supply of High-voltage FET Output stage; Channel A and B                                                                                                                                                                                                                                                                                                                                                  |

| LV1A, LV1B     | Negative Supply of High-voltage FET Output stage; Channel A and B                                                                                                                                                                                                                                                                                                                                                  |

| VCWA, VCWB     | Supply connections for CW FET output stage; Channel A and B                                                                                                                                                                                                                                                                                                                                                        |

| GND            | Ground connection; Driver                                                                                                                                                                                                                                                                                                                                                                                          |

| GNDCWA, GNDCWB | Ground connection for CW FET output stage of Channel A and B                                                                                                                                                                                                                                                                                                                                                       |

| BIAS           | Connect to VAA (+2.5V); used for internal biasing; high-impedance input                                                                                                                                                                                                                                                                                                                                            |

| INPUTS         |                                                                                                                                                                                                                                                                                                                                                                                                                    |

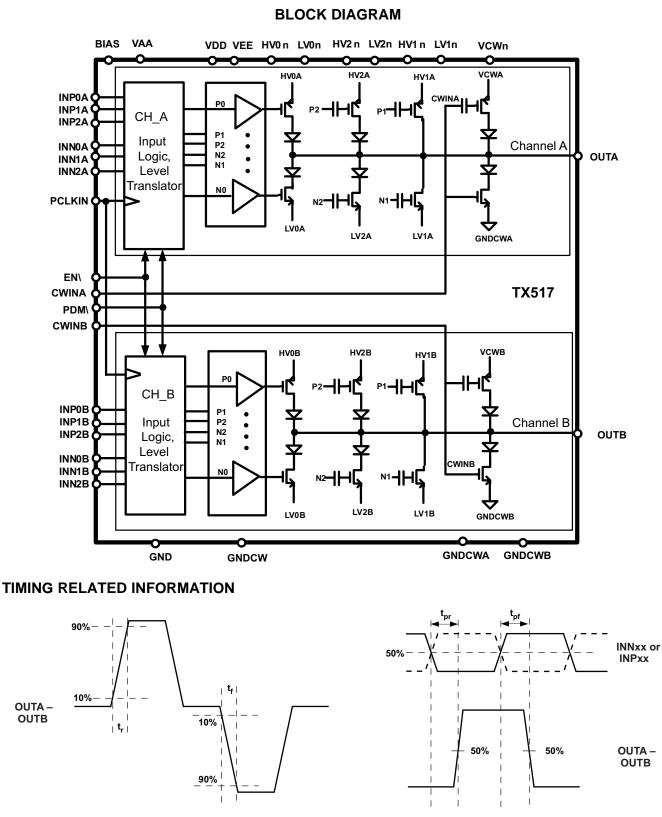

| INP0A, INP0B   | Logic input signal for the Low-voltage P-FET stage of channel A and B; Low = ON, High = OFF. Controls HV0A, HV0B. High impedance input.                                                                                                                                                                                                                                                                            |

| INNOA, INNOB   | Logic input signal for the Low-voltage N-FET stage of channel A and B; Low = OFF, High = ON. Controls LV0A, LV0B. High impedance input.                                                                                                                                                                                                                                                                            |

| INP2A, INP2B   | Logic input signal for the Intermediate voltage P-FET stage of channel A and B; Low = ON, High = OFF.<br>Controls HV2A, HV2B. High impedance input.                                                                                                                                                                                                                                                                |

| INN2A, INN2B   | Logic input signal for the Intermediate Voltage N-FET stage of channel A and B; Low = OFF, High = ON. Controls LV2A, LV2B. High impedance input.                                                                                                                                                                                                                                                                   |

| INP1A, INP1B   | Logic input signal for the High-voltage P-FET stage of channel A and B; Low = ON, High = OFF. Controls HV1A, HV1B. High impedance input.                                                                                                                                                                                                                                                                           |

| INN1A, INN1B   | Logic input signal for the High-voltage N-FET stage of channel A and B; Low = OFF, High = ON. Controls LV1A, LV1B. High impedance input.                                                                                                                                                                                                                                                                           |

| CWINA          | CW gate input signal for A output. An input '1' means that current sinks from OUTA. An input '0' means that current sources from OUTA. This pin directly accesses the output A CW FET gates.                                                                                                                                                                                                                       |

| CWINB          | CW gate input signal for B output. An input '1' means that current sinks from OUTB. An input '0' means that current sources from OUTB. This pin directly accesses the output B CW FET gates.                                                                                                                                                                                                                       |

| ĒN             | Logic Input for non-CW path; use the Enable-pin to select between input data being latched or transparent operation. Low = input data will be retimed by the internal (T&H) at the rate of the applied clock at PCLKIN. High = use this mode when operating the TX517 without a clock. When High (1) the input data will bypass the (T&H). This pin is a common control for Channel A and B. High impedance input. |

| PDM            | Power-down control input non-CW path; Low = power-down, High = normal operation. The PDM-pin controls the voltage translation circuits which draw some quiescent power. This pin is a common control for Channel A and B. High impedance input.                                                                                                                                                                    |

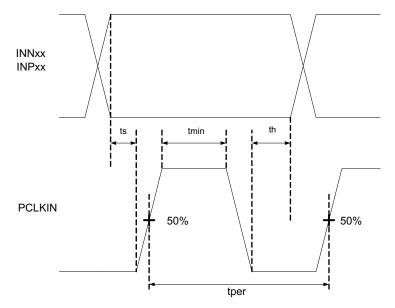

| PCLKIN         | Clock input for usage in latch (T&H) mode. When clock signal is high, the (T&H) circuit is in track mode. When clock signal is low, the (T&H) is in hold mode. This pin is a common clock input for both Channel A and B. High impedance input.                                                                                                                                                                    |

| OUTPUTS        |                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OUTA           | Output Channel A                                                                                                                                                                                                                                                                                                                                                                                                   |

| OUTB           | Output Channel B                                                                                                                                                                                                                                                                                                                                                                                                   |

ZHCS185A – SEPTEMBER 2011 – REVISED JANUARY 2012

# Instruments

EXAS

www.ti.com.cn

### **ABSOLUTE MAXIMUM RATINGS**

Voltages referenced to Ground potential (GND = 0V); over operating free-air temperature (unless otherwise noted) <sup>(1)</sup>

|                 |                                                                                          | VALUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | UNIT |

|-----------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V               | High-Voltage, Positive Supply HV1,2 referred to OUTA/B, see also Max. delta voltage      | -0.3 to +80                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V    |

| V <sub>DS</sub> | High-Voltage, Positive Supply HV0 referred to OUTA/B, see also Max. delta voltage        | -0.3 to +6                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V    |

|                 | High-Voltage VCWA/B supply referred to GNDCWA/B                                          | -0.3 to +16                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V    |

| \/              | High-Voltage, Negative Supply LV1,2 referred to OUTA/B, see also Max. delta voltage      | -40 to +0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V    |

| V <sub>DS</sub> | High-Voltage, Negative Supply LV0 referred to OUTA/B, see also Max. delta voltage        | -6 to +0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V    |

|                 | Max. delta voltage: HV1-LV1 and HV2 – LV2                                                | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

|                 | Max. delta voltage: HV0 – LV0                                                            | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V    |

| VDD             | Driver Supply, positive                                                                  | -0.3 to +6                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V    |

| VEE             | Driver Supply, negative                                                                  | -6 to +0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V    |

| VAA             | Logic Supply Voltage                                                                     | -0.3 to +6                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V    |

|                 | Logic Inputs (INPx, INNx, EN, PDM, PCLKIN, U)                                            | -0.3 to +6                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V    |

|                 | CW inputs (CWINA, CWINB)                                                                 | -0.3 to +11                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V    |

|                 | Peak Solder Temperature <sup>(2)</sup>                                                   | Supply HV0 referred to OUTA/B, see also Max. delta voltage-0.3 to +6supply referred to GNDCWA/B-0.3 to +16Supply LV1,2 referred to OUTA/B, see also Max. delta voltage-40 to +0.3Supply LV0 referred to OUTA/B, see also Max. delta voltage-6 to +0.31-LV1 and HV2 - LV21100 - LV012-0.3 to +6-6 to +0.3-0.3 to +6-0.3 to +6-0.3 to +6-0.3 to +6-0.3 to +6-0.3 to +6VINB)-0.3 to +11ure (2)260perature, any condition (3)150perature, continuous operation, long term reliability (4)125 | °C   |

| TJ              | Maximum junction temperature, any condition <sup>(3)</sup>                               | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | °C   |

| TJ              | Maximum junction temperature, continuous operation, long term reliability <sup>(4)</sup> | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | °C   |

| Tstg            | Storage temperature range                                                                | -65 to 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | °C   |

|                 | НВМ                                                                                      | 500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

| ESD ratings     | CDM                                                                                      | 750                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

|                 | MM                                                                                       | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V    |

Stresses above those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may degrade device reliability.

Device according to the device at these or any other conditions for extended periods may degrade device reliability.

(2) Device complies with JSTD-020D.

(3) The absolute maximum junction temperature under any condition is limited by the constraints of the silicon process.

(4) The absolute maximum junction temperature for continuous operation is limited by the package constraints. Operation above this temperature may result in reduced reliability and/or lifetime of the device.

### THERMAL INFORMATION

|                                          | THERMAL METRIC <sup>(1)</sup>              | TX517                                                                                       |       |

|------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------|-------|

|                                          |                                            | BGA (144) (ZCQ) PINS           28           3.8           11.3           0.2           3.57 | UNITS |

| θ <sub>JA</sub>                          | Junction-to-ambient thermal resistance     | 28                                                                                          |       |

| θ <sub>JCtop</sub>                       | Junction-to-case (top) thermal resistance  | 3.8                                                                                         | °C/W  |

| $\theta_{JB}$                            | Junction-to-board thermal resistance       | 11.3                                                                                        | C/W   |

| Ψυτ                                      | Junction-to-top characterization parameter | 0.2                                                                                         |       |

| Power                                    | $TA = 25^{\circ}C$                         | 3.57                                                                                        |       |

| Rating <sup>(2)(3)</sup><br>(TJ = 125°C) | TA = 85°C                                  | 1.47                                                                                        | W     |

(1) 有关传统和新的热度量的更多信息,请参阅 /C 封装热度量 应用报告 SPRA953。

(2) This data was taken with the JEDEC High-K test PCB.

Power rating is determined with a junction temperature of 125°C. This is the point where distortion starts to substantially increase and long-term reliability starts to be reduced. Thermal management of the final PCB should strive to keep the junction temperature at or below 125°C for best performance and reliability.

ZHCS185A-SEPTEMBER 2011-REVISED JANUARY 2012

#### www.ti.com.cn

# **RECOMMENDED OPERATING CONDITIONS**

|                                                 | MIN           | ТҮР   | MAX                                         | UNIT |

|-------------------------------------------------|---------------|-------|---------------------------------------------|------|

| VAA                                             | 2.38          | 2.5   | 3.3                                         | V    |

| VDD                                             | 4.75          | 5.0   | 5.25                                        | V    |

| VEE                                             | -5.25         | -5.0  | -4.75                                       | V    |

| HV0A, HV0B                                      | 0             | 1.9   | 5                                           | V    |

| LV0A, LV0B                                      | -5            | -1.9  | 0                                           | V    |

| HV2A, HV2B                                      | 0             | 32    | 70                                          | V    |

| LV2A, LV2B                                      | -30           | -11.9 | 0                                           | V    |

| HV1A, HV1B                                      | >HV0 and >HV2 | 61    | 70                                          | V    |

| LV1A, LV1B                                      | -30           | -20.9 | <lv0 <lv2<="" and="" td=""><td>V</td></lv0> | V    |

| VCWA, VCWB                                      | 0             | 11    | 15                                          | V    |

| Maximum DELTA between HV1 to LV1 and HV2 to LV2 |               |       | 100                                         | V    |

| INNx, INPx, EN, PDM, PCLKIN, U                  | 0             |       | VAA                                         | V    |

| INCWA, INCWB                                    | 0             | 5     | 10                                          | V    |

| INNxx, INPxx input sample rate                  | 1             |       | 100                                         | Msps |

| INNxx, INPXX input unit interval                | 10            |       | 1000                                        | ns   |

| PCLKIN input frequency                          | 1             |       | 100                                         | MHz  |

| Ambient Temperature, T <sub>A</sub>             | 0             |       | 85                                          | °C   |

ZHCS185A – SEPTEMBER 2011 – REVISED JANUARY 2012

# **ELECTRICAL CHARACTERISTICS**

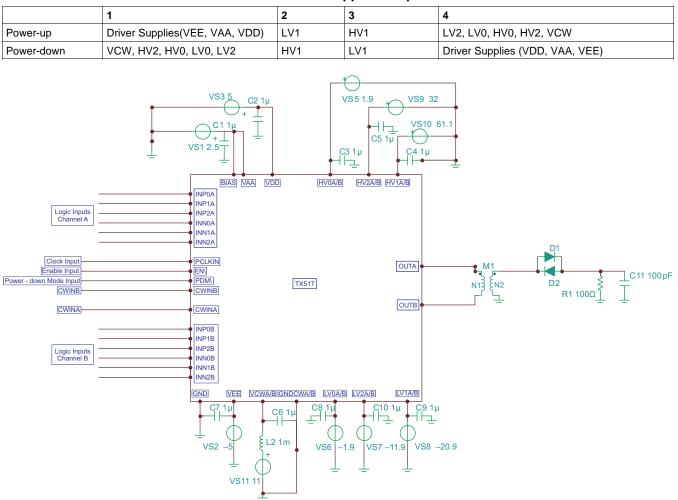

All Specifications at:  $T_A = 0$  to 85°C, VAA = 2.5V, VDD = 5V, VEE = -5V, HV0 = 1.9V, LV0= -1.9V, HV2 = 32V, LV2=-11.9V, HV1 = +61.1V, LV1= -20.9V, VCW =11V, R<sub>L</sub>=100  $\Omega$  to GND for OUTA, R<sub>L</sub>=100  $\Omega$  to GND for OUTB, unless otherwise noted. The parameter results are applicable to both OUTA and OUTB, and they are measured using Non-Latch Mode unless otherwise noted.

|                                 | PARAMETER                                                                 | CONDITIONS                                                                                   | MIN  | TYP   | MAX  | UNITS | TEST LEVEL <sup>(1</sup> |

|---------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|-------|------|-------|--------------------------|

| HV0/L                           | V0 SIGNAL PATH – DC PERFORMANCE                                           |                                                                                              |      |       |      |       |                          |

|                                 | P-CHANNEL                                                                 |                                                                                              |      |       |      |       |                          |

|                                 | Effective resistance, RDSon + Rdiode                                      | HV0 = 2 V, OUTX = -750 mV to -1.25 V                                                         | 6.5  | 9.5   | 13   | Ω     | А                        |

|                                 | Effective resistance variation                                            | Max output power to Min output power, load = 100 $\Omega$ to 0 V                             |      |       | 12%  |       | С                        |

|                                 | Output saturation current                                                 | $R_L = 5 \Omega$ to $-30 V$                                                                  | -3.1 | -1.3  | -1   | А     | А                        |

|                                 | Output voltage                                                            |                                                                                              |      | 1.0   |      | V     | С                        |

|                                 | N-CHANNEL                                                                 |                                                                                              |      |       |      |       |                          |

|                                 | Effective resistance, RDSon + Rdiode                                      | LV0 = -2V, OUTX = 750 mV to 1.25 V                                                           | 2.5  | 5     | 8.5  | Ω     | А                        |

|                                 | Effective Resistance Variation                                            | Max output power to Min output power, Load = 100 $\Omega$ to 0 V                             |      |       | 5    | %     | С                        |

|                                 | Output saturation current                                                 | $R_L = 5 \Omega$ to +30 V                                                                    | 1.4  | 1.8   | 3.1  | А     | А                        |

|                                 | Output voltage                                                            |                                                                                              |      | -1.2  |      | V     | С                        |

| IV0/L                           | V0 SIGNAL PATH – AC PERFORMANCE                                           |                                                                                              |      |       |      |       |                          |

|                                 | Single-tone output frequency                                              |                                                                                              | 1    |       | 100  | Msps  | В                        |

|                                 | 2 <sup>nd</sup> Order harmonic distortion (when using transformer bridge) | f = 5.0 MHz square wave, measured using transformer at secondary coil with RL = 100 $\Omega$ |      | 35    |      | dBc   | С                        |

| r                               | Output rise time                                                          | 10% to 90% of 0 V to +Vout<br>Figure 8                                                       |      | 4.5   |      | ns    | С                        |

|                                 | Output fall time                                                          | 10% to 90% of 0 V to -Vout<br>Figure 8                                                       |      | 1     |      | ns    | С                        |

| <sub>or</sub> , t <sub>pf</sub> | Propagation Delay                                                         | Input 50% to Output 50%<br>Figure 8                                                          |      | 30    |      | ns    | В                        |

| IV2/L                           | V2 SIGNAL PATH – DC PERFORMANCE                                           |                                                                                              |      |       |      |       |                          |

|                                 | P-CHANNEL                                                                 |                                                                                              |      |       |      |       |                          |

|                                 | Effective resistance, RDSon + Rdiode                                      | HV2 = 30 V to HV2 = 20 V                                                                     | 4.5  | 9     | 12.5 | Ω     | А                        |

|                                 | Effective resistance variation                                            | Max output power to Min output power, load = 100 $\Omega$ to 0 V                             |      |       | 12%  |       | С                        |

|                                 | Output saturation current                                                 | HV2 = 60 V; $R_L$ = 5 $\Omega$ to GND                                                        | -4.1 | -2.3  | -1.8 | А     | А                        |

|                                 | Output voltage                                                            |                                                                                              |      | 28.5  |      | V     | С                        |

|                                 | N-CHANNEL                                                                 |                                                                                              |      |       |      |       |                          |

|                                 | Effective resistance, RDSon + Rdiode                                      | LV2 = -10 V to $LV2 = -12 V$                                                                 | 1.5  | 4.5   | 7.5  | Ω     | А                        |

|                                 | Effective resistance variation                                            | Max output power to Min output power, load = 100 $\Omega$ to 0 V                             |      |       | 4%   |       | С                        |

|                                 | Output saturation current                                                 | $LV2 = -60 V; R_L = 5 \Omega \text{ to GND}$                                                 | 2.4  | 3.0   | 5.0  | А     | А                        |

|                                 | Output Voltage                                                            |                                                                                              |      | -10.5 |      | V     | С                        |

| IV2/L                           | V2 SIGNAL PATH – AC PERFORMANCE                                           |                                                                                              |      |       |      |       |                          |

|                                 | Single-tone Output Frequency                                              |                                                                                              | 1    |       | 100  | Msps  | В                        |

|                                 | 2 <sup>nd</sup> Order harmonic distortion when using transformer bridge   | f = 5.0 MHz square wave, measured using transformer at secondary coil with RL = 100 $\Omega$ |      | 50    |      | dBc   | С                        |

| r                               | Output rise time                                                          | 10% to 90% of 0 V to +Vout<br>Figure 8                                                       |      | 7.5   |      | ns    | С                        |

| f                               | Output fall time                                                          | 10% to 90% of 0 V to -Vout<br>Figure 8                                                       |      | 3     |      | ns    | С                        |

| <sub>pr</sub> , t <sub>pf</sub> | Propagation delay                                                         | Input 50% to Output 50%<br>Figure 8                                                          |      | 25    |      | ns    | В                        |

(1) Test levels: (A) 100% tested at 25°C. Over temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

TX517

www.ti.com.cn

### **ELECTRICAL CHARACTERISTICS**

All Specifications at:  $T_A = 0$  to 85°C, VAA = 2.5V, VDD = 5V, VEE = -5V, HV0 = 1.9V, LV0 = -1.9V, HV2 = 32V, LV2 = -11.9V, HV1 = +61.1V, LV1 = -20.9V, VCW = 11V, R<sub>L</sub>= 100 $\Omega$  to GND for OUTA, R<sub>L</sub>= 100 $\Omega$  to GND for OUTB, unless otherwise noted. The parameter results are applicable to both OUTA and OUTB, and they are measured using Non-Latch Mode unless otherwise noted.

| PARAMETER                                                                 | CONDITIONS                                                                                     | MIN  | TYP  | MAX  | UNITS | TEST LEVEL <sup>(1)</sup> |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|-------|---------------------------|

| HV1/LV1 SIGNAL PATH – DC PERFORMANCE                                      | · · · · · ·                                                                                    |      |      |      |       |                           |

| P-CHANNEL                                                                 |                                                                                                |      |      |      |       |                           |

| Effective resistance, RDSon + Rdiode                                      | HV1 = 60 V to HV1 = 50 V                                                                       | 2.5  | 7    | 12.5 | Ω     | А                         |

| Effective resistance variation                                            | Max output power to Min output power load = $100 \Omega$ to GND                                |      |      | 11%  |       | С                         |

| Output saturation current                                                 | HV1 = 60 V; $R_L = 5 \Omega$ to GND                                                            | -4.1 | -2.5 | -2   | А     | А                         |

| Output voltage                                                            |                                                                                                |      | 58   |      | V     | С                         |

| N-CHANNEL                                                                 |                                                                                                |      |      |      |       |                           |

| Effective resistance, RDSon + Rdiode                                      | LV1 = -20 V to -10 V                                                                           | 1    | 2    | 4.5  | Ω     | А                         |

| Effective resistance variation                                            | Max output power to Min output power load = 100 $\Omega$ to 0 V                                |      |      | 3%   |       | С                         |

| Output saturation current                                                 | LV1 = $-60$ V; R <sub>L</sub> = 5 $\Omega$ to GND                                              | 2.9  | 3.4  | 4.1  | А     | А                         |

| Output voltage                                                            |                                                                                                |      | -20  |      | V     | С                         |

| HV1/LV1 SIGNAL PATH – AC PERFORMANCE                                      |                                                                                                |      |      |      |       |                           |

| Single-tone output frequency                                              |                                                                                                | 1    |      | 100  | Msps  | В                         |

| 2 <sup>nd</sup> Order harmonic distortion (when using transformer bridge) | $f$ = 5.0 MHz square wave, measured using transformer at secondary coil with RL = 100 $\Omega$ |      | 60   |      | dBc   | С                         |

| t <sub>r</sub> Output rise time                                           | 10% to 90% of 0 V to +Vout<br>Figure 8                                                         |      | 6.5  |      | ns    | С                         |

| t <sub>r</sub> Output fall time                                           | 10% to 90% of 0 V to -Vout<br>Figure 8                                                         |      | 3    |      | ns    | С                         |

| t <sub>pr</sub> , t <sub>pf</sub> Propagation Delay                       | Input 50% to Output 50%<br>Figure 8                                                            |      | 25   |      | ns    | В                         |

(1) Test levels: (A) 100% tested at 25°C. Over temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

### **ELECTRICAL CHARACTERISTICS**

All Specifications at:  $T_A = 0$  to 85°C, VAA = 2.5V, VDD = 5V, VEE = -5V, HV0 = 1.9V, LV0 = -1.9V, HV2 = 32V, LV2 = -11.9V, HV1 = +61.1V, LV1 = -20.9V, VCW = 11V, R<sub>L</sub>= 100  $\Omega$  to GND for OUTA, R<sub>L</sub>= 100 $\Omega$  to GND for OUTB, unless otherwise noted. The parameter results are applicable to both OUTA and OUTB, and they are measured using Non-Latch Mode unless otherwise noted.

| PARAMETER                            | CONDITIONS                                                       | MIN   | TYP   | MAX   | UNITS | TEST LEVEL <sup>(1)</sup> |

|--------------------------------------|------------------------------------------------------------------|-------|-------|-------|-------|---------------------------|

| CW SIGNAL PATH – DC PERFORMANCE      |                                                                  |       |       |       |       |                           |

| P-CHANNEL                            |                                                                  |       |       |       |       |                           |

| Effective resistance, RDSon + Rdiode | VCW = 4.5 Vto 5.5 V                                              | 9     | 21    | 31    | Ω     | A                         |

| Effective resistance variation       | Max output power to Min output power, load = 100 $\Omega$ to 0 V |       |       | 30%   |       | с                         |

| Output saturation current            | $R_L = 5 \Omega$ to $-20 V$                                      | -0.16 | -0.12 | -0.06 | А     | A                         |

| Output voltage                       |                                                                  |       | 8     |       | V     | С                         |

| N-CHANNEL                            |                                                                  |       |       |       |       |                           |

| Effective resistance, RDSon + Rdiode | OUTX = 1 V to 2 V                                                | 9     | 14    | 18    | Ω     | A                         |

| Effective resistance variation       | Max output power to Min output power, load = 100 $\Omega$ to 0 V |       |       | 10%   |       | с                         |

| Output saturation current            | $R_L = 5 \Omega$ to 20 V                                         | 0.29  | 0.35  | 0.44  | А     | A                         |

| Output voltage                       |                                                                  |       | 30    |       | mV    | С                         |

Test levels: (A) 100% tested at 25°C. Over temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

ZHCS185A – SEPTEMBER 2011 – REVISED JANUARY 2012

www.ti.com.cn

# **ELECTRICAL CHARACTERISTICS (continued)**

All Specifications at:  $T_A = 0$  to 85°C, VAA = 2.5V, VDD = 5V, VEE = -5V, HV0 = 1.9V, LV0 = -1.9V, HV2 = 32V, LV2 = -11.9V, HV1 = +61.1V, LV1 = -20.9V, VCW = 11V, R<sub>L</sub>= 100  $\Omega$  to GND for OUTA, R<sub>L</sub>= 100 $\Omega$  to GND for OUTB, unless otherwise noted. The parameter results are applicable to both OUTA and OUTB, and they are measured using Non-Latch Mode unless otherwise noted.

|                                   | PARAMETER                                            | CONDITIONS                                                                          | MIN      | TYP   | MAX  | UNITS | TEST LEVEL <sup>(1)</sup> |

|-----------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------|----------|-------|------|-------|---------------------------|

| cw s                              | SIGNAL PATH – AC PERFORMANCE <sup>(2)</sup>          |                                                                                     |          |       |      |       |                           |

|                                   | Single-tone output frequency                         |                                                                                     | 0.5      |       | 10   | MHz   | В                         |

|                                   |                                                      | $f$ = 1MHz, measured using transformer at secondary coil with $R_L$ = 100 $\Omega$  |          | 47    |      | dBc   | С                         |

|                                   | 2 <sup>nd</sup> Order harmonic distortion            | $f$ = 5 MHz, measured using transformer at secondary coil with $R_L$ = 100 $\Omega$ |          | 33    |      | dBc   | С                         |

|                                   | Slew Rate + (Positive Edge)                          | 20% to 80% of Voutpp, measured using transformer at                                 |          | 0.6   |      | V/ns  | С                         |

|                                   | Slew Rate – (Negative Edge)                          | secondary coil with RL = 100 $\Omega$                                               |          | 0.45  |      | V/ns  | С                         |

| tr                                | Output rise time                                     | 10% to 90% of 0 V to +Vout<br>Figure 8                                              |          | 30    |      | ns    | С                         |

| t <sub>f</sub>                    | Output fall time                                     | 10% to 90% of 0 V to -Vout<br>Figure 8                                              |          | 10    |      | ns    | С                         |

| t <sub>pr</sub> , t <sub>pf</sub> | Propagation Delay                                    | Input 50% to Output 50%<br>Figure 8                                                 |          | 25    |      | ns    | В                         |

|                                   | AC-coupled gate drive time constant for<br>P-CHANNEL |                                                                                     | 10       | 20    | 30   | μs    | С                         |

| CW I                              | NPUT CHARACTERISTIC                                  |                                                                                     |          |       |      |       | *                         |

|                                   | High input voltage                                   |                                                                                     | 1.05     |       |      | V     | В                         |

|                                   | Low input voltage                                    |                                                                                     |          |       | 0.35 | V     | В                         |

|                                   | Low input current                                    | CWINX=0V                                                                            |          | 0     | 1    | μΑ    | В                         |

|                                   | High input current                                   | CWINX=5.0V                                                                          |          | 25    | 40   | μΑ    | В                         |

|                                   | Input Gate Charge                                    | CWINX = 0 V to 5.0 V or<br>5.0 V to 0 V                                             |          | 550   |      | рС    | С                         |

| LOG                               | IC CHARACTERISTICS – INNXX, INPXX, EN                | PDM PCLKIN pins                                                                     |          |       |      |       | 1                         |

|                                   |                                                      | INNxx, INPxx, PCLKIN @ 10 MHz                                                       |          | 6     |      |       |                           |

|                                   | Input capacitance                                    | EN\ @ 10 MHz                                                                        |          | 9     |      | pF    | С                         |

|                                   |                                                      | PDM\ @ 10 MHz                                                                       |          | 4     |      |       |                           |

|                                   | Logic high input voltage                             | VAA=2.375V to 3.6V                                                                  | 0.55*VAA |       | VAA  | V     | В                         |

|                                   | Logic low input voltage                              | VAA=2.375V to 3.6V                                                                  | 0        |       | 0.8  | V     | В                         |

|                                   | Logic low input current                              |                                                                                     |          | 0.2   | 10   | μA    | В                         |

|                                   | Logic high input current                             |                                                                                     |          | 0.2   | 10   | μΑ    | В                         |

|                                   | Minimum clock period, tper                           | Figure 9, PCLKIN                                                                    | 10       |       |      | ns    | В                         |

|                                   | Minimum clock high time, tmin                        | Figure 9, PCLKIN                                                                    | 2.0      |       |      | ns    | В                         |

| t <sub>s</sub>                    | Setup time                                           | Figure 9, PCLKIN, INNxx, INPxx                                                      | 0        |       |      | ns    | В                         |

| t <sub>h</sub>                    | Hold time                                            | Figure 9, PCLKIN, INNxx, INPxx                                                      | 1.5      |       |      | ns    | В                         |

| OUT                               | PUT CHARACTERISTIC                                   |                                                                                     |          |       |      |       |                           |

|                                   | Output resistance                                    | Power Down Mode (Hi-Z Output) VTEST = 20 V                                          |          | 1     |      | GΩ    | С                         |

|                                   | Output capacitance                                   | Power Down Mode (Hi-Z Output)<br>@1 to 100 MHZ                                      |          | 165   |      | pF    | С                         |

|                                   | Leakage current                                      | Power Down Mode (Hi-Z Output) VTEST = 0V                                            |          | 0.001 | 10   | μA    | A                         |

| INTE                              | RNAL GATE CHARGE CHARACTERISTICS                     |                                                                                     |          |       |      |       |                           |

|                                   |                                                      | HV0/LV0 internal FET gates driven from VEE to VDD or VDD to VEE                     |          | 3.5   |      | nC    | С                         |

|                                   | Input gate charge <sup>(3)</sup>                     | HV1/LV1 internal FET gates driven from VEE to VDD or VDD to VEE                     |          | 4.6   |      | nC    | С                         |

|                                   |                                                      | HV2/LV2 internal FET gates driven rom VEE to VDD or VDD to VEE                      |          | 7     |      | nC    | с                         |

(1) Test levels: (A) 100% tested at 25°C. Over temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

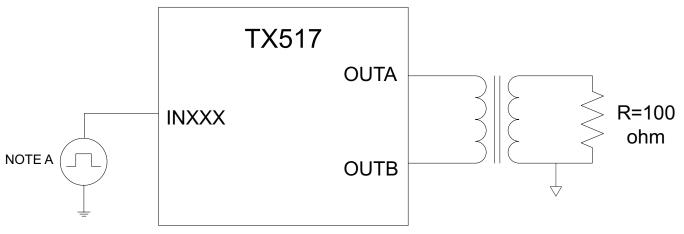

(2) TX517 CW outputs are complimentary. Thus a transformer is needed to enable CW output.

(3) Input gate charge is the amount of charge to change the internal FET gates of a given output from either a low to a high state or from a high to a low state. Each gate charge value applies to both the P and N type FET for the given output. These values can be used to estimate the amount of dynamic current that needs to be provided to the VDD and VEE power supplies in order to switch the internal FET's at a given sampling rate.

TX517

www.ti.com.cn

### **ELECTRICAL CHARACTERISTICS**

All Specifications at:  $T_A = 0$  to 85°C, VAA = 2.5V, VDD = 5V, VEE = -5V, HV0 = 1.9V, LV0 = -1.9V, HV2 = 32V, LV2 = -11.9V, HV1 = +61.1V, LV1 = -20.9V, VCW = 11V, R<sub>L</sub>= 100 $\Omega$  to GND for OUTA, R<sub>L</sub>= 100 $\Omega$  to GND for OUTB, unless otherwise noted. The parameter results are applicable to both OUTA and OUTB, and they are measured using Non-Latch Mode unless otherwise noted.

| PARAMETER                                                         | CONDITIONS                                                                                                                                                         | MIN     | ТҮР  | МАХ   | UNITS | TEST<br>LEVEL <sup>(1)</sup> |   |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-------|------------------------------|---|

| POWER SUPPLY                                                      |                                                                                                                                                                    |         |      |       |       |                              |   |

| Total Quiescent Current (PW Mode) Power supply VDD                | INPxx = 1, INNxx = 0, PCLKIN= 0 or 1                                                                                                                               |         |      | 13    | 15    | mA                           | А |

| Total Quiescent Current (PW Mode) Power supply VEE                | INPxx = 1, INNxx = 0, PCLKIN= 0 or 1                                                                                                                               | -10     | -8   |       | mA    | A                            |   |

| Total Quiescent Current (PW Mode) Power supply VAA                | INPxx = 1, INNxx = 0, PCLKIN= 0 or 1                                                                                                                               | -3      | -2   |       | mA    | А                            |   |

|                                                                   | Input pattern = 10 cycle square wave, 5%                                                                                                                           | HV0/LV0 |      | 17    | 23    |                              |   |

| Dynamic Current Consumption (PW Mode)<br>Power supply VDD         | duty cycle at 10 Msps (5 MHz) on noted signal path. Load = transformer and 100                                                                                     | HV1/LV1 |      | 18    | 23    | mA                           | В |

|                                                                   | ohm differential load, see Figure 10.                                                                                                                              | HV2/LV2 |      | 20.5  | 23    |                              |   |

|                                                                   | Input pattern = 10 cycle square wave, 5%                                                                                                                           | HV0/LV0 | -15  | -10   |       |                              |   |

| Dynamic Current Consumption (PW Mode)<br>Power supply VEE         | duty cycle at 10 Msps (5 MHz) on noted signal path. Load = transformer and 100                                                                                     | HV1/LV1 | -15  | -10.5 |       | mA                           | В |

| · · · · · · · · · · · · · · · · · · ·                             | ohm differential load, see Figure 10.                                                                                                                              | HV2/LV2 | -15  | -12.5 |       |                              |   |

|                                                                   | Input pattern = 10 cycle square wave, 5%                                                                                                                           | HV0/LV0 | -4   | -2.3  |       |                              |   |

| Dynamic Current Consumption (PW Mode)<br>Power supply VAA         | duty cycle at 10 Msps (5 MHz) on noted signal path. Load = transformer and 100                                                                                     | HV1/LV1 | -4   | -2.5  |       | mA                           | В |

|                                                                   | ohm differential load, see Figure 10.                                                                                                                              | HV2/LV2 | -4   | -2.5  |       |                              |   |

| Dynamic Current Consumption (PW Mode)<br>Power supply HV0         | Input pattern = 10 cycle square wave, 5%<br>(5 MHz) on noted signal path. Load = trans<br>differential load, see Figure 10.                                        |         |      | 2     | 4     | mA                           | В |

| Dynamic Current Consumption (PW Mode)<br>Power supply LV0         | Input pattern = 10 cycle square wave, 5%<br>(5 MHz) on noted signal path. Load = trans<br>differential load, see Figure 10.                                        |         | -3.5 | -2    |       | mA                           | В |

| Dynamic Current Consumption (PW Mode)<br>Power supply HV1         | Input pattern = 10 cycle square wave, 5%<br>(5 MHz) on noted signal path. Load = trans<br>differential load, see Figure 10.                                        |         | 41   | 60    | mA    | В                            |   |

| Dynamic Current Consumption (PW Mode)<br>Power supply LV1         | Input pattern = 10 cycle square wave, 5%<br>(5 MHz) on noted signal path. Load = trans<br>differential load, see Figure 10.                                        |         | -55  | -41   |       | mA                           | В |

| Dynamic Current Consumption (PW Mode)<br>Power supply HV2         | Input pattern = 10 cycle square wave, 5%<br>Msps(5 MHz) on noted signal path. Load =<br>ohm differential load, see Figure 10.                                      |         |      | 22    | 60    | mA                           | В |

| Dynamic Current Consumption (PW Mode)<br>Power supply LV2         | Input pattern = 10 cycle square wave, 5%<br>(5 MHz) on noted signal path. Load = trans<br>differential load, see Figure 10.                                        |         | -35  | -22   |       | mA                           | В |

|                                                                   | Input pattern = 10 cycle square wave, 5%                                                                                                                           | HV0/LV0 |      | 0.15  | 0.25  |                              |   |

| Total Power Dissipation for device only (PW Mode)                 | duty cycle at 10 Msps on noted signal path. Load = transformer and 100 ohm                                                                                         | HV1/LV1 |      | 1.1   | 1.7   | W                            | В |

|                                                                   | differential load, see Figure 10.                                                                                                                                  |         | 0.6  | 0.8   |       |                              |   |

| Dynamic Current Consumption (CW Mode)<br>Power supply VCWA + VCWB | Input pattern = 10 cycle square wave, 100<br>Msps on CW signal path. Load = transform<br>differential load, see Figure 10.<br>EN\ = 0 or 1, PCLKIN = 0 or 1        |         | 62   | 100   | mA    | В                            |   |

| Total Power Dissipation for device only (CW Mode)                 | Input pattern = 10 cycle square wave, 100<br>Msps (5 MHz) on noted signal path. Load<br>100 ohm differential load, see Figure 10.<br>EN\ = 0 or 1, PCLKIN = 0 or 1 |         | 310  | 400   | mW    | В                            |   |

| Supply (HVx, LVx) Slew Rate Limit                                 |                                                                                                                                                                    |         |      |       | 10    | V/ms                         | В |

| POWER-DOWN CHARACTERISTIC                                         |                                                                                                                                                                    |         |      |       |       |                              |   |

| Power-Down Dissipation                                            | Power Down Mode (Hi-Z Output)<br>PDM\= 0, INPxx = 1, INNxx = 0<br>PCLKIN = 0 or 1                                                                                  |         |      | 3     | 15    | mW                           | А |

(1) Test levels: (A) 100% tested at 25°C. Over temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

# ELECTRICAL CHARACTERISTICS (any level to any level transitions – 17 level output, 289 unique transitions<sup>(1)</sup>)

All Specifications at:  $T_A = 0^{\circ}C$  to 85°C, VAA = 2.5V, VDD = 5V, VEE = -5V, HV0 = 1.9V, LV0= -1.9V, HV2 = 32V, LV2 = -11.9V, HV1 = +61.1V, LV1 = -20.9V, VCW = 11V, R<sub>L</sub>= 100  $\Omega$  to GND for OUTA, R<sub>L</sub>=100 $\Omega$  to GND for OUTB, unless otherwise noted.

| PARAMETER                                                     | CONDITIONS                  | MIN TYP MAX                           | UNITS  | TEST<br>LEVEL <sup>(2)</sup> |

|---------------------------------------------------------------|-----------------------------|---------------------------------------|--------|------------------------------|

| POWER UP/DOWN TIMING                                          |                             | · · · · · · · · · · · · · · · · · · · |        |                              |

| Power down time                                               |                             | 100                                   | ns     | С                            |

| Power up time                                                 |                             | 100                                   | ns     | С                            |

| HVX/LVX SIGNAL PATH – AC PERFORMANCE                          |                             |                                       |        |                              |

| Mean normalized output rise time                              | 10% to 90% of 0 to 1, 20MHz | 5                                     | ns     | С                            |

| Mean delay (relative to clock edge of 1 <sup>st</sup> sample) | 0-20 MHz                    | 23                                    | ns     | С                            |

| Delay standard deviation                                      | 0-20 MHz                    | 1.2                                   | ns     | С                            |

| Phase standard deviation                                      | 5 MHz                       | 0.01                                  | cycles | С                            |

| Phase standard deviation                                      | 20 MHz                      | 0.03                                  | cycles | С                            |

| Cain standard deviation                                       | 5 MHz                       | 4                                     | %      | С                            |

| Gain standard deviation                                       | 20 MHz                      | 8                                     | %      | С                            |

(1) These parameters are measured on the differential output starting from 1 of 17 possible states to every other possible state. Therefore, 17X17 = 289 unique transitions.

(2) Test levels: (A) 100% tested at 25°C. Over temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

#### ZHCS185A – SEPTEMBER 2011 – REVISED JANUARY 2012

#### TYPICAL CHARACTERISTICS

All Specifications at:  $T_A = 25^{\circ}$ C, VAA = +2.5V, VDD = +5V. VEE = -5V, HV0 = 1.9V, LV0 = -1.9V, HV2 = 32V, LV2 = -11.9V, HV1 = +61.1V, LV1 = -20.9V, VCW = 11V, R<sub>L</sub> = 100 $\Omega$  to GND for OUTA, R<sub>L</sub> = 100 $\Omega$  to GND for OUTB, unless otherwise noted.

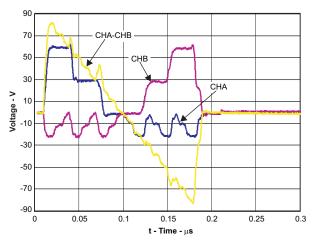

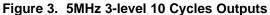

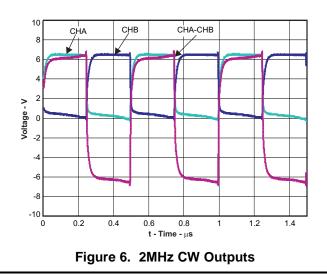

Figure 1. 17-level Outputs with 10ns Pulse Width (100MSPS)

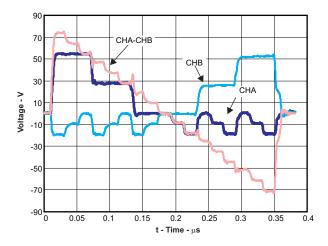

Figure 2. 17-level Outputs with 20ns Pulse Width (50MSPS)

TX517

ZHCS185A-SEPTEMBER 2011-REVISED JANUARY 2012

www.ti.com.cn

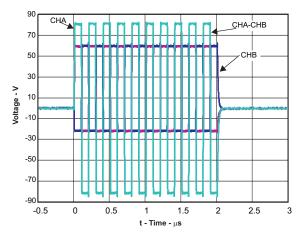

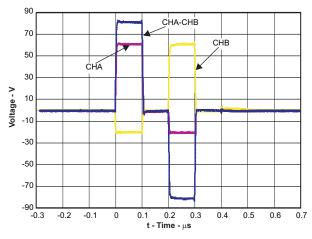

#### **TYPICAL CHARACTERISTICS (continued)**