ZHCS254-JUNE 2011

# **1.2V** 至 **3.6V**、**12** 位、纳瓦级功率、四线式

微型触摸屏控制器,具有 SPI™

查询样品: TSC2008-Q1

## 特性

- 符合汽车应用要求

- 四线式触摸屏接口

- 单 1.2V 至 3.6V 电源/基准

- 比例式转换

- 有效吞吐速率:

- 高达 20kHz(8位)或 10kHz(12位)

- 通过预处理减少总线活动

- 高速 SPI(高达 25MHz)

- 基于简单命令的用户接口:

- TSC2046 兼容型

- 8 位或 12 位分辨率

- 片上温度测量

- 触压测量

- 数字缓冲 PENIRQ

- 片上、可编程 **PENIRQ** 上拉

- 自动断电控制

- 低功耗(12位、8.2kHz均衡速率):

- 30.4µA,在1.2V、f<sub>SCLK</sub> = 5MHz

- 35.5µA,在 1.8V、f<sub>SCLK</sub> = 10MHz

- 44.6µA,在 2.7V、f<sub>SCLK</sub> = 10MHz

- 上电、软件、和 SureSet™ 复位

- 增强型 ESD 保护

- ±8kV HBM

- ±1kV CDM

- ±25kV 空气间隙放电

- ±15kV 接触放电

- 闭锁电流超过 100mA,符合 JESD78 Class I 标 ٠ 准

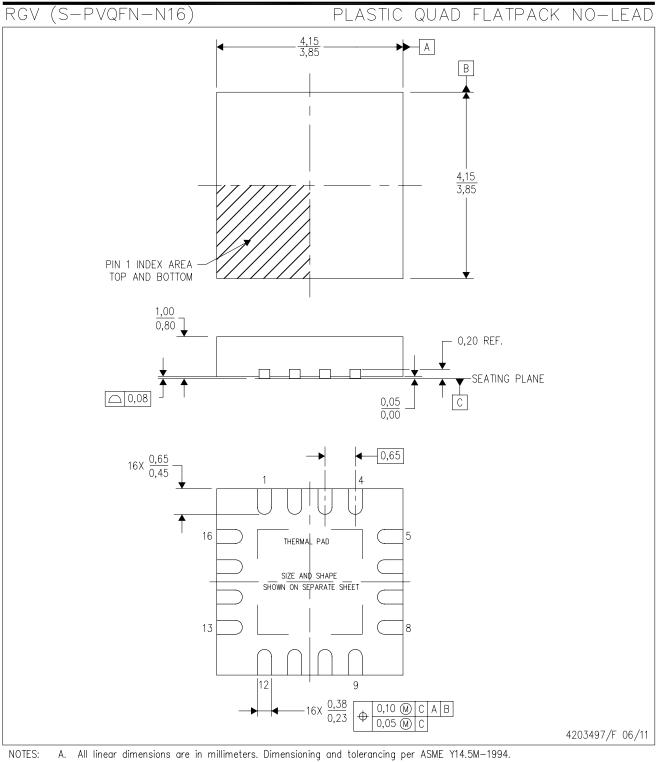

- 4 x 4 QFN-16 封装

美国专利号: 6,246,394; 其它专利正在申请 应用

多屏触摸控制系统

## 说明

TSC2008-Q1 是一款极低功耗的触摸屏控制器,专为基于高级低电压处理器的功耗敏感型手持式应用而设计。 该 器件的工作电源电压低至 1.2 V,可采用单体电池供电。 TSC2008-Q1 具有包括驱动器与控制逻辑的完整超低功耗 12 位模数转换器 (ADC) 阻性触摸屏转换器,可测量触压。

除了这些标准特性之外,TSC2008-Q1 还提供了触摸屏测量预处理以降低总线负载,从而减少主机处理器资源的消 耗,这样就可以将这些资源转给更重要的功能使用。

TSC2008-Q1 支持 SPI 串行总线和数据传输。 该器件可提供 8 位或 12 位的可编程分辨率,以适应不同的触摸屏 尺寸与性能需求。

TSC2008-Q1 采用 16 引脚、4 x 4 QFN 封装。 TSC2008-Q1 针对 -40°C 至 +105°C 的工业温度范围进行了特性 分析。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SureSet is a trademark of Texas Instruments. SPI is a trademark of Motorola Inc.

All other trademarks are the property of their respective owners.

www.ti.com.cn

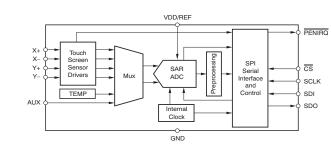

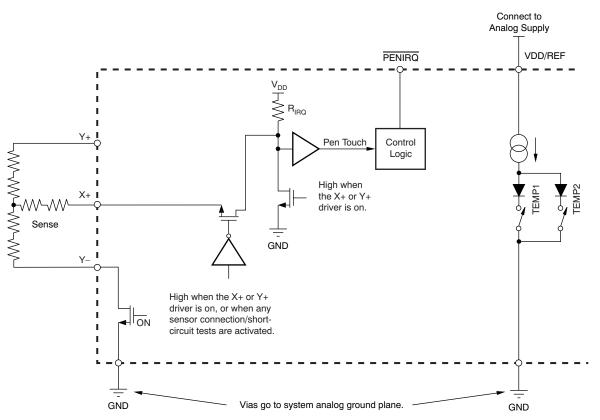

图 1. 方框图

2

## TEXAS INSTRUMENTS

#### ZHCS254-JUNE 2011

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| T <sub>A</sub> | PAC                     | KAGE | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|-------------------------|------|-----------------------|------------------|

| -40°C to 105°C | QFN - RGV Tape and Reel |      | TSC2008TRGVRQ1        | TSC2008T         |

(1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet, or see the TI website at www.ti.com.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted).

|                                             | TSC2008-Q1                      | UNIT                                                   |      |

|---------------------------------------------|---------------------------------|--------------------------------------------------------|------|

| Valtaga                                     | Analog input X+, Y+, AUX to GND | -0.4 to VDD + 0.1                                      | V    |

| Voltage                                     | Analog input X–, Y– to GND      | -0.4 to VDD + 0.1                                      | V    |

| Voltage range                               | VDD to GND                      | -0.3 to +5                                             | V    |

| Digital input voltage to GND                |                                 | -0.3 to VDD + 0.3                                      | V    |

| Digital output voltage to GND               |                                 | -0.3 to VDD + 0.3                                      | V    |

| Power dissipation                           |                                 | (T <sub>J</sub> Max - T <sub>A</sub> )/θ <sub>JA</sub> |      |

| Thermal impedance, $\theta_{JA}$            | QFN package                     | 47                                                     | °C/W |

| Operating free-air temperature range,       | , T <sub>A</sub>                | -40 to +105                                            | °C   |

| Storage temperature range, T <sub>STG</sub> |                                 | -65 to +150                                            | °C   |

| Junction temperature, T <sub>J</sub> Max    |                                 | +150                                                   | °C   |

|                                             | Vapor phase (60 sec)            | +215                                                   | °C   |

| Lead temperature                            | Infrared (15 sec)               | +220                                                   | °C   |

| IEC contact discharge <sup>(2)</sup>        | X+, X–, Y+, Y–                  | ±15                                                    | kV   |

| IEC air discharge <sup>(2)</sup>            | X+, X–, Y+, Y–                  | ±25                                                    | kV   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-maximum rated conditions for extended periods may affect device reliability.

(2) Test method based on IEC standard 61000-4-2. Device powered by battery. Contact Texas Instruments for test details.

# ZHCS254 - JUNE 2011

# **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40^{\circ}$ C to +105°C,  $V_{DD} = +1.2$ V to +3.6V, unless otherwise noted.

|                                             |                             |                                               |                                               | TS  | C2008-Q1 |                 |                    |

|---------------------------------------------|-----------------------------|-----------------------------------------------|-----------------------------------------------|-----|----------|-----------------|--------------------|

| PARAMETER                                   |                             |                                               | TEST CONDITIONS                               | MIN | TYP      | MAX             | UNIT               |

| AUXILIARY AN                                | ALOG INPUT                  | F                                             |                                               |     |          |                 |                    |

| Input voltage ra                            | nge                         |                                               |                                               | 0   |          | V <sub>DD</sub> | V                  |

| Input capacitand                            | ce                          |                                               |                                               |     | 12       |                 | pF                 |

| Input leakage cu                            | urrent                      |                                               |                                               | -1  |          | +1              | μA                 |

| A/D CONVERT                                 | ER                          |                                               |                                               |     |          |                 |                    |

| Resolution                                  |                             | Programmable:                                 | 8 or 12 bits                                  |     |          | 12              | Bits               |

| No missing code                             | es                          | 12-bit resolution                             | 1                                             | 11  |          |                 | Bits               |

| Integral linearity                          |                             |                                               |                                               |     | ±1.5     |                 | LSB <sup>(1)</sup> |

| Differential linea                          | rity                        |                                               |                                               |     | ±1       |                 | LSB                |

| Offect error                                |                             | $V_{DD} = 1.8V$                               |                                               |     | -1.2     |                 | LSB                |

| Offset error                                |                             | $V_{DD} = 3.0V$                               |                                               |     | -3.1     |                 | LSB                |

| Coin orror                                  |                             | $V_{DD} = 1.8V$                               |                                               |     | 0.7      |                 | LSB                |

| Gain error                                  |                             | V <sub>DD</sub> = 3.0V                        |                                               |     | 0.1      |                 | LSB                |

| TOUCH SENSO                                 | DRS                         |                                               |                                               |     |          |                 |                    |

|                                             | register D                  | $T_A = +25^{\circ}C, V_D$                     | <sub>D</sub> = 1.8V, setup command '10100000' |     | 50       |                 | kΩ                 |

| PENIRQ pull-up                              | resisior, R <sub>IRQ</sub>  | $T_A = +25^{\circ}C, V_D$                     | <sub>D</sub> = 1.8V, setup command '10101000' |     | 90       |                 | kΩ                 |

| Switch                                      | Y+, X+                      |                                               |                                               |     | 6        |                 | Ω                  |

| on-resistance                               | Y-, X-                      |                                               |                                               |     | 5        |                 | Ω                  |

| Switch drivers d                            | rive current <sup>(2)</sup> | 100ms duration                                |                                               |     |          | 50              | mA                 |

| INTERNAL TEN                                | IPERATURE SENS              | SOR                                           |                                               |     |          |                 |                    |

| Temperature rai                             | nge                         |                                               |                                               | -40 |          | +105            | °C                 |

|                                             |                             | Differential                                  | $V_{DD} = 3V$                                 |     | 1.94     |                 | °C/LSB             |

| Decolution                                  |                             | method <sup>(3)</sup><br>TEMP1 <sup>(4)</sup> | V <sub>DD</sub> = 1.6V                        |     | 1.04     |                 | °C/LSB             |

| Resolution                                  |                             |                                               | $V_{DD} = 3V$                                 |     | 0.35     |                 | °C/LSB             |

|                                             |                             |                                               | $V_{DD} = 1.6V$                               |     | 0.19     |                 | °C/LSB             |

|                                             |                             | Differential                                  | $V_{DD} = 3V$                                 |     | ±2       |                 | °C/LSB             |

| Acouroov                                    |                             | method <sup>(3)</sup>                         | $V_{DD} = 1.6V$                               |     | ±2       |                 | °C/LSB             |

| Accuracy                                    |                             | TEMP1 <sup>(4)</sup>                          | $V_{DD} = 3V$                                 |     | ±3       |                 | °C/LSB             |

|                                             |                             | TEMPTY                                        | $V_{DD} = 1.6V$                               | ±3  |          |                 | °C/LSB             |

| INTERNAL OS                                 | CILLATOR                    |                                               |                                               |     |          |                 |                    |

|                                             |                             |                                               | V <sub>DD</sub> = 1.2V                        |     | 3.19     |                 | MHz                |

|                                             |                             | 8-bit                                         | V <sub>DD</sub> = 1.8V                        |     | 3.66     |                 | MHz                |

|                                             |                             | 0-011                                         | V <sub>DD</sub> = 2.7V                        |     | 3.78     |                 | MHz                |

| Intornal alcali for                         | auonov f                    |                                               | V <sub>DD</sub> = 3.6V                        |     | 3.82     |                 | MHz                |

| Internal clock frequency, $f_{\text{CCLK}}$ |                             |                                               | V <sub>DD</sub> = 1.2V                        |     | 1.6      |                 | MHz                |

|                                             |                             | 12 bit                                        | V <sub>DD</sub> = 1.8V                        |     | 1.83     |                 | MHz                |

|                                             |                             | 12-bit                                        | V <sub>DD</sub> = 2.7V                        |     | 1.88     |                 | MHz                |

|                                             |                             |                                               | V <sub>DD</sub> = 3.6V                        |     | 1.91     |                 | MHz                |

| <b>F</b>                                    |                             | V <sub>DD</sub> = 1.6V                        |                                               |     | 0.0056   |                 | %/°C               |

| Frequency drift                             |                             | $V_{DD} = 3.0V$                               |                                               |     | 0.012    |                 | %/°C               |

(1)

LSB means *least significant bit*. With  $V_{DD}$  (REF) = +2.5V, 1LSB is 610µV. Ensured by design, but not production tested. Exceeding 50 mA source current may result in device degradation.

Difference between TEMP1 and TEMP2 measurement; no calibration necessary.

(2) (3) (4) Temperature drift is -2.1mV/°C.

# **ELECTRICAL CHARACTERISTICS (continued)**

At  $T_A = -40^{\circ}C$  to +105°C,  $V_{DD} = +1.2V$  to +3.6V, unless otherwise noted.

|                                              |                                  |                                                          |                                                   |                              | TSC2008-Q1          |       |                       |      |

|----------------------------------------------|----------------------------------|----------------------------------------------------------|---------------------------------------------------|------------------------------|---------------------|-------|-----------------------|------|

| PARAMETER                                    | 1                                |                                                          | TEST CONDITIONS                                   |                              |                     | TYP   | MAX                   | UNIT |

| DIGITAL INPU                                 | UT/OUTPUT                        |                                                          |                                                   |                              |                     |       |                       |      |

| Logic family                                 |                                  |                                                          |                                                   |                              |                     | CMOS  |                       |      |

|                                              | V <sub>IH</sub>                  | $1.2 V \leq V_DD < 3.6$                                  | V                                                 |                              | $0.7 \times V_{DD}$ |       | V <sub>DD</sub> + 0.3 | V    |

|                                              |                                  | $1.2 \text{V} \leq \text{V}_{\text{DD}} < 1.6$           | V                                                 |                              | -0.3                |       | $0.2 \times V_{DD}$   | V    |

|                                              | V <sub>IL</sub>                  | $1.6V \le V_{DD} \le 3.6$                                | V                                                 |                              | -0.3                |       | $0.3 \times V_{DD}$   | V    |

|                                              | IIL                              | CS, SCLK, and S                                          | CS, SCLK, and SDI pins                            |                              |                     |       | 1                     | μA   |

| Logic level                                  | C <sub>IN</sub> <sup>(5)</sup>   | CS, SCLK, and S                                          | SDI pins                                          |                              |                     |       | 10                    | pF   |

|                                              | V <sub>OH</sub>                  | I <sub>OH</sub> = 2 TTL load                             | S                                                 |                              | $V_{DD} - 0.2$      |       | V <sub>DD</sub>       | V    |

|                                              | V <sub>OL</sub>                  | I <sub>OL</sub> = 2 TTL loads                            | I <sub>OL</sub> = 2 TTL loads                     |                              |                     |       | 0.2                   | V    |

|                                              | I <sub>LEAK</sub> <sup>(5)</sup> | Floating output                                          | Floating output                                   |                              |                     |       | 1                     | μA   |

|                                              | C <sub>OUT</sub> <sup>(5)</sup>  | Floating output                                          |                                                   |                              |                     |       | 10                    |      |

| Data format                                  |                                  |                                                          |                                                   |                              | Straight Binary     |       |                       |      |

| POWER SUP                                    |                                  | NTS                                                      |                                                   |                              |                     |       |                       |      |

| Power-supply                                 | voltage                          |                                                          |                                                   |                              |                     |       |                       |      |

| V <sub>DD</sub>                              |                                  | Specified perform                                        | Specified performance                             |                              |                     |       | 3.6                   | V    |

|                                              |                                  | 12-bit,                                                  | V <sub>DD</sub> = 1.2V                            | 69.6k eq rate <sup>(6)</sup> |                     | 285.0 | 375.0                 | μA   |

|                                              |                                  | $f_{SCLK} = 5MHz,$<br>$f_{ADC} = 2MHz,$<br>PD[1:0] = 0,0 |                                                   | 8.2k eq rate <sup>(6)</sup>  |                     | 30.4  | 42.2                  | μA   |

| Quiescent sup<br>(V <sub>DD</sub> with sense |                                  | 40.1.1                                                   | V 4.0V                                            | 82.6k eq rate <sup>(6)</sup> |                     | 344.0 | 500.0                 | μA   |

|                                              |                                  | 12-bit,<br>f <sub>SCLK</sub> = 10MHz,                    | $V_{DD} = 1.8V$                                   | 8.2k eq rate <sup>(6)</sup>  |                     | 34.5  | 37.7                  | μA   |

|                                              |                                  | $f_{ADC} = 2MHz,$<br>PD[1:0] = 0,0                       | V 0.7V                                            | 84.8k eq rate <sup>(6)</sup> |                     | 461.0 | 630.0                 | μA   |

|                                              |                                  | PD[1:0] = 0,0                                            | $V_{DD} = 2.7 V$                                  | 8.2k eq rate <sup>(6)</sup>  |                     | 44.6  | 55.1                  | μA   |

| Power-down s                                 | supply current                   | $\overline{\text{CS}} = 1, \text{SDI} = \text{SOI}$      | CLK = 1, PENIRQ                                   | = 1, PD[1:0] = 0,0           |                     | 0     | 5.5                   | μA   |

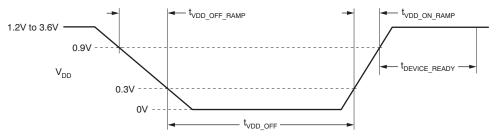

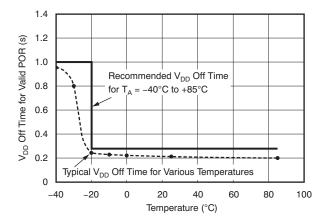

| POWER ON/C                                   |                                  | IIREMENTS <sup>(5)</sup> (see Figu                       | re 38)                                            |                              |                     |       |                       |      |

| t <sub>VDD_OFF_RAMP</sub>                    |                                  | $T_{A} = -40^{\circ}C \text{ to } +80^{\circ}C$          | 5°C                                               |                              | 2                   |       |                       | kV/s |

| t <sub>VDD_OFF</sub>                         |                                  | $T_{A} = -40^{\circ}C \text{ to } +80^{\circ}C$          | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ , VDD = 0V |                              |                     |       |                       | S    |

|                                              |                                  | $T_{A} = -20^{\circ}C \text{ to } +8$                    | $85^{\circ}C, VDD = 0V$                           |                              | 0.3                 |       |                       | S    |

| t <sub>VDD_ON_RAMP</sub>                     |                                  | $T_{A} = -40^{\circ}C \text{ to } +80^{\circ}C$          | 5°C                                               |                              | 12                  |       |                       | kV/s |

| tDEVICE_READY                                |                                  | $T_{A} = -40^{\circ}C \text{ to } +80^{\circ}C$          | 5°C                                               |                              | 2                   |       |                       | ms   |

(5) Ensured by design, but not production tested

(6) See the Throughput Rate and SPI Bus Traffic section for calculation information.

ZHCS254-JUNE 2011

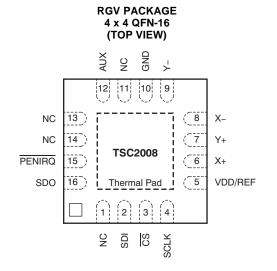

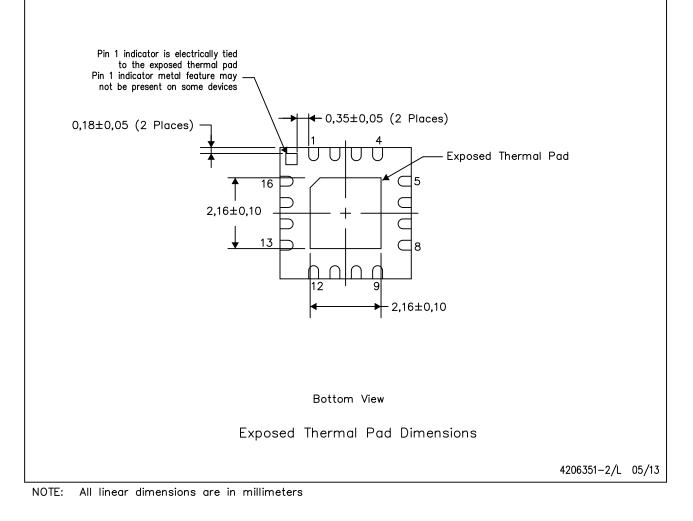

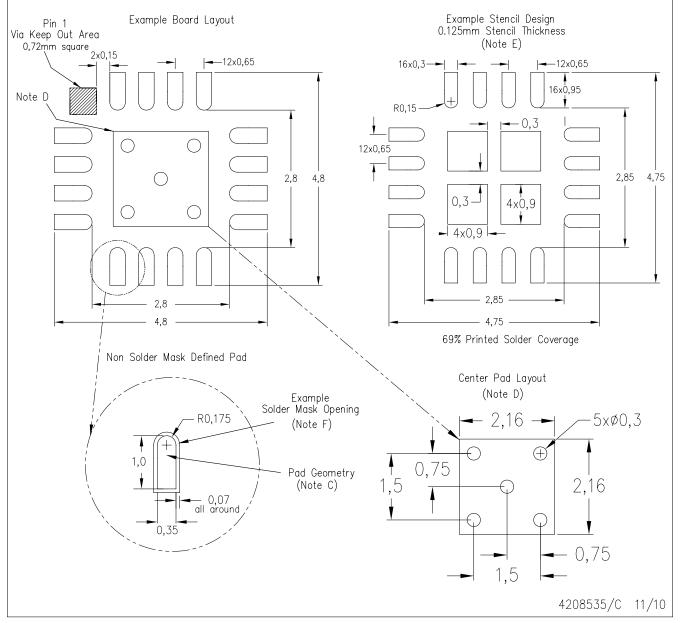

## **PIN CONFIGURATION**

(1) The thermal pad is internally connected to the substrate. The thermal pad can be connected to the analog ground or left floating. Keep the thermal pad separate from the digital ground, if possible.

| PIN<br>NO. | PIN<br>NAME | I/O | A/D | DESCRIPTION                                                                                                                                                                                    |

|------------|-------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | NC          |     |     | No connection                                                                                                                                                                                  |

| 2          | SDI         | I   | D   | Serial data input                                                                                                                                                                              |

| 3          | CS          | I   | D   | Chip select                                                                                                                                                                                    |

| 4          | SCLK        | I   | D   | Serial clock input                                                                                                                                                                             |

| 5          | VDD/REF     |     |     | Supply voltage and external reference input                                                                                                                                                    |

| 6          | X+          | I   | А   | X+ channel input                                                                                                                                                                               |

| 7          | Y+          | I   | А   | Y+ channel input                                                                                                                                                                               |

| 8          | X-          | I   | А   | X– channel input                                                                                                                                                                               |

| 9          | Y–          | I   | А   | Y– channel input                                                                                                                                                                               |

| 10         | GND         |     |     | Ground                                                                                                                                                                                         |

| 11         | NC          |     |     | No connection                                                                                                                                                                                  |

| 12         | AUX         | I   | А   | Auxiliary channel input. If not used, this input should be grounded.                                                                                                                           |

| 13         | NC          |     |     | No connection                                                                                                                                                                                  |

| 14         | NC          |     |     | No connection                                                                                                                                                                                  |

| 15         | PENIRQ      | 0   | D   | Pen touch interrupt output. Active low when pen is touched. The output remains low until conversion is complete or pen touch is released. The rising edge signals the end of conversion (EOC). |

| 16         | SDO         | 0   | D   | Serial data output                                                                                                                                                                             |

#### PIN ASSIGNMENTS

TSC2008-Q1

www.ti.com.cn

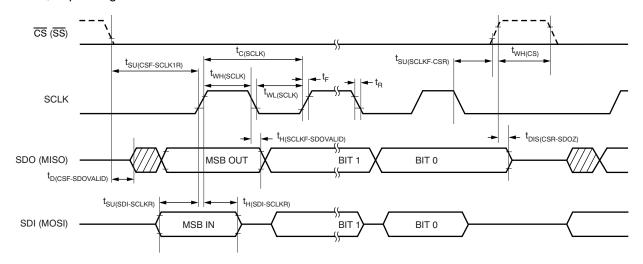

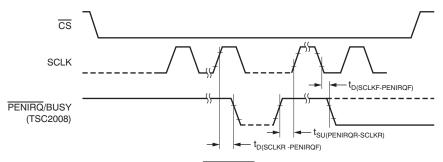

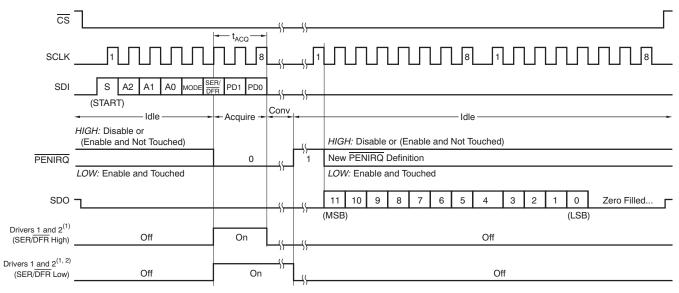

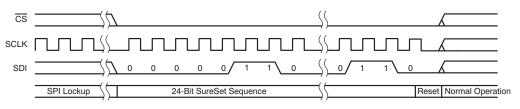

### TIMING INFORMATION

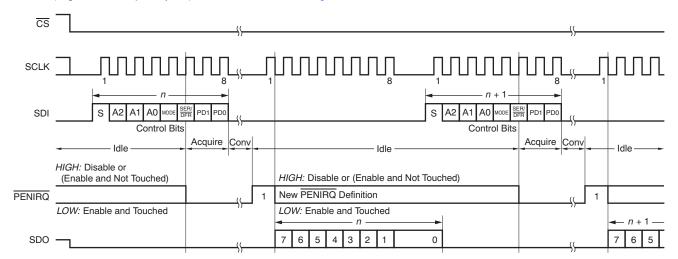

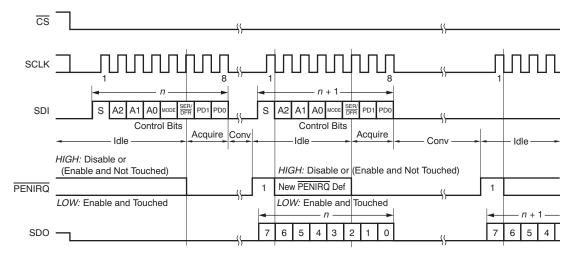

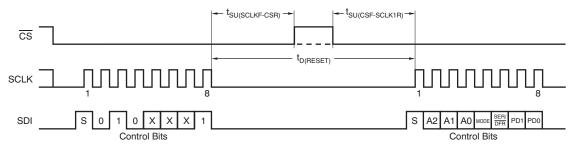

The TSC2008-Q1 supports SPI programming in mode CPOL = 0 and CPHA = 0. The falling edge of SCLK is used to change the output (MISO) data, and the rising edge is used to latch the input (MOSI) data. Eight SCLKs are required to complete the command byte cycle, and an additional eight or 16 SCLKs are required for the data to be read, depending on the mode used.

NOTE: CPOL = 0, CPHA = 0, Byte 0 cycle requires 24 SCLKs, and Byte 1 cycle requires 8 SCLKs.

Figure 2. Detailed I/O Timing

Figure 3. PENIRQ Timing

Texas Instruments

www.ti.com.cn

#### ZHCS254 - JUNE 2011

# TIMING REQUIREMENTS<sup>(1)</sup>

All specifications typical at  $-40^{\circ}$ C to  $+105^{\circ}$ C, VDD = 1.6V, unless otherwise noted.

| P                               | ARAMETER                                  | TEST CONDITIONS                          | MIN                      | MAX                        | UNIT |

|---------------------------------|-------------------------------------------|------------------------------------------|--------------------------|----------------------------|------|

|                                 |                                           | 1.2V ≤ VDD < 1.6V, 40% to 60% duty cycle | 182                      |                            | ns   |

| t <sub>C(SCLK)</sub>            | SPI serial clock cycle time               | 1.6 ≤ VDD < 2.7V, 40% to 60% duty cycle  | 62.5                     |                            | ns   |

|                                 |                                           | 2.7V ≤ VDD ≤ 3.6V, 40% to 60% duty cycle | 40                       |                            | ns   |

|                                 |                                           | 1.2V ≤ VDD < 1.6V, 10pF load             |                          | 5.5                        | MHz  |

| f <sub>SCLK</sub>               | SPI serial clock frequency                | 1.6 ≤ VDD < 2.7V, 10pF load              |                          | 16                         | MHz  |

|                                 |                                           | 2.7V ≤ VDD ≤ 3.6V, 10pF load             |                          | 25                         | MHz  |

| t <sub>WH(SCLK)</sub>           | SPI serial clock high time                |                                          | $0.4 \times t_{C(SCLK)}$ | 0.6 × t <sub>C(SCLK)</sub> | ns   |

| t <sub>WL(SCLK)</sub>           | SPI serial clock low time                 |                                          | $0.4 \times t_{C(SCLK)}$ | 0.6 × t <sub>C(SCLK)</sub> | ns   |

|                                 | Enchle land time                          | 1.2V ≤ VDD < 1.6V                        | 22                       |                            | ns   |

| tSU(CSF-SCLK1R)                 | Enable lead time                          | 1.6 ≤ VDD < 3.6V                         | 14                       |                            | ns   |

|                                 |                                           | 1.2V ≤ VDD < 1.6V                        |                          | 55                         | ns   |

| t <sub>D</sub> (CSF-SDOVALID)   | Slave access time                         | 1.6 ≤ VDD < 3.6V                         |                          | 25                         | ns   |

|                                 | MISO data hold time                       | 1.2V ≤ VDD < 1.6V                        | 40                       | 80                         | ns   |

| t <sub>H</sub> (SCLKF-SDOVALID) |                                           | 1.6 ≤ VDD < 3.6V                         | 6                        | 30                         | ns   |

|                                 | Sequential transfer delay                 | 1.2V ≤ VDD < 1.6V                        | 50                       |                            | ns   |

| t <sub>WH(CS)</sub>             |                                           | 1.6 ≤ VDD < 3.6V                         | 20                       |                            | ns   |

|                                 |                                           | 1.2V ≤ VDD < 1.6V                        | 25                       |                            | ns   |

| t <sub>SU(SDI-SCLKR)</sub>      | MOSI data setup time                      | 1.6 ≤ VDD < 3.6V                         | 10                       |                            | ns   |

| t <sub>H(SDI-SCLKR)</sub>       | MOSI data hold time                       |                                          | 5                        |                            | ns   |

|                                 |                                           | 1.2V ≤ VDD < 1.6V                        |                          | 55                         | ns   |

| tDIS(CSR-SDOZ)                  | Slave MISO disable time                   | 1.6 ≤ VDD < 3.6V                         |                          | 25                         | ns   |

|                                 | <b>F</b> 11 1 <i>C</i>                    | 1.2V ≤ VDD < 1.6V                        | 50                       |                            | ns   |

| t <sub>SU(SCLKF-CSR)</sub>      | Enable lag time                           | 1.6 ≤ VDD < 3.6V                         | 20                       |                            | ns   |

|                                 | PENIRQ (used as BUSY)                     | 1.2V ≤ VDD < 1.6V                        |                          | 55                         | ns   |

| <sup>t</sup> D(SCLKR-PENIRQF)   | delay from SCLK rising edge               | 1.6 ≤ VDD < 3.6V                         |                          | 25                         | ns   |

|                                 | Setup time from PENIRQ                    | 1.2V ≤ VDD < 1.6V                        | 50                       |                            | ns   |

| t <sub>SU(PENIRQR-SCLKR)</sub>  | (used as BUSY) to the rising edge of SCLK | 1.6 ≤ VDD < 3.6V                         | 20                       |                            | ns   |

| t <sub>D(RESET)</sub>           | Reset period requirement                  |                                          | 200                      |                            | ns   |

| t <sub>R</sub>                  | Rise time                                 | VDD = 3V, f <sub>SCLK</sub> = 25MHz      |                          | 3                          | ns   |

| t <sub>F</sub>                  | Fall time                                 | VDD = 3V, f <sub>SCLK</sub> = 25MHz      |                          | 3                          | ns   |

(1) All input signals are specified with  $t_R = t_F = 5ns$  (10% to 90% of VDD) and timed from a voltage level of (V<sub>IL</sub> + V<sub>IH</sub>)/2.

ZHCS254-JUNE 2011

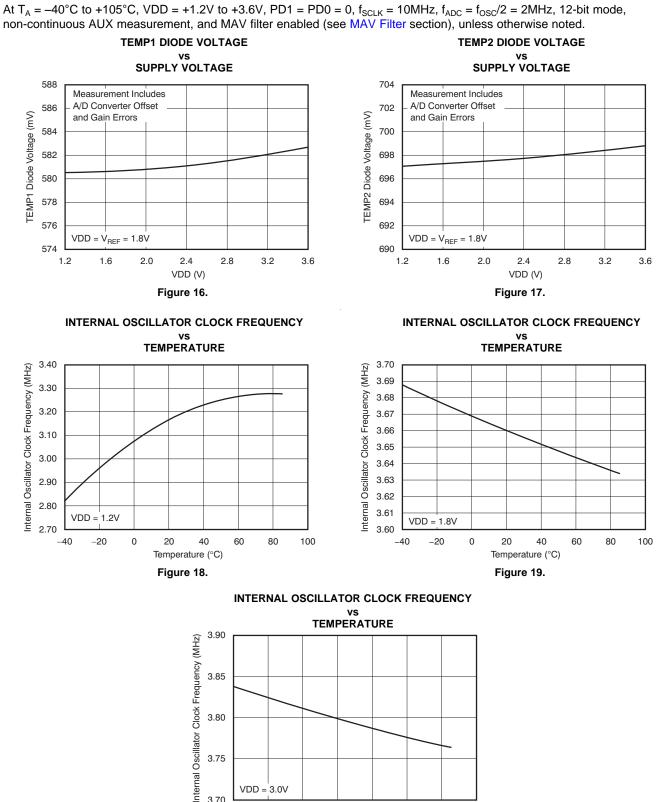

## **TYPICAL CHARACTERISTICS**

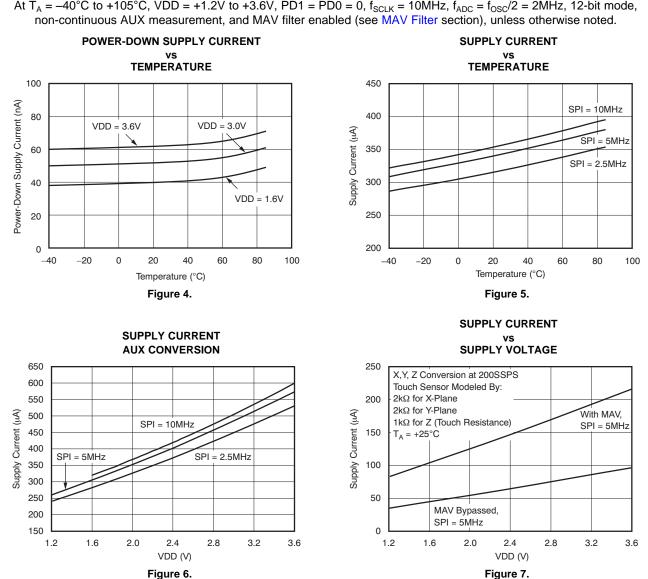

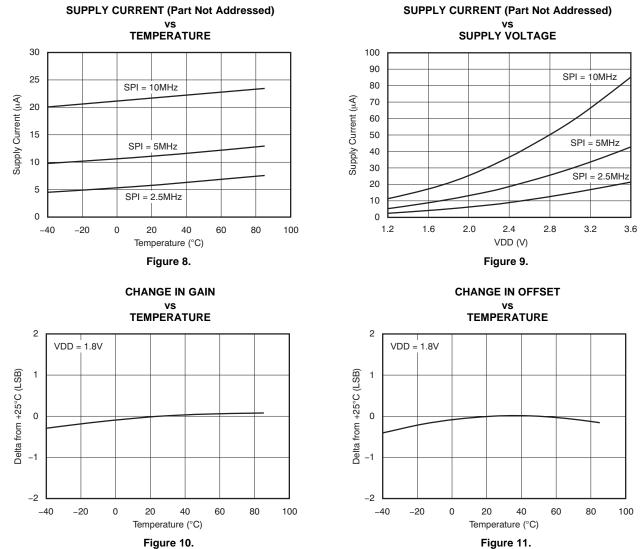

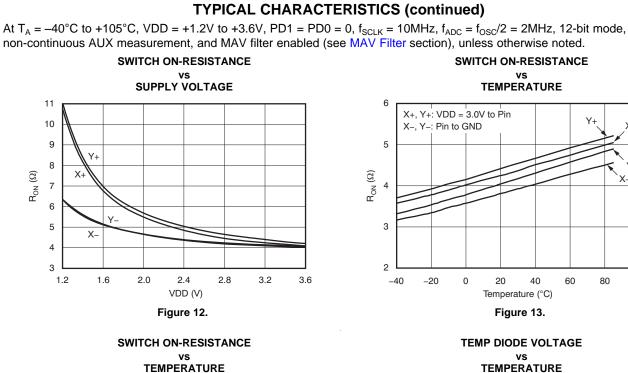

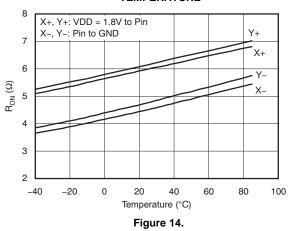

At  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C, VDD = +1.2V to +3.6V, PD1 = PD0 = 0,  $f_{SCLK} = 10$ MHz,  $f_{ADC} = f_{OSC}/2 = 2$ MHz, 12-bit mode, non-continuous AUX measurement, and MAV filter enabled (see MAV Filter section), unless otherwise noted.

At  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C, VDD = +1.2V to +3.6V, PD1 = PD0 = 0,  $f_{SCLK} = 10$ MHz,  $f_{ADC} = f_{OSC}/2 = 2$ MHz, 12-bit mode, non-continuous AUX measurement, and MAV filter enabled (see MAV Filter section), unless otherwise noted.

www.ti.com.cn

# TSC2008-Q1

100

ZHCS254-JUNE 2011

VDD = 3.0V

-20

0

20

40

Temperature (°C) Figure 20.

60

80

100

3.70

-40

ZHCS254 - JUNE 2011

www.ti.com.cn

**STRUMENTS**

XAS

# **TYPICAL CHARACTERISTICS (continued)**

#### ZHCS254 - JUNE 2011

## OVERVIEW

The TSC2008-Q1 is an analog interface circuit for a human interface touch screen device. All peripheral functions are controlled through the command byte and onboard state machines. While maintaining similarity in hardware, command, and software to its predecessor, the TSC2046 (or TSC2046E), the TSC2008-Q1 includes significant improvements such as:

- Much stronger and more comprehensive electrostatic discharge (ESD) protection

- Uses only 1/13 power for equivalent performance

- 1/7 bus traffic

- 3/16 size

- Direct 1.8V interface

- Prudent reset scheme

• Saves 1/7 power if 8-bit SDO adjusted output mode used

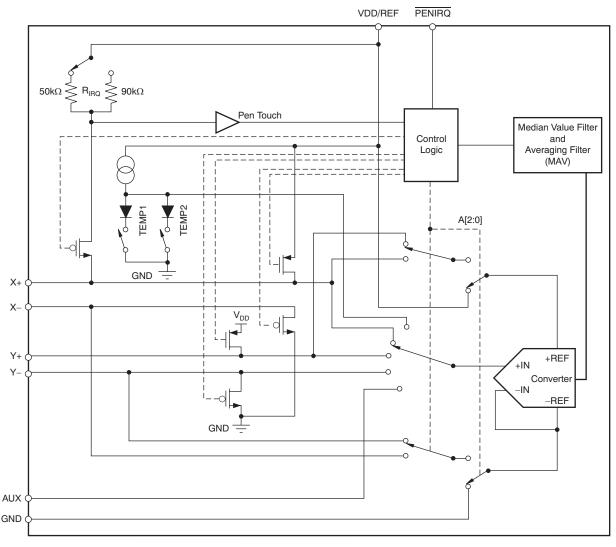

The TSC2008-Q1 consists of the following blocks (see 图 1):

- Touch Screen Sensor Drivers

- Auxiliary Input (AUX)

- Temperature Sensor

- Acquisition Activity Preprocessing

- Internal Conversion Clock

- SPI Interface

Communication with the TSC2008-Q1 is done via an SPI serial interface. The TSC2008-Q1 is an SPI slave device; therefore, data are shifted into or out of the TSC2008-Q1 under the control of the host microprocessor, which also provides the serial data clock.

Control of the TSC2008-Q1 and its functions is accomplished by writing to the command register of an internal state machine. A simple command protocol (compatible with SPI) is used to address this register.

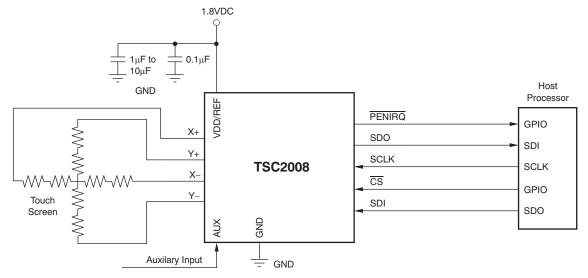

A typical application of the TSC2008-Q1 is shown in Figure 21.

Figure 21. Typical Circuit Configuration

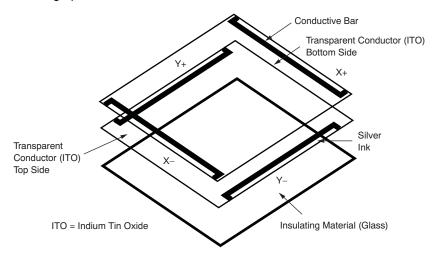

#### **TOUCH SCREEN OPERATION**

A resistive touch screen operates by applying a voltage across a resistor network and measuring the change in resistance at a given point on the matrix where the screen is touched by an input (stylus, pen, or finger). The change in the resistance ratio marks the location on the touch screen.

The TSC2008-Q1 supports resistive 4-wire configurations, as shown in Figure 22. The circuit determines location in two coordinate pair dimensions, although a third dimension can be added for measuring pressure.

## **4-WIRE TOUCH SCREEN COORDINATE PAIR MEASUREMENT**

A 4-wire touch screen is typically constructed as shown in Figure 22. It consists of two transparent resistive layers separated by insulating spacers.

Figure 22. 4-Wire Touch Screen Construction

The 4-wire touch screen panel works by applying a voltage across the vertical or horizontal resistive network. The A/D converter converts the voltage measured at the point where the panel is touched. A measurement of the Y position of the pointing device is made by connecting the X+ input to a data converter chip, turning on the Y+ and Y- drivers, and digitizing the voltage seen at the X+ input. The voltage measured is determined by the voltage divider developed at the point of touch. For this measurement, the horizontal panel resistance in the X+ lead does not affect the conversion because of the high input impedance of the A/D converter.

Voltage is then applied to the other axis, and the A/D converter converts the voltage representing the X position on the screen. This process provides the X and Y coordinates to the associated processor.

Measuring touch pressure (Z) can also be done with the TSC2008-Q1. To determine pen or finger touch, the pressure of the *touch* must be determined. Generally, it is not necessary to have very high performance for this test; therefore, 8-bit resolution mode may be sufficient (however, data sheet calculations are shown using 12-bit resolution mode). There are several different ways of performing this measurement. The TSC2008-Q1 supports two methods. The first method requires knowing the X-plate resistance, the measurement of the X-Position, and two additional cross panel measurements ( $Z_2$  and  $Z_1$ ) of the touch screen (see Figure 23). Equation 1 calculates the touch resistance:

$$R_{\text{TOUCH}} = R_{X-\text{plate}} \cdot \frac{X_{\text{Postition}}}{4096} \left( \frac{Z_2}{Z_1} - 1 \right)$$

(1)

ZHCS254-JUNE 2011 The second method requires knowing both the X-plate and Y-plate resistance, measurement of X-Position and

TSC2008-Q1

Y-Position, and Z<sub>1</sub>. Equation 2 also calculates the touch resistance:  $R_{\text{TOUCH}} = \frac{R_{\text{X-plate}} \cdot X_{\text{Postition}}}{4096} \left(\frac{4096}{Z_1} - 1\right) - R_{\text{Y-plate}} \cdot$ Y Position (2) Measure X-Position X+ Touch w X-Position Measure Z<sub>1</sub>-Position Touch w Z<sub>4</sub>-Position ò Touch ٨٨ Z<sub>2</sub>-Position X Measure Z<sub>2</sub>-Position

Figure 23. Pressure Measurement

When the touch panel is pressed or touched and the drivers to the panel are turned on, the voltage across the touch panel will often overshoot and then slowly settle down (decay) to a stable dc value. This effect is a result of mechanical bouncing caused by vibration of the top layer sheet of the touch panel when the panel is pressed. This settling time must be accounted for, or else the converted value is incorrect. Therefore, a delay must be introduced between the time the driver for a particular measurement is turned on, and the time a measurement is made.

In some applications, external capacitors may be required across the touch screen for filtering noise picked up by the touch screen (for example, noise generated by the LCD panel or back-light circuitry). The value of these capacitors provides a low-pass filter to reduce the noise, but creates an additional settling time requirement when the panel is touched. The settling time typically shows up as gain error. The TSC2008-Q1 has a built-in noise filter (see the *Preprocessing* section). These capacitors can be reduced to minimal value or not installed.

The TSC2008-Q1 touch screen interface can measure position (X,Y) and pressure (Z).

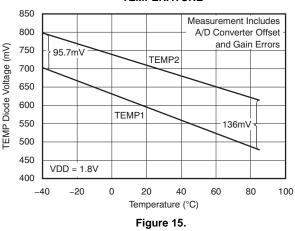

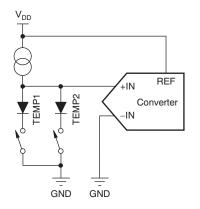

### INTERNAL TEMPERATURE SENSOR

In some applications, such as battery recharging, an ambient temperature measurement is required. The temperature measurement technique used in the TSC2008-Q1 relies on the characteristics of a semiconductor junction operating at a fixed current level. The forward diode voltage ( $V_{BE}$ ) has a well-defined characteristic versus temperature. The ambient temperature can be predicted in applications by knowing the +25°C value of the  $V_{BE}$  voltage and then monitoring the delta of that voltage as the temperature changes.

The TSC2008-Q1 offers two modes of temperature measurement. The first mode requires calibration at a known temperature, but only requires a single reading to predict the ambient temperature. The TEMP1 diode, shown in Figure 24, is used during this measurement cycle. This voltage is typically 580mV at +25°C with a 10µA current. The absolute value of this diode voltage can vary by a few millivolts; the temperature coefficient ( $T_C$ ) of this voltage is very consistent at -2.1mV/°C. During the final test of the end product, the diode voltage is stored at a known room temperature, in system memory, for calibration purposes by the user. The result is an equivalent temperature measurement resolution of 0.3°C/LSB (1LSB = 610µV with V<sub>REF</sub> = 2.5V).

Figure 24. Functional Block Diagram of Temperature Measurement Mode

The second mode does not require a test temperature calibration, but uses a two-measurement (differential) method to eliminate the need for absolute temperature calibration and for achieving 2°C/LSB accuracy. This mode requires a second conversion of the voltage across the TEMP2 diode with a resistance 91 times larger than the TEMP1 diode. The voltage difference between the first (TEMP1) and second (TEMP2) conversion is represented by:

$$\Delta V = \frac{kT}{q} \cdot \ln(N) \tag{3}$$

Where:

- N = the resistance ratio = 91.

- k = Boltzmann's constant =  $1.3807 \times 10^{-23}$  J/K (joules/kelvins).

- q = the electron charge =  $1.6022 \times 10^{-19}$  C (coulombs).

- T = the temperature in kelvins (K).

This method can provide much improved absolute temperature measurement, but a lower resolution of 1.6°C/LSB. The resulting equation to solve for T is:

$$\mathsf{T} = \frac{\mathsf{q} \cdot \Delta \mathsf{V}}{\mathsf{k} \cdot \mathsf{ln}(\mathsf{N})}$$

Where:

$\Delta V = V_{BE} (TEMP2) - V_{BE} (TEMP1) (in mV).$

$\therefore$  T = 2.573 ·  $\Delta$ V (in K),

or T =  $2.573 \cdot \Delta V - 273$  (in °C).

Temperature 1 and/or temperature 2 measurements have the same timing as shown in Figure 31 to Figure 34.

(4)

www.ti.com.cn

## ANALOG-TO-DIGITAL CONVERTER

Figure 25 shows the analog inputs of the TSC2008-Q1. The analog inputs (X, Y, and Z touch panel coordinates, chip temperature and auxiliary inputs) are provided via a multiplexer to the Successive Approximation Register (SAR) analog-to-digital converter (ADC). The A/D architecture is based on capacitive redistribution architecture, which inherently includes a sample-and-hold function.

Figure 25. Analog Input Section (Simplified Diagram)

A unique configuration of low on-resistance switches allows an unselected A/D converter input channel to provide power and an accompanying pin to provide ground for driving the touch panel. By maintaining a differential input to the converter and a differential reference input architecture, it is possible to negate errors caused by the driver switch on-resistance.

#### Reference

The TSC2008-Q1 uses an external voltage reference applied to the VDD/REF pin. The upper reference voltage range is the same as the supply voltage range, which allows for simple, 1.2V to 3.6V single-supply operation of the chip.

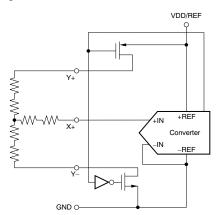

# ZHCS254 – JUNE 2011 Reference Mode

There is a critical item regarding the reference when making measurements while the switch drivers are on. For this discussion, it is useful to consider the basic operation of the TSC2008-Q1 (see Figure 21). This particular application shows the device being used to digitize a resistive touch screen. A measurement of the current Y position of the pointing device is made by connecting the X+ input to the A/D converter, turning on the Y+ and Y– drivers, and digitizing the voltage on X+, as shown in Figure 26. For this measurement, the resistance in the X+ lead does not affect the conversion; it does affect the settling time, but the resistance is usually small enough that this is not a concern. However, because the resistance between Y+ and Y– is fairly low, the on-resistance of the Y drivers does make a small difference. Under the situation outlined so far, it would not be possible to achieve a 0V input or a full-scale input regardless of where the pointing device is on the touch screen because some voltage is lost across the internal switches. In addition, the internal switch resistance is unlikely to track the resistance of the touch screen, providing an additional source of error.

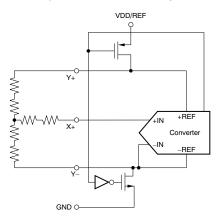

Figure 26. Simplified Diagram of Single-Ended Reference

This situation is resolved, as shown in Figure 27, by using the differential mode; the +REF and –REF inputs are connected directly to Y+ and Y–, respectively. This mode makes the A/D converter ratiometric. The result of the conversion is always a percentage of the external reference, regardless of how it changes in relation to the on-resistance of the internal switches. Note that there is an important consideration regarding power dissipation when using the ratiometric mode of operation (see the *Power Dissipation* section for more details).

Figure 27. Simplified Diagram of Differential Reference (Both Y Switches are Enabled, and X+ is the Analog Input)

#### **Touch Screen Settling**

In some applications, external capacitors may be required across the touch screen to filter noise picked up by the touch screen (that is, noise generated by the LCD panel or backlight circuitry). These capacitors provide a low-pass filter to reduce the noise, but they also cause a settling time requirement when the panel is touched. The settling time typically shows up as a gain error. The problem is that the input and/or reference has not settled to its final steady-state value before the A/D converter samples the input(s) and provides the digital output. Additionally, the reference voltage may continue to change during the measurement cycle.

There are two ways to resolve this issue. Option 1 is to stop or slow down the TSC2008-Q1 SCLK for the required touch screen settling time. This option allows the input and reference to have stable values for the Acquire period (three clock cycles of the TSC2008-Q1; see Figure 31). This option works for both the single-ended and the differential modes. Option 2 is to operate the TSC2008-Q1 in the differential mode only for the touch screen measurements and command the TSC2008-Q1 to remain on (touch screen drivers ON) and not go into power-down (PD0 = 1). Several conversions are made, depending on the settling time required and the TSC2008-Q1 data rate. Once the required number of conversions have been made, the processor commands the TSC2008-Q1 to go into its power-down state on the last measurement. This process is required for X-Position, Y-Position, and Z-Position measurements.

#### Touch Detect

The  $\overline{\text{PENIRQ}}$  can be used as an interrupt to the host.  $R_{\text{IRQ}}$  is an internal pull-up resistor with a programmable value of either 50k $\Omega$  (default) or 90k $\Omega$  (which allows the total resistance from X+ to Y– to be as high as 30k $\Omega$ ). Write command '1010' (setup command) followed by data '1xx0' sets the pull-up resistor to 90k $\Omega$ . **NOTE:** The first three bits must be '0's and the select bit is the last bit. To change the pull-up resistor back to 50k $\Omega$ , issue write command '1010' followed by data '0xx0'.

An example for the Y-position measurement is detailed in Figure 28. The PENIRQ output is pulled high by an internal <u>pull-up</u> resistor. While in power-down mode with PD0 = 0, the Y- driver is on and connected to GND, and the PENIRQ output is connected to the X+ input. When the panel is touched, the X+ input is pulled to ground through the touch screen, and PENIRQ output goes low because of the current path through the panel to GND, initiating an interrupt to the processor. During the measurement cycle for X-, Y-, and Z-Position, the X+ input is disconnected from the PENIRQ pull-down transistor to eliminate any pull-up resistor leakage current from flowing through the touch screen, thus causing no errors.

If the last command byte written to the TSC2008-Q1 contains PD0 = 1, the pen-interrupt output function is disabled and cannot detect when the panel is touched. In order to re-enable the pen-interrupt output function under these circumstances, a command byte must be written to the TSC2008-Q1 with PD0 = 0.

If the last command byte contains PD0 = 0, then the pen-interrupt function is enabled at the end of a conversion. The end of conversion (EOC) occurs on the rising edge of  $\overline{PENIRQ}$ .

In both cases previously listed, it is recommended that whenever the host writes to the TSC2008-Q1, the master processor masks the interrupt associated to PENIRQ. This masking prevents false triggering of interrupts when the PENIRQ line is disabled in the cases previously listed.

www.ti.com.cn

Figure 28. Example of a Pen-Touch Induced Interrupt via the **PENIRQ** Pin

## Preprocessing

The TSC2008-Q1 has a fixed combined MAV filter (median value filter and averaging filter).

#### **MAV** Filter

If the acquired signal source is noisy because of the digital switching circuit, it may necessary to evaluate the data without noise. In this case, the median value filter operation helps remove the *noise*. The array of seven converted results is sorted first. The middle three values are then averaged to produce the output value of the MAV filter.

The MAV filter is applied to all measurements for all analog inputs including the touch screen inputs, temperature measurements TEMP1 and TEMP2, and auxiliary input AUX. To shorten the conversion time, the MAV filter may be bypassed though the setup command; see Table 2 and Table 4.

Figure 29. MAV Filter Operation (Patent Pending)

## DIGITAL INTERFACE

The TSC2008-Q1 communicates through a standard SPI bus. The SPI allows full-duplex, synchronous, serial communication between a host processor (the master) and peripheral devices (slaves). The SPI master generates the synchronizing clock and initiates transmissions. The SPI slave devices depend on a master to start and synchronize transmissions.

A transmission begins when initiated by a master SPI. The byte from the master SPI begins shifting in on the slave SDI (MOSI—master out, slave in) pin under the control of the master serial clock. As the byte shifts in on the SDI (MOSI) pin, a byte shifts out on the SDO (MISO—master in, slave out) pin to the master shift register.

The idle state of the TSC2008-Q1 serial clock is logic low, which corresponds to a clock polarity setting of 0 (typical microprocessor SPI control bit CPOL = 0). The TSC2008-Q1 interface is designed so that with a clock phase bit setting of 0 (typical microprocessor SPI control bit CPHA = 0), the master begins driving its MOSI pin and the slave begins driving its MISO pin half an SCLK before the first serial clock edge. The CS (SS, slave select) pin can remain low between transmissions.

#### Table 1. Standard SPI Signal Names vs Common Serial Interface Signal Names

| SPI SIGNAL NAMES           | COMMON SERIAL INTERFACE NAMES |

|----------------------------|-------------------------------|

| SS (Slave Select)          | CS (Chip Select)              |

| MISO (Master In Slave Out) | SDO (Serial Data Out)         |

| MOSI (Master Out Slave In) | SDI (Serial Data In)          |

As a comparison to the popular TSC2046 timing characteristics, a few differences between the interfaces are worth notice:

- 1. Unlike the TSC2046, there is not a 15 SCLK cycle for the TSC2008-Q1.

- 2. There is an adjusted SDO timing that allows an 8-bit, back-to-back cycle.

- 3. The TSC2008-Q1 uses an internal conversion clock; therefore, the SPI serial clock (SCLK) can only affect the acquiring period and I/O transfer.

- 4. The TSC2008-Q1 uses an internal clock to perform the conversion. PENIRQ rises when the conversion is complete. If the host issues an SCLK before the conversion is complete, PENIRQ also rises, but the conversion result is invalid.

- 5. If a new command is issued before a conversion is complete (indicated by EOC), then the conversion is aborted.

- 6. Releasing the SPI bus (by raising  $\overline{CS}$ ) during the conversion is OK, but releasing the SPI during the I/O transfer (for example, read result) aborts the data transfer.

# CONTROL BYTE

The control byte (on SDI), as shown in Table 2, provides the start conversion, addressing, A/D converter resolution, configuration, and power-down of the TSC2008-Q1. Figure 31, Table 2, and Table 3 give detailed information regarding the order and description of these control bits within the control byte.

#### Table 2. Order of the Control Bits in the Control Byte

| BIT 7<br>(MSB) | BIT 6 | BIT 5 | BIT 4 | BIT 3   | BIT 2   | BIT 1  | BIT 0<br>(LSB) | COMMENT                |

|----------------|-------|-------|-------|---------|---------|--------|----------------|------------------------|

| S              | A2    | A1    | A0    | MODE    | SER/DFR | PD1    | PD0            | Excludes setup command |

| S              | 0     | 1     | 0     | Pull-up | Bypass  | Timing | Reset          | Setup command          |

### Table 3. Description of the Control Bits in the Control Byte

| BIT | DESCRIPTION                                                                                                                                                                                                                                                          |                                                                                                                                                                                   |  |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7   | Start Bit. When this bit = '1', it indicates this is one of the user commands. A new control byte can start every 16th clock cycle in 12-bit conversion mode or every 12th clock cycle in 8-bit conversion mode (see Figure 31 through Figure 34).                   |                                                                                                                                                                                   |  |  |  |  |  |  |

| 6-4 | Bit[6:4] = A[2:0]. Channel select command if A[2:0] $\neq$ '010'.<br>These channel select bits, along with the SER/DFR bit, control the setting of the multiplexer input, touch driver switches, and reference inputs (see Table 4 and Figure 31 through Figure 34). | Bit[6:4] = A[2:0]. Setup command if A[2:0] = '010'.                                                                                                                               |  |  |  |  |  |  |

| 3   | Mode Select Bit. This bit controls the number of bits for<br>the next conversion.<br>0: 12 bits (low)<br>1: 8 bits (high).                                                                                                                                           | Pull-up Resistor Select Bit <sup>(1)</sup> .<br>0: 50kΩ <u>PENIRQ</u> pull-up resistor (default).<br>1: 90kΩ <u>PENIRQ</u> pull-up resistor.                                      |  |  |  |  |  |  |

| 2   | Single-Ended/Differential Reference Select Bit (SER/DFR). Along with the channel select bits, A[2:0], this bit controls the setting of the multiplexer input, touch driver switches, and reference inputs (see Table 4).                                             | Bypass Noise Filter Bit <sup>(1)</sup> .<br>0: MAV noise filter enabled (default).<br>1: MAV noise filter bypassed.                                                               |  |  |  |  |  |  |

| 1-0 | Bit[1:0] = PD[1:0]. Power Down Mode Select Bits.                                                                                                                                                                                                                     | Bit 1: Timing Select Bit <sup>(1)</sup> .<br>0: TSC2046-compatible timing for SDO during data read (default)<br>1: Adjusted SDO timing; MSB appears before 1st rising clock edge. |  |  |  |  |  |  |

| 1-0 | See Table 5 for details.                                                                                                                                                                                                                                             | Bit 0: Software Reset Bit.<br>0: Nothing happens (default).<br>1: Software reset.                                                                                                 |  |  |  |  |  |  |

(1) These bits configure the pull-up resistor value, control the filter bypass, and select the SDO output timing. The bits are static and the values are stored in register bits that will only be reset to default by a reset condition (power-on reset, software reset, or SureSet) or changed with the setup command.

# TSC2008-Q1

#### www.ti.com.cn

The control byte begins with a start bit followed by seven control bits. For the command to be valid, the start bit must be '1'. Do not use '0' for the start bit; it is reserved for factory use.

**Initiate Start**—The first bit is the start bit (S), and must always be high to initiate the start of a user-controllable control byte. When the start bit = '0', it is reserved for factory use.

Addressing and Command Decoding—The next three bits in the control byte following the start bit are three addressing bits A[2:0] used to select the active input channel(s) of the input multiplexer (see Table 4 and Figure 25), enable the touch screen drivers, select the reference inputs, or decode other commands.

Bit[6:4] = '010' is the setup command that is used to configure the TSC.

Bit[3:0] followed by the setup command are the configuration bits and are used to select the pull-up resistor value, bypass the noise filter (in the preprocessing unit), select the SDO output timing, and perform the software reset. Bit[3:1] are static—that is, they do not change once programmed unless either the device is powered off, one of the reset conditions occur (power-on reset, software reset, or SureSet), or unless changed with the setup command. Note that if any reset occurs, bit[3:1] is set to the default values listed in Table 3. Any function decoded as shown in Table 4 (excluding the setup command) has no access to these four configuration bits.

|        |                                       | r    | 1          |                       |           |           | 1                            |

|--------|---------------------------------------|------|------------|-----------------------|-----------|-----------|------------------------------|

| A[2:0] | BIT <u>2<sup>(1)</sup></u><br>SER/DFR | +REF | –REF = –IN | INPUT TO<br>ADC = +IN | X-DRIVERS | Y-DRIVERS | DESCRIPTION                  |

| 0h     | Don't care                            | VDD  | GND        | TEMP1                 | All OFF   | All OFF   | Measure TEMP1                |

| 1h     | 1 (single-ended)                      | VDD  | GND        | X+                    | All OFF   | All ON    | Measure Y position           |

| 1h     | 0 (differential mode)                 | Y+   | Y–         | X+                    | All OFF   | All ON    | Measure Y position           |

| 2h     | Used as noise filter<br>bypass        |      | _          | _                     | All OFF   | All OFF   | Setup command <sup>(2)</sup> |

| 3h     | 1 (single-ended)                      | VDD  | GND        | X+                    | X– ON     | Y+ ON     | Measure Z1 position          |

| 3h     | 0 (differential mode)                 | Y+   | X–         | X+                    | X– ON     | Y+ ON     | Measure Z1 position          |

| 4h     | 1 (single-ended)                      | VDD  | GND        | Y–                    | X– ON     | Y+ ON     | Measure Z2 position          |

| 4h     | 0 (differential mode)                 | Y+   | X–         | Y–                    | X– ON     | Y+ ON     | Measure Z2 position          |

| 5h     | 1 (single-ended)                      | VDD  | GND        | Y+                    | All ON    | All OFF   | Measure X position           |

| 5h     | 0 (differential mode)                 | X+   | X–         | Y+                    | All ON    | All OFF   | Measure X position           |

| 6h     | Don't care                            | VDD  | GND        | AUX                   | All OFF   | All OFF   | Measure AUX                  |

| 7h     | Don't care                            | VDD  | GND        | TEMP2                 | All OFF   | All OFF   | Measure TEMP2                |

#### Table 4. Converter Function Select (CFS) Information

(1) Bit 2 is the SER/DFR control bit for all commands except for the setup command.

(2) Use the setup command to configure the touch screen controller or access the software reset function.

**MODE**—The mode bit sets the resolution of the A/D converter. With this bit low, the next conversion has 12 bits of resolution; with this bit high, the next conversion has eight bits of resolution.

**SER/DFR** —The SER/DFR bit controls the reference mode: either single-ended (high) or differential (low). The differential mode is also referred to as the ratiometric conversion mode and is preferred for X-Position, Y-Position, and Pressure-Touch measurements for optimum performance. The reference is derived from the voltage at the switch drivers, which is almost the same as the voltage to the touch screen. In this case, a reference voltage is not needed because the reference voltage to the A/D converter is the same as the voltage across the touch screen. In single-ended mode, the converter reference voltage is always the difference between the VREF and GND pins (see Table 4 and Figure 25 through Figure 27, for further information).

If X-Position, Y-Position, and Pressure-Touch are measured in the single-ended mode, then VDD is used as the reference.

**NOTE:** The differential mode can only be used for X-Position, Y-Position, and Pressure-Touch measurements. All other measurements require the single-ended mode.

**PD0 and PD1**—The power-down bits select the power-down mode that the TSC2008-Q1 will be in after the current command completes, as shown in Table 5.

It is recommended to set PD0 = '0' in each command byte to get the lowest power consumption possible. If multiple X-, Y-, and Z-position measurements are performed sequentially (such as when averaging), PD0 = '1' leaves the touch screen drivers on at the end of each conversion cycle.

| PD1 | PD0 | PENIRQ   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                  |

|-----|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Enabled  | Power-Down Between Conversions. When each conversion is finished, the converter enters a low-power mode. At the start of the next conversion, the device instantly powers up to full power. There is no need for additional delays to ensure full operation, and the very first conversion is valid. The Y– switch is on when in power-down. |

| 0   | 1   | Disabled | A/D converter on. PENIRQ disabled.                                                                                                                                                                                                                                                                                                           |

| 1   | 0   | Enabled  | A/D converter off. PENIRQ enabled.                                                                                                                                                                                                                                                                                                           |

| 1   | 1   | Disabled | A/D converter on. PENIRQ disabled.                                                                                                                                                                                                                                                                                                           |

#### Table 5. Power-Down and Internal Reference Selection

#### Variable Resolution

The TSC2008-Q1 provides either 8-bit or 12-bit resolution for the A/D converter. Lower resolution is often practical for measuring slow changing signals such as touch pressure. Performing the conversions at lower resolution reduces the amount of time it takes for the A/D converter to complete its conversion process, which also lowers power consumption.

#### 8- and 12-Bit Conversion

The TSC2008-Q1 provides both 12-bit or 8-bit conversion modes.

The 12-bit conversion mode can be done in 24 SCLKs per cycle or 16 SCLKs per cycle timing; see Figure 31 and Figure 32 for details. The 8-bit conversion can be done in 24 SCLKs per cycle (although this mode is unlikely to be selected), 16 SCLKs per cycle, or even 8 SCLKs per cycle (when adjusted SDO timing is selected); see Figure 33 and Figure 34 for details.

The 8-bit mode can be used when faster throughput is needed and the digital result is not as critical. By switching to the 8-bit conversion mode, a conversion is complete four internal conversion clock cycles earlier and also takes less time to transfer the result. The internal conversion clock runs at twice the speed (4MHz typical) than the 12-bit conversion mode. This faster conversion and transfer saves power.

#### **Conversion Clock and Conversion Time**

The TSC2008-Q1 contains an internal clock that drives the state machines that perform the many functions of the device. This clock is divided down to provide a clock that runs the A/D converter. The 8-bit ADC mode uses a 4MHz clock and the 12-bit ADC mode uses a 2MHz clock. The actual frequency of this internal clock is slower than the name suggests, and varies with the supply voltage.

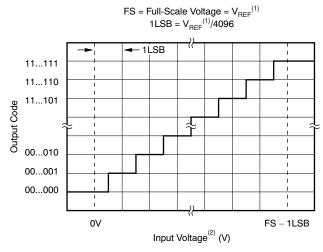

### Data Format

The TSC2008-Q1 output data are in Straight Binary format as shown in Figure 30. This figure shows the ideal output code for the given input voltage and does not include the effects of offset, gain, or noise.

- (1) Reference voltage at converter: +REF (–REF). See Figure 25.

- (2) Input voltage at converter, after multiplexer: +IN (–IN). See Figure 25.

## Figure 30. Ideal Input Voltages and Output Codes

#### ZHCS254 – JUNE 2011

## **12-BIT OPERATION TIMING**

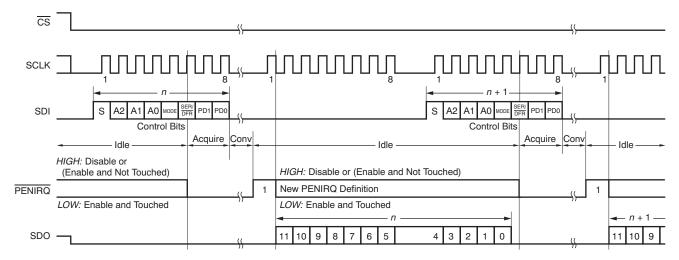

A single touch result can be easily achieved using 24 SCLKs per cycle operation when the 12-bit ADC mode is used, as shown in Figure 31. However, because this operation uses slightly more bus bandwidth, a more efficient method is to overlap the control bytes with the conversion result using 16 SCLKs per cycle operation; see Figure 32.

NOTES: (1) For Y-Position, Driver 1 is on X+ is selected, and Driver 2 is off. For X-Position, Driver 1 is off, Y+ is selected, and Driver 2 is on. Y- will turn on when power-down mode is entered and PD0 = 0.

(2) Drivers will remain on if PD0 = 1 (no power down) until selected input channel, or power-down mode is changed, or  $\overline{CS}$  is high.

## Figure 31. Conversion Timing—12-Bit Mode, 24 SCLKs per Cycle, 8-Bit Bus Interface

The control bits for conversion n + 1 can be overlapped with conversion n to allow for a conversion every 16 clock cycles, as shown in Figure 32. After submitting the control bits, the TSC2008-Q1 uses the internal clock to acquire data from seven conversions (see Figure 29). Deselecting the TSC2008-Q1 ( $\overline{CS} = '1'$ ) during this time period allows the host to communicate with the other peripherals using the same SPI bus before reading out the ADC data.

#### www.ti.com.cn

## **8-BIT OPERATION TIMING**

If the 8-bit ADC mode produces an acceptable result, then 16 SCLKs per cycle operation can also be used, as shown in Figure 33. If SDO is released one-half SCLK cycle earlier (with the SDO adjusted option), the fastest transfer (eight SCLKs per cycle) is achievable; see Figure 34.

Figure 33. Conversion Timing—8-Bit Mode, 16 SCLKs per Cycle, 8-Bit Bus Interface, without Adjusted SDO Timing (TSC2046-Compatible)

Figure 34. Conversion Timing—8-Bit Mode, 8 SCLKs per Cycle, 8-Bit Bus Interface, with Adjusted SDO Timing

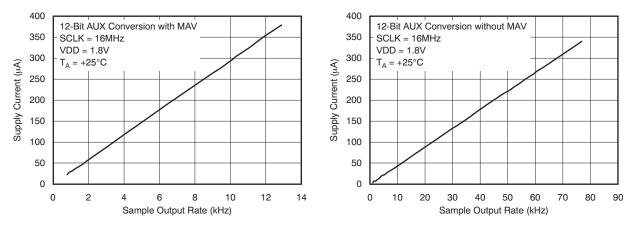

#### POWER DISSIPATION

There are two major power modes for the TSC2008-Q1: full-power (PD0 = '1') and auto power-down (PD0 = '0'). Unlike its predecessor, the TSC2046/2046E (where operation is synchronous to SCLK and therefore power depends on the SCLK frequency), the TSC2008-Q1 uses an internal clock for conversion and is asynchronous to SCLK. TSC2008-Q1 power consumption depends on the sample rate and is minimally affected by the SCLK frequency. Figure 31 shows a timing example using 12-bit resolution and 24 SCLKs per cycle. There are approximately 2.5 SCLKs of acquisition time used at the end of the 8-bit command cycle. When the preprocessing filter is on, the next six acquisition cycles are controlled by the internal conversion clock instead of relying on the external SCLK. A conversion time follows each acquisition time. Because there are six more conversions to be completed, and also because of the power used from preprocessing, the power consumption when the filter is on is higher than the power consumed without the filter at the same output rate, as shown in Figure 35. This timing sequence also applies to Figure 32 to Figure 34. Thus, using the TSC2008-Q1, power consumption can be very low, even with a low SCLK frequency.

Figure 35. Sample Output Rate vs Supply Current (with and without MAV filter)

Another important consideration for power dissipation is the reference mode of the converter. In the single-ended reference mode, the touch panel drivers are on only when the analog input voltage is being acquired (see Figure 31 and Table 4). The external device (for example, a resistive touch screen), therefore, is only powered during the acquisition period. In the differential reference mode, the external device must be powered throughout the acquisition and conversion periods (see Figure 31). If the conversion rate is high, using this mode could substantially increase power dissipation.

## THROUGHPUT RATE AND SPI BUS TRAFFIC

Although the internal A/D converter has a sample rate of up to 200kSPS, the throughput presented at the bus is much lower. The rate is reduced because preprocessing manages the redundant work of filtering out noise. The throughput is further limited by the SPI bus bandwidth, which is determined by the supply voltage and what the host processor can support. The effective throughput is approximately 20kSPS at 8-bit resolution, or 10kSPS at 12-bit resolution. The preprocessing saves a large portion of the SPI bandwidth for the system to use on other devices.

Each sample and conversion takes 19 CCLK cycles (12-bit), or 16 CCLK cycles (8-bit). The TSC2008-Q1 contains an internal clock that drives the state machines that perform the many functions of the device. This clock is divided down to provide a clock that runs the A/D converter. The 8-bit ADC mode uses a 4MHz clock and the 12-bit ADC mode uses a 2MHz clock. The actual frequency of this internal clock is slower than the name suggests, and varies with the supply voltage. For a typical internal 4MHz OSC clock, the frequency actually ranges from 3.66MHz to 3.82MHz. For VDD = 1.2V, the frequency reduces to 3.19MHz, which gives a 3.19MHz/16 = 199kSPS raw A/D converter sample rate.

#### **12-Bit Operation**

For 12-bit operation, sending the conversion result across the SPI bus takes 16 or 24 bus clocks (SCLK clock); see Figure 32 and Figure 31. There is an additional SCLK to be added to accommodate the cycle overhead (time between consecutive cycles) so that the total bus cycle time used for calculating the throughput is actually 17 or 25 bus clocks (SCLK clock), respectively. Using a TSC2046-compatible SDO output mode or an SDO-adjusted output mode does not affect the transmission time.

Seven sample-and-conversions take (19 x 7) internal clocks to complete. The MAV filter loop requires 19 internal clocks. For VDD = 1.2V, the complete processed data cycle time calculations are shown in Table 6. Because the first acquisition cycle overlaps with the I/O cycle, four CCLKs must be deducted from the total CCLK cycles. The total time required is  $(19 \times 7 + 19) - 4 = 148$  CCLKs plus I/O.

#### 8-Bit Operation

For 8-bit operation, sending the conversion result across the SPI bus takes 8, 16, or 24 bus clocks (SCLK clock); see Figure 34, Figure 33, and Figure 31. There is an additional SCLK to be added to accommodate the cycle overhead (time between consecutive cycles) so that the total bus cycle time used for calculating the throughput is actually 9, 17, or 25 bus clocks (SCLK clock), respectively. Sending the conversion result takes 17 or 25 SCLKs using 8-bit resolution and a TSC2046-compatible SDO output mode. If an SDO-adjusted output mode is used with 8-bit resolution, it takes only 9 or 17 SCLKs to send the result back to host.

Seven sample-and-conversions take (16 x 7) internal clocks to complete. The MAV filter loop takes 19 internal clocks. For VDD = 1.2V, the complete processed data cycle time calculations are shown in Table 6. Because the first acquisition cycle is overlapped with the I/O cycle, four CCLKs must be deducted from the total CCLK cycles. The total time required is  $(16 \times 7 + 19) - 4 = 127$  CCLKs plus I/O.