TAS5731

具有数字信号处理器 (DSP) 和 2.1 模式的 2 x 20W 数字音频功率放大器

查询样片: TAS5731

## 特性

- 2 通道 I<sup>2</sup>S 输入; 8kHz 至 48kHz f<sub>S</sub>

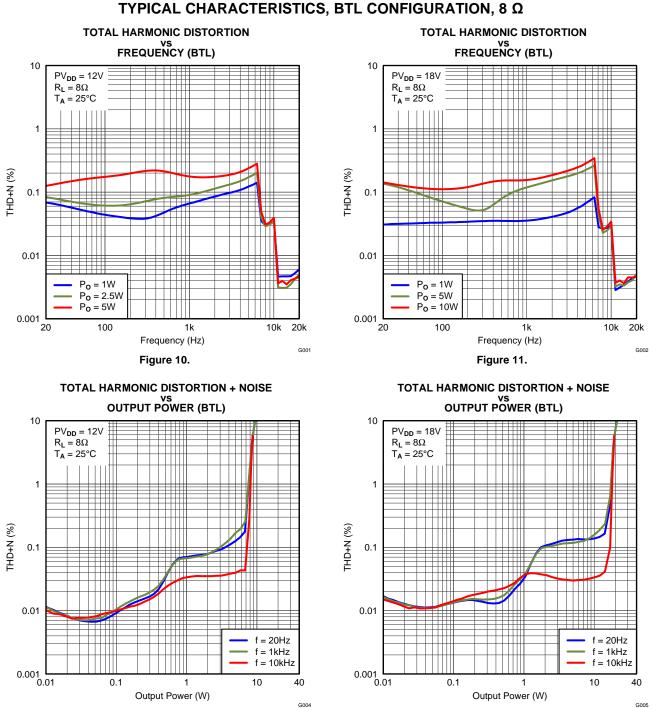

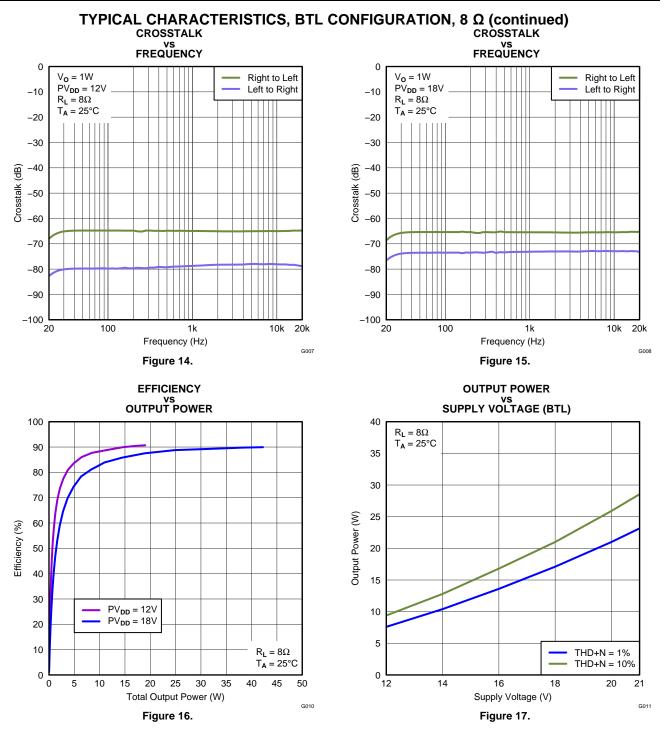

- 20W 立体声, 8Ω / 18V(总谐波失真 (THD) + N = 10%)

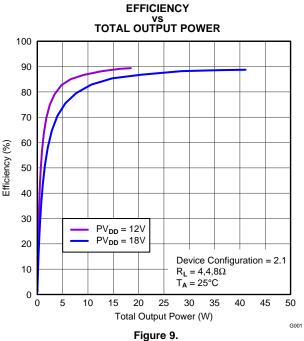

- 最高 90% 效率运行

- 8V 至 21V 宽电源电压范围;

3.3V 数字电源

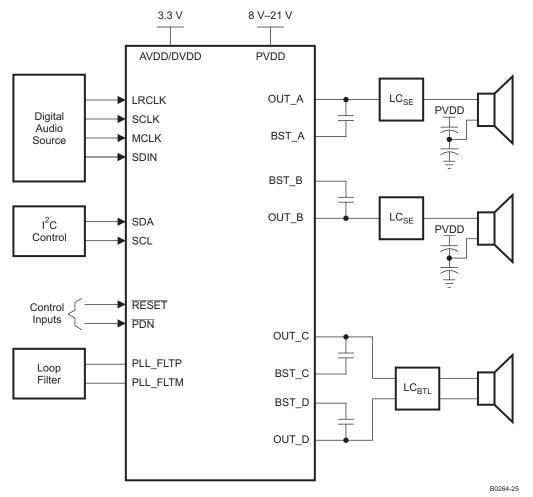

- 支持单一器件 2.1 (2×单端 (SE) + 1×桥接负载 (BTL))

- 可支持 2Ω SE 和 4Ω BTL 模式的 70mΩ R<sub>DS(on)</sub> 器件

- 12V / 2Ω / 8W SE 模式

- 12V / 4Ω / 15W BTL 模式

- 扬声器均衡 (EQ)(每通道 8BQ), 2 x 动态范围压 缩 (DRC)

- 与 TAS5727 引脚到引脚 (P2P) 兼容

- 优势

- 直接连接至数字处理器

- 来自标准电源的高输出功率

- 无需散热器

- 高级处理改善了音频体验

#### 应用范围

- 液晶电视 (LCD) 电视

- 发光二极管 (LED) 电视

- 投音机

#### 说明

TAS5731 是一款 20W,高效,数字音频立体声功率放 大器,此放大器用于驱动立体声桥接式扬声器。一个 串行数据输入可处理最多两个离散音频通道并能与大多 数数字音频处理器和 MPEG 解码器无缝整合。此器件 可接受宽范围的输入数据和数据传输速率。一个完全 可编程数据路径将这些通道路由至内部扬声器驱动器。

TAS5731 只能作为从属器件,从外部源接收所有时 钟。根据输入采样率的不同,TAS5731 运行时带有 384kHz 开关速率至 352KHz 开关速率间的的脉宽宽度 调制 (PWM) 载波。 与四阶噪声整形器结合的过采样 可提供一个白噪音基准以及从 20Hz 至 20kHz 的出色 动态范围。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# TAS5731

TEXAS INSTRUMENTS

ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# SIMPLIFIED 2.1 APPLICATION DIAGRAM

ZHCS602A – DECEMBER 2011 – REVISED SEPTEMBER 2013

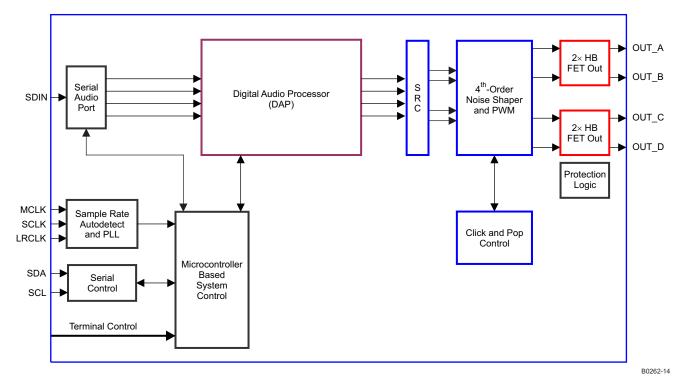

## **FUNCTIONAL VIEW**

B0034-08

Figure 1. Power-Stage Functional Block Diagram

4

www.ti.com.cn

ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

## DAP Process Structure

TEXAS INSTRUMENTS

#### ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

www.ti.com.cn

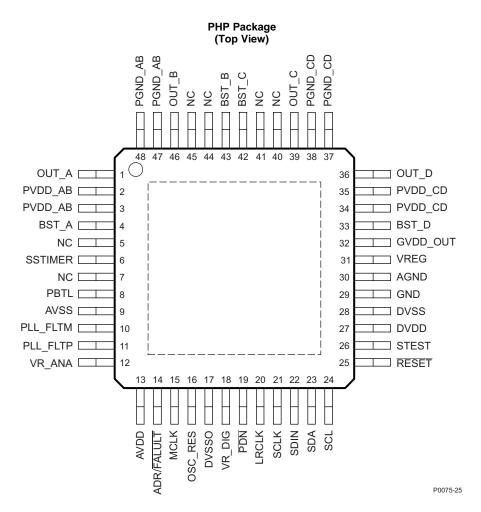

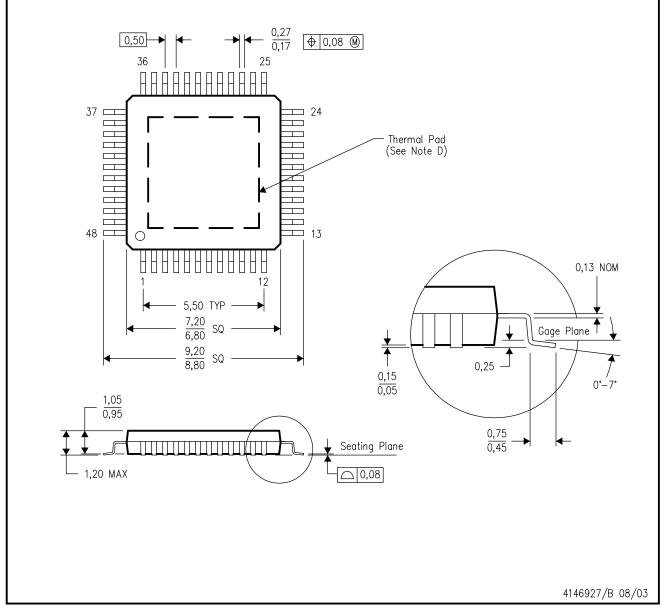

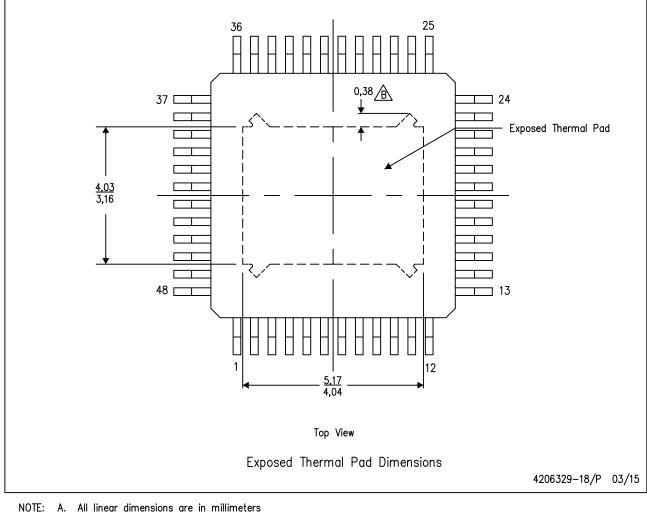

#### **DEVICE INFORMATION**

**PIN FUNCTIONS**

| PIN       |     | TYPE <sup>(1)</sup> | 5-V      | TERMINATION <sup>(2)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-----|---------------------|----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | NO. | ITPE                | TOLERANT | IERMINATION (*)            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AGND      | 30  | Р                   |          |                            | Local analog ground for power stage, which should be connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ADR/FAULT | 14  | DIO                 |          |                            | Dual function terminal which sets the LSB of the 7-bit $l^2C$ address to<br>"0" if pulled to GND and to "1" if pulled to DVDD. If configured to be<br>a fault output by the methods described in $l^2C$ Address Selection and<br>Fault Output, this terminal is pulled low when an internal fault occurs.<br>A pull-up or pull-down resistor is required, as is shown in the Typical<br>Application Circuit Diagrams. If pulled high (to DVDD), a $15k\Omega$<br>resistor should be used to minimize in-rush current at power up and<br>to isolate the net if the pin is used as a fault output, as described<br>above. |

| AVDD      | 13  | Р                   |          |                            | 3.3-V analog power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AVSS      | 9   | Р                   |          |                            | Analog 3.3-V supply ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BST_A     | 4   | Р                   |          |                            | High-side bootstrap supply for half-bridge A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BST_B     | 43  | Р                   |          |                            | High-side bootstrap supply for half-bridge B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

(1) TYPE: A = analog; D = 3.3-V digital; P = power/ground/decoupling; I = input; O = output

(2) All pullups are 20-µA weak pullups and all pulldowns are 20-µA weak pulldowns. The pullups and pulldowns are included to assure proper input logic levels if the terminals are left unconnected (pull-ups → logic 1 input; pulldowns → logic 0 input). Devices that drive inputs with pullups must be able to sink 20 µA while maintaining a logic-0 drive level. Devices that drive inputs with pulldowns must be able to source 20 µA while maintaining a logic-1 drive level.

#### ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

# **PIN FUNCTIONS (continued)**

| PIN      |                               |                     | (2)      |                            |                                                                                                                                                                                                                                                  |  |

|----------|-------------------------------|---------------------|----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO.                           | TYPE <sup>(1)</sup> | TOLERANT | TERMINATION <sup>(2)</sup> | DESCRIPTION                                                                                                                                                                                                                                      |  |

| BST_C    | 42                            | Р                   |          |                            | High-side bootstrap supply for half-bridge C                                                                                                                                                                                                     |  |

| BST_D    | 33                            | Р                   |          |                            | High-side bootstrap supply for half-bridge D                                                                                                                                                                                                     |  |

| DVDD     | 27                            | Р                   |          |                            | 3.3-V digital power supply                                                                                                                                                                                                                       |  |

| DVSS     | 28                            | Р                   |          |                            | Digital ground                                                                                                                                                                                                                                   |  |

| DVSSO    | 17                            | Р                   |          |                            | Oscillator ground                                                                                                                                                                                                                                |  |

| GND      | 29                            | Р                   |          |                            | Analog ground for power stage                                                                                                                                                                                                                    |  |

| GVDD_OUT | 32                            | Р                   |          |                            | Gate drive internal regulator output                                                                                                                                                                                                             |  |

| LRCLK    | 20                            | DI                  | 5-V      | Pulldown                   | Input serial audio data left/right clock (sample-rate clock)                                                                                                                                                                                     |  |

| MCLK     | 15                            | DI                  | 5-V      | Pulldown                   | Master clock input                                                                                                                                                                                                                               |  |

| NC       | 5, 7,<br>40,<br>41,<br>44, 45 | _                   |          |                            | No connect                                                                                                                                                                                                                                       |  |

| OSC_RES  | 16                            | AO                  |          |                            | Oscillator trim resistor. Connect an 18.2-kΩ, 1% resistor to DVSSO.                                                                                                                                                                              |  |

| OUT_A    | 1                             | 0                   |          |                            | Output, half-bridge A                                                                                                                                                                                                                            |  |

| OUT_B    | 46                            | 0                   |          |                            | Output, half-bridge B                                                                                                                                                                                                                            |  |

| OUT_C    | 39                            | 0                   |          |                            | Output, half-bridge C                                                                                                                                                                                                                            |  |

| OUT_D    | 36                            | 0                   |          |                            | Output, half-bridge D                                                                                                                                                                                                                            |  |

| PBTL     | 8                             | DI                  |          | Pulldown                   | Low means BTL mode; high means PBTL mode. Information goes directly to power stage.                                                                                                                                                              |  |

| PDN      | 19                            | DI                  | 5-V      | Pullup                     | Power down, active-low. PDN prepares the device for loss of power supplies by shutting down the noise shaper and initiating the PWM stop sequence.                                                                                               |  |

| PGND_AB  | 47, 48                        | Р                   |          |                            | Power ground for half-bridges A and B                                                                                                                                                                                                            |  |

| PGND_CD  | 37, 38                        | Р                   |          |                            | Power ground for half-bridges C and D                                                                                                                                                                                                            |  |

| PLL_FLTM | 10                            | AO                  |          |                            | PLL negative loop-filter terminal                                                                                                                                                                                                                |  |

| PLL_FLTP | 11                            | AO                  |          |                            | PLL positive loop-filter terminal                                                                                                                                                                                                                |  |

| PVDD_AB  | 2, 3                          | Р                   |          |                            | Power-supply input for half-bridge output A and B                                                                                                                                                                                                |  |

| PVDD_CD  | 34, 35                        | Р                   |          |                            | Power-supply input for half-bridge output C and D                                                                                                                                                                                                |  |

| RESET    | 25                            | DI                  | 5-V      | Pullup                     | Reset, active-low. A system reset is generated by applying a logic<br>low to this pin. RESET is an asynchronous control signal that<br>restores the DAP to its default conditions and places the PWM in the<br>hard-mute (high-impedance) state. |  |

| SCL      | 24                            | DI                  | 5-V      |                            | I <sup>2</sup> C serial control clock input                                                                                                                                                                                                      |  |

| SCLK     | 21                            | DI                  | 5-V      | Pulldown                   | Serial audio-data clock (shift clock). SCLK is the serial-audio-port input-data bit clock.                                                                                                                                                       |  |

| SDA      | 23                            | DIO                 | 5-V      |                            | I <sup>2</sup> C serial control data interface input/output                                                                                                                                                                                      |  |

| SDIN     | 22                            | DI                  | 5-V      | Pulldown                   | Serial audio data input. SDIN supports three discrete (stereo) data formats.                                                                                                                                                                     |  |

| SSTIMER  | 6                             | AI                  |          |                            | Controls ramp time of OUT_x to minimize pop. Leave this pin floating for BD mode. Requires capacitor of 2.2 nF to GND in AD mode. The capacitor determines the ramp time.                                                                        |  |

| STEST    | 26                            | DI                  |          |                            | Factory test pin. Connect directly to DVSS.                                                                                                                                                                                                      |  |

| VR_ANA   | 12                            | Р                   |          |                            | Internally regulated 1.8-V analog supply voltage. This pin must not be used to power external devices.                                                                                                                                           |  |

| VR_DIG   | 18                            | Р                   |          |                            | Internally regulated 1.8-V digital supply voltage. This pin must not be used to power external devices.                                                                                                                                          |  |

| VREG     | 31                            | Р                   |          |                            | Digital regulator output. Not to be used for powering external circuitry.                                                                                                                                                                        |  |

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                        |                                                                                                                                                                                                                                                                                                                                                                                                                                 | VALUE                             | UNIT |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|

| Currente currente e re | DVDD, AVDD         -0.3 to 3.6           PVDD_x         -0.3 to 30           3.3-V digital input         -0.5 to DVDD + 0.5           5-V tolerant <sup>(2)</sup> digital input (except MCLK)         -0.5 to DVDD + 2.5 <sup>(3)</sup> 5-V tolerant MCLK input         -0.5 to AVDD + 2.5 <sup>(3)</sup> x         27 <sup>(4)</sup> x         34 <sup>(4)</sup> ent, I <sub>IK</sub> ±20           rrent, I <sub>OK</sub> ±20 | V                                 |      |

| Supply voltage         | PVDD_x                                                                                                                                                                                                                                                                                                                                                                                                                          | -0.3 to 30                        | V    |

|                        | 3.3-V digital input                                                                                                                                                                                                                                                                                                                                                                                                             | -0.5 to DVDD + 0.5                |      |

| Input voltage          | 5-V tolerant <sup>(2)</sup> digital input (except MCLK)                                                                                                                                                                                                                                                                                                                                                                         | -0.5 to DVDD + 2.5 <sup>(3)</sup> | V    |

|                        | 5-V tolerant MCLK input                                                                                                                                                                                                                                                                                                                                                                                                         | -0.5 to AVDD + 2.5 <sup>(3)</sup> |      |

| OUT_x to PGND          | )_x                                                                                                                                                                                                                                                                                                                                                                                                                             | 27 <sup>(4)</sup>                 | V    |

| BST_x to PGND          | _x                                                                                                                                                                                                                                                                                                                                                                                                                              | 34 <sup>(4)</sup>                 | V    |

| Input clamp curr       | ent, I <sub>IK</sub>                                                                                                                                                                                                                                                                                                                                                                                                            | ±20                               | mA   |

| Output clamp cu        | rrent, I <sub>OK</sub>                                                                                                                                                                                                                                                                                                                                                                                                          | ±20                               | mA   |

| Operating free-a       | ir temperature                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 to 85                           | °C   |

| Operating junction     | on temperature range                                                                                                                                                                                                                                                                                                                                                                                                            | 0 to 150                          | °C   |

| Storage tempera        | iture range, T <sub>stq</sub>                                                                                                                                                                                                                                                                                                                                                                                                   | -40 to 125                        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating *Conditions* is not implied. Exposure to absolute-maximum conditions for extended periods may affect device reliability. 5-V tolerant inputs are PDN, RESET, SCLK, LRCLK, MCLK, SDIN, SDA, and SCL.

(2)

(3) Maximum pin voltage should not exceed 6 V.

(4) DC voltage + peak ac waveform measured at the pin should be below the allowed limit for all conditions.

## THERMAL INFORMATION

|                         | THERMAL METRIC <sup>(1)</sup>                | TAS5731       | UNIT |

|-------------------------|----------------------------------------------|---------------|------|

|                         |                                              | PHP (48 PINS) | UNIT |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance       | 27.9          | °C/W |

| $\theta_{JB}$           | Junction-to-board thermal resistance         | 13            | °C/W |

| θ <sub>JC(bottom)</sub> | Junction-to-case (bottom) thermal resistance | 1.1           | °C/W |

| θ <sub>JC(top)</sub>    | Junction-to-case (top) thermal resistance    | 20.7          | °C/W |

| τιΨ                     | Junction-to-top characterization parameter   | 0.3           | °C/W |

| Ψ <sub>JB</sub>         | Junction-to-board characterization parameter | 6.7           | °C/W |

(1) 有关传统和全新热度量的更多信息,请参阅 IC 封装热度量 应用报告 (文献号:ZHCA543)。

#### **RECOMMENDED OPERATING CONDITIONS**

|                               |                                      |                                                             | MIN | NOM | MAX                 | UNIT |  |

|-------------------------------|--------------------------------------|-------------------------------------------------------------|-----|-----|---------------------|------|--|

|                               | Digital/analog supply voltage        | DVDD, AVDD                                                  | 3   | 3.3 | 3.6                 | V    |  |

|                               | Half-bridge supply voltage           | PVDD_x                                                      | 8   |     | 21.5 <sup>(1)</sup> | V    |  |

| V <sub>IH</sub>               | High-level input voltage             | 5-V tolerant                                                | 2   |     |                     | V    |  |

| V <sub>IL</sub>               | Low-level input voltage              | 5-V tolerant                                                |     |     | 0.8                 | V    |  |

| T <sub>A</sub>                | Operating ambient temperature range  |                                                             | 0   |     | 85                  | °C   |  |

| T <sub>J</sub> <sup>(2)</sup> | Operating junction temperature range |                                                             | 0   |     | 125                 | °C   |  |

|                               | Les d'anna les se                    | Output filter: L = 15 $\mu$ H, C = 680 nF,<br>PVDD_x ≤ 13 V | 3   |     |                     | 0    |  |

| R <sub>L</sub> (PBTL)         | Load impedance                       | Output filter: L = 15 $\mu$ H, C = 680 nF,<br>PVDD_x > 13 V | 4   |     |                     | Ω    |  |

| R <sub>L</sub> (BTL)          | Load impedance                       | Output filter: L = 15 µH, C = 680 nF                        | 4   |     |                     | Ω    |  |

|                               | Lood impodance                       | Output filter: L = 15 $\mu$ H, C = 680 nF,<br>PVDD_x ≤ 13 V | 2   |     |                     | _    |  |

| R <sub>L</sub> (SE)           | Load impedance                       | Output filter: L = 15 $\mu$ H, C = 680 nF,<br>PVDD_x > 13 V | 4   |     |                     | Ω    |  |

For operation at PVDD\_x levels greater than 18V, the modulation limit must be set to 93.8% via the control port register 0x10. (1)

Continuous operation above the recommended junction temperature may result in reduced reliability and/or lifetime of the device. (2)

#### ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

## **RECOMMENDED OPERATING CONDITIONS (continued)**

|    |                          |                                                             | MIN | NOM | MAX | UNIT |

|----|--------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| Lo | Output-filter inductance | Minimum output inductance under short-<br>circuit condition | 10  |     |     | μH   |

#### **PWM OPERATION AT RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                   | TEST CONDITIONS                     | VALUE | UNIT  |

|-----------------------------|-------------------------------------|-------|-------|

| Output DWM outph froguenou  | 11.025/22.05/44.1-kHz data rate ±2% | 352.8 | ki la |

| Output PWM switch frequency | 48/24/12/8/16/32-kHz data rate ±2%  | 384   | kHz   |

### PLL INPUT PARAMETERS AND EXTERNAL FILTER COMPONENTS

|                                          | PARAMETER                                | TEST CONDITIONS      | MIN    | TYP | MAX    | UNIT  |

|------------------------------------------|------------------------------------------|----------------------|--------|-----|--------|-------|

| f <sub>MCLKI</sub>                       | MCLK frequency                           |                      | 2.8224 |     | 24.576 | MHz   |

|                                          | MCLK duty cycle                          |                      | 40%    | 50% | 60%    |       |

| t <sub>r</sub> /<br>t <sub>f(MCLK)</sub> | Rise/fall time for MCLK                  |                      |        |     | 5      | ns    |

|                                          | LRCLK allowable drift before LRCLK reset |                      |        |     | 4      | MCLKs |

|                                          | External PLL filter capacitor C1         | SMD 0603 X7R         |        | 47  |        | nF    |

|                                          | External PLL filter capacitor C2         | SMD 0603 X7R         |        | 4.7 |        | nF    |

|                                          | External PLL filter resistor R           | SMD 0603, metal film |        | 470 |        | Ω     |

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

$T_A = 25^{\circ}$ , PVCC\_x = 18 V, DVDD = AVDD = 3.3 V, R<sub>L</sub>= 8  $\Omega$ , BTL AD mode,  $f_S = 48$  kHz (unless otherwise noted)

|                                    | PARAMETER                                             |                                               | TEST CONDITIONS                                  | MIN | TYP | MAX               | UNIT |

|------------------------------------|-------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-----|-----|-------------------|------|

| V <sub>OH</sub>                    | High-level output voltage                             | ADR/FAULTand SDA                              | I <sub>OH</sub> = -4 mA<br>DVDD = 3 V            | 2.4 |     |                   | V    |

| V <sub>OL</sub>                    | Low-level output voltage                              | ADR/FAULTand SDA                              | I <sub>OL</sub> = 4 mA<br>DVDD = 3 V             |     |     | 0.5               | V    |

| IIL                                | Low-level input current                               |                                               | $V_{I} < V_{IL}$ ; DVDD = AVDD<br>= 3.6V         |     |     | 75                | μA   |

| I <sub>IH</sub>                    | High-level input current                              |                                               | $V_I > V_{IH}$ ; DVDD =<br>AVDD = 3.6V           |     |     | 75 <sup>(1)</sup> | μA   |

|                                    |                                                       |                                               | Normal mode                                      |     | 49  | 68                |      |

| I <sub>DD</sub>                    | 3.3 V supply current                                  | 3.3 V supply voltage (DVDD,<br>AVDD)          | Reset (RESET = low,<br>PDN = high)               |     | 23  | 38                | mA   |

|                                    |                                                       |                                               | Normal mode                                      |     | 32  | 50<br>8           |      |

| I <sub>PVDD</sub>                  | Supply current                                        | No load (PVDD_x)                              | $\frac{\text{Reset}}{\text{PDN}} = \text{high})$ |     | 3   |                   | mA   |

| (2)                                | Drain-to-source resistance, LS                        | on resistance                                 |                                                  | 80  |     | 0                 |      |

| r <sub>DS(on)</sub> <sup>(2)</sup> | Drain-to-source resistance, HS                        | T <sub>J</sub> = 25°C, includes metallization | on resistance                                    |     | 80  |                   | mΩ   |

| I/O Protectio                      | on .                                                  |                                               |                                                  |     |     |                   |      |

| V <sub>uvp</sub>                   | Undervoltage protection limit                         | PVDD falling                                  |                                                  |     | 6.4 |                   | V    |

| V <sub>uvp,hyst</sub>              | Undervoltage protection limit                         | PVDD rising                                   |                                                  |     | 7.1 |                   | V    |

| OTE <sup>(3)</sup>                 | Overtemperature error                                 |                                               |                                                  |     | 150 |                   | °C   |

| OTE <sub>HYST</sub> (3)            | Extra temperature drop required to recover from error |                                               |                                                  |     | 30  |                   | °C   |

| l <sub>oc</sub>                    | Overcurrent limit protection                          | Output to output short in BTL r               | node                                             |     | 4.5 |                   | А    |

| I <sub>OCT</sub>                   | Overcurrent response time                             |                                               |                                                  |     | 150 |                   | ns   |

(1)  $I_{IH}$  for the PBTL pin has a maximum limit of 200  $\mu$ A due to an internal pulldown on the pin. (2) This does not include bond-wire or pin resistance.

(3) Specified by design

Copyright © 2011–2013, Texas Instruments Incorporated

www.ti.com.cn

# AC Characteristics (BTL, PBTL)

PVDD\_x = 18 V, BTL AD mode,  $f_S = 48$  KHz,  $R_L = 8 \Omega$ ,  $C_{BST} = 33$  nF, audio frequency = 1 kHz, AES17 filter,  $f_{PWM} = 384$  kHz,  $T_A = 25^{\circ}$ C (unless otherwise specified). All performance is in accordance with recommended operating conditions (unless otherwise specified).

|       | PARAMETER                            | TEST CONDITIONS                                             | MIN | TYP  | MAX | UNIT |  |

|-------|--------------------------------------|-------------------------------------------------------------|-----|------|-----|------|--|

|       |                                      | BTL mode, PVDD = 8 V, 7% THD                                |     | 4    |     |      |  |

|       |                                      | BTL mode, PVDD = 8 V, 10% THD                               |     | 4.2  |     |      |  |

|       |                                      | BTL mode, PVDD = 12 V, 7% THD                               |     | 9.1  |     |      |  |

|       |                                      | BTL mode, PVDD = 12 V, 10% THD                              |     | 9.6  |     |      |  |

|       |                                      | BTL mode, PVDD = 18 V, 7% THD                               |     | 19.8 |     |      |  |

|       |                                      | BTL mode, PVDD = 18 V, 10% THD                              |     | 20.9 |     |      |  |

|       |                                      | PBTL mode, PVDD = 12 V, $R_L$ = 4 $\Omega$ , 7% THD         |     | 17.7 |     |      |  |

| Po    | Power output per channel             | PBTL mode, PVDD = 12 V, $R_L$ = 4 $\Omega$ , 10% THD        |     | 18.7 |     | W    |  |

| 0     |                                      | PBTL mode, PVDD = 18 V, $R_L$ = 4 $\Omega$ , 7% THD         |     | 39   |     |      |  |

|       |                                      | PBTL mode, PVDD = 18 V, $R_L$ = 4 $\Omega$ , 10% THD        |     | 41.5 |     |      |  |

|       |                                      | SE Mode, PVDD = 12 V, RL = 4 Ω, 7% THD                      |     | 4.3  |     | 1    |  |

|       |                                      | SE Mode, PVDD = 12 V, RL = 4 $\Omega$ , 10% THD             |     | 4.6  |     |      |  |

|       |                                      | SE Mode, PVDD = 18 V, RL = 4 Ω, 7% THD                      |     | 16.8 |     |      |  |

|       |                                      | SE Mode, PVDD = 18 V, RL = 4 $\Omega$ , 10% THD             |     | 17.8 |     |      |  |

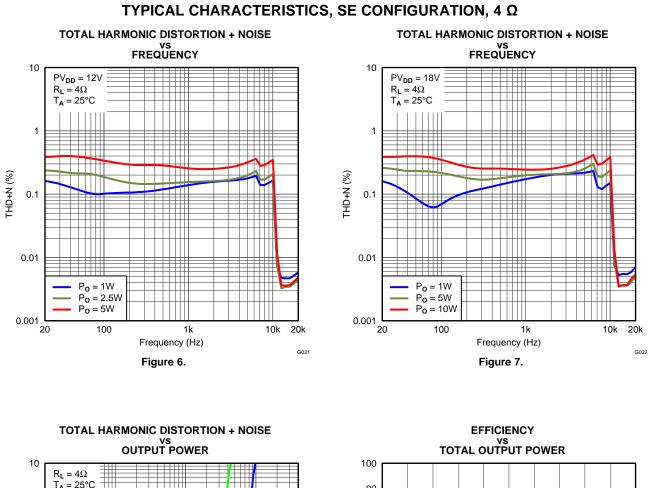

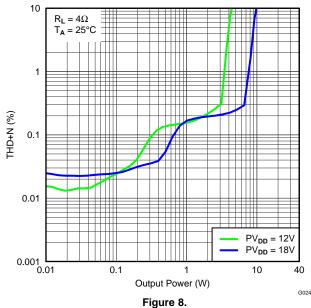

|       |                                      | PVDD = 8 V, P <sub>O</sub> = 1 W                            |     | 0.1  |     |      |  |

| THD+N | Total harmonic distortion + noise    | PVDD = 12 V, P <sub>O</sub> = 1 W                           |     | 0.07 |     | %    |  |

|       |                                      | PVDD = 18 V, P <sub>O</sub> = 1 W                           |     | 0.03 |     |      |  |

| Vn    | Output integrated noise (rms)        | A-weighted                                                  |     | 56   |     | μV   |  |

|       | Cross-talk                           | P <sub>O</sub> = 0.25 W, f = 1 kHz (AD Mode)                |     | -69  |     | dB   |  |

| SNR   | Signal-to-noise ratio <sup>(1)</sup> | A-weighted, $f = 1 \text{ kHz}$ , maximum power at THD < 1% |     | 106  |     | dB   |  |

(1) SNR is calculated relative to 0-dBFS input level.

ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

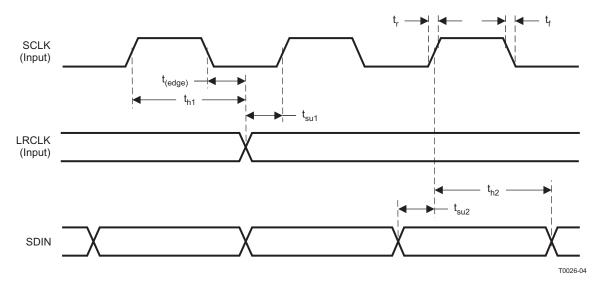

# SERIAL AUDIO PORTS SLAVE MODE

over recommended operating conditions (unless otherwise noted)

|                                | PARAMETER                                                 | TEST<br>CONDITIONS     | MIN   | TYP | МАХ    | UNIT           |

|--------------------------------|-----------------------------------------------------------|------------------------|-------|-----|--------|----------------|

| f <sub>SCLKIN</sub>            | Frequency, SCLK 32 × $f_S$ , 48 × $f_S$ , 64 × $f_S$      | C <sub>L</sub> = 30 pF | 1.024 |     | 12.288 | MHz            |

| t <sub>su1</sub>               | Setup time, LRCLK to SCLK rising edge                     |                        | 10    |     |        | ns             |

| t <sub>h1</sub>                | Hold time, LRCLK from SCLK rising edge                    |                        | 10    |     |        | ns             |

| t <sub>su2</sub>               | Setup time, SDIN to SCLK rising edge                      |                        | 10    |     |        | ns             |

| t <sub>h2</sub>                | Hold time, SDIN from SCLK rising edge                     |                        | 10    |     |        | ns             |

|                                | LRCLK frequency                                           |                        | 8     | 48  | 48     | kHz            |

|                                | SCLK duty cycle                                           |                        | 40%   | 50% | 60%    |                |

|                                | LRCLK duty cycle                                          |                        | 40%   | 50% | 60%    |                |

|                                | SCLK rising edges between LRCLK rising edges              |                        | 32    |     | 64     | SCLK<br>edges  |

| t <sub>(edge)</sub>            | LRCLK clock edge with respect to the falling edge of SCLK |                        | -1/4  |     | 1/4    | SCLK<br>period |

| t <sub>r</sub> /t <sub>f</sub> | Rise/fall time for SCLK/LRCLK                             |                        |       |     | 8      | ns             |

Figure 2. Slave-Mode Serial Data-Interface Timing

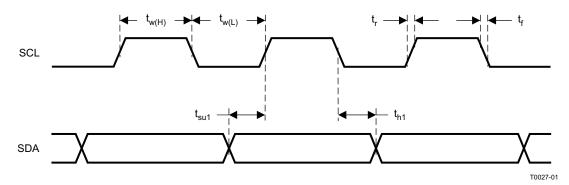

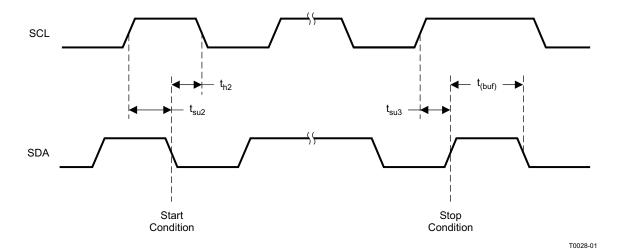

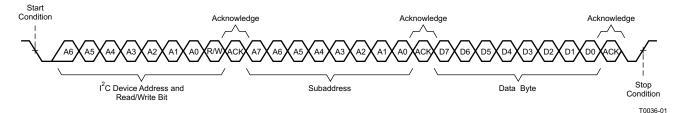

# I<sup>2</sup>C SERIAL CONTROL PORT OPERATION

Timing characteristics for I<sup>2</sup>C Interface signals over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                       | TEST CONDITIONS | MIN | MAX | UNIT |

|--------------------|-------------------------------------------------|-----------------|-----|-----|------|

| f <sub>SCL</sub>   | Frequency, SCL                                  | No wait states  |     | 400 | kHz  |

| t <sub>w(H)</sub>  | Pulse duration, SCL high                        |                 | 0.6 |     | μs   |

| t <sub>w(L)</sub>  | Pulse duration, SCL low                         |                 | 1.3 |     | μs   |

| t <sub>r</sub>     | Rise time, SCL and SDA                          |                 |     | 300 | ns   |

| t <sub>f</sub>     | Fall time, SCL and SDA                          |                 |     | 300 | ns   |

| t <sub>su1</sub>   | Setup time, SDA to SCL                          |                 | 100 |     | ns   |

| t <sub>h1</sub>    | Hold time, SCL to SDA                           |                 | 0   |     | ns   |

| t <sub>(buf)</sub> | Bus free time between stop and start conditions |                 | 1.3 |     | μs   |

| t <sub>su2</sub>   | Setup time, SCL to start condition              |                 | 0.6 |     | μs   |

| t <sub>h2</sub>    | Hold time, start condition to SCL               |                 | 0.6 |     | μs   |

| t <sub>su3</sub>   | Setup time, SCL to stop condition               |                 | 0.6 |     | μs   |

| CL                 | Load capacitance for each bus line              |                 |     | 400 | pF   |

Figure 3. SCL and SDA Timing

www.ti.com.cn

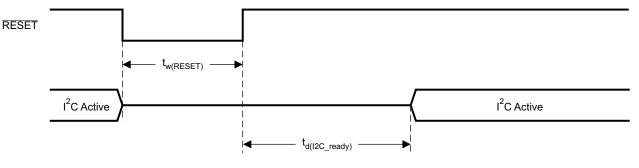

# **RESET TIMING (RESET)**

Control signal parameters over recommended operating conditions (unless otherwise noted). Please refer to Recommended Use Model section on usage of all terminals.

| Delegendenties DECET active                            |    |

|--------------------------------------------------------|----|

| t <sub>w(RESET)</sub> Pulse duration, RESET active 100 | μs |

| $t_{d(I2C\_ready)}$ Time to enable I <sup>2</sup> C 12 | ms |

System Initialization. Enable via I<sup>2</sup>C.

T0421-01

NOTES: On power up, it is recommended that the TAS5731 RESET be held LOW for at least 100 µs after DVDD has reached 3 V.

If RESET is asserted LOW while PDN is LOW, then RESET must continue to be held LOW for at least 100 µs after PDN is deasserted (HIGH).

#### Figure 5. Reset Timing

ZHCS602A – DECEMBER 2011 – REVISED SEPTEMBER 2013

ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

Figure 13.

Figure 12.

ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

## **DETAILED DESCRIPTION**

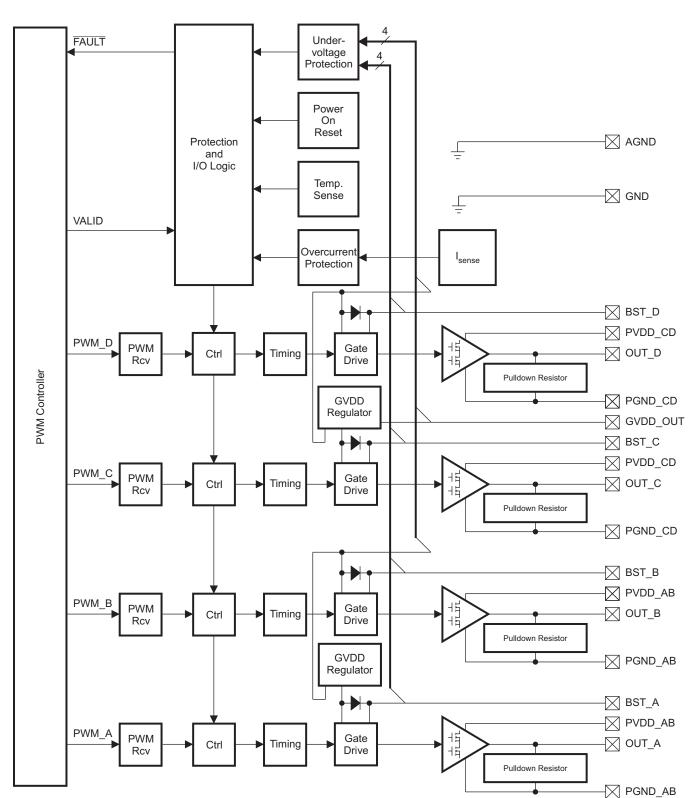

## **POWER SUPPLY**

To facilitate system design, the TAS5731 needs only a 3.3-V supply in addition to the (typical) 18-V power-stage supply. An internal voltage regulator provides suitable voltage levels for the gate drive circuitry. Additionally, all circuitry requiring a floating voltage supply, e.g., the high-side gate drive, is accommodated by built-in bootstrap circuitry requiring only a few external capacitors.

In order to provide good electrical and acoustical characteristics, the PWM signal path for the output stage is designed as identical, independent half-bridges. For this reason, each half-bridge has separate bootstrap pins (BST\_x), and power-stage supply pins (PVDD\_x). The gate-drive voltage (GVDD\_OUT) is derived from the PVDD voltage. Special attention should be paid to placing all decoupling capacitors as close to their associated pins as possible. Inductance between the power-supply pins and decoupling capacitors must be avoided.

For a properly functioning bootstrap circuit, a small ceramic capacitor must be connected from each bootstrap pin (BST\_x) to the power-stage output pin (OUT\_x). When the power-stage output is low, the bootstrap capacitor is charged through an internal diode connected between the gate-drive regulator output pin (GVDD\_OUT) and the bootstrap pin. When the power-stage output is high, the bootstrap capacitor potential is shifted above the output potential and thus provides a suitable voltage supply for the high-side gate driver. In an application with PWM switching frequencies in the range from 288 kHz to 384 kHz, it is recommended to use 33-nF, X7R ceramic capacitors, size 0603 or 0805, for the bootstrap supply. These 33-nF capacitors ensure sufficient energy storage, even during minimal PWM duty cycles, to keep the high-side power-stage FET (LDMOS) fully turned on during the remaining part of the PWM cycle.

Special attention should be paid to the power-stage power supply; this includes component selection, PCB placement, and routing. As indicated, each half-bridge has independent power-stage supply pins (PVDD\_x). For optimal electrical performance, EMI compliance, and system reliability, it is important that each PVDD\_x pin is decoupled with a 100-nF, X7R ceramic capacitor placed as close as possible to each supply pin.

The TAS5731 is fully protected against erroneous power-stage turnon due to parasitic gate charging.

#### I<sup>2</sup>C Address Selection and Fault Output

ADR/FAULT is an input pin during power up. It can be pulled HIGH or LOW through a resistor as shown in the Typical Application Circuit section in order to set the  $l^2C$  address. Pulling this pin HIGH through the resistor results in setting the  $l^2C$  7-bit address to 0011011 (0x36), and pulling it LOW through the resistor results in setting the address to 0011010 (0x34).

During power up, the address of the device is latched in, freeing up the ADR/FAULT pin to be used as a fault notification output. When configured as a fault output, the pin will go low when a fault occurs and will return to it's default state when register 0x02 is cleared. The behavior of the pin in response to a fault condition is to be pulled low immediately upon an error. The device then waits for a period of time determined by BKND\_ERR Register (0x1C) before attempting to resume playback. If the error has been cleared when the device attempts to resume playback, playback will resume, the ADR/FAULT pin will remain high, and normal operation will resume. If the error has not been removed, then the device will immediately re-enter the protected state and wait again for the predetermined period of time to pass. The device will pull the fault pin low for over-current, over-temperature, and under-voltage lock-out.

#### SINGLE-FILTER PBTL MODE

The TAS5731 supports parallel BTL (PBTL) mode with OUT\_A/OUT\_B (and OUT\_C/OUT\_D) connected before the LC filter. In order to put the part in PBTL configuration, drive PBTL (pin 8) HIGH. This synchronizes the turnoff of half-bridges A and B (and similarly C/D) if an overcurrent condition is detected in either half-bridge. There is a pulldown resistor on the PBTL pin that configures the part in BTL mode if the pin is left floating.

PWM output multiplexers should be updated to set the device in PBTL mode. Output Mux Register (0x25) should be written with a value of 0x0110 3245.

#### **DEVICE PROTECTION SYSTEM**

#### **Overcurrent (OC) Protection With Current Limiting**

The device has independent, fast-reacting current detectors on all high-side and low-side power-stage FETs. The detector outputs are closely monitored by a protection system. If the high-current condition situation persists, i.e., the power stage is being overloaded, a protection system triggers a latching shutdown, resulting in the power stage being set in the high-impedance (Hi-Z) state. The device returns to normal operation once the fault condition (i.e., a short circuit on the output) is removed. Current-limiting and overcurrent protection are not independent for half-bridges. That is, if the bridge-tied load between half-bridges A and B causes an overcurrent fault, half-bridges A, B, C, and D are shut down.

#### **Overtemperature Protection**

The TAS5731 has an overtemperature-protection system. If the device junction temperature exceeds 150°C (nominal), the device is put into thermal shutdown, resulting in all half-bridge outputs being set in the high-impedance (Hi-Z) state. The TAS5731 recovers automatically once the temperature drops approximately 30°C.

#### Undervoltage Protection (UVP) and Power-On Reset (POR)

The UVP and POR circuits of the TAS5731 fully protect the device in any power-up/down and brownout situation. While powering up, the POR circuit resets the overload circuit (OLP) and ensures that all circuits are fully operational when the PVDD and AVDD supply voltages reach 7.6 V and 2.7 V, respectively. Although PVDD and AVDD are independently monitored, a supply-voltage drop below the UVP threshold on AVDD or either PVDD pin results in all half-bridge outputs immediately being set in the high-impedance (Hi-Z) state.

#### SSTIMER FUNCTIONALITY

The SSTIMER pin uses a capacitor connected between this pin and ground to control the output duty cycle when exiting all-channel shutdown. The capacitor on the SSTIMER pin is slowly charged through an internal current source, and the charge time determines the rate at which the output transitions from a near-zero duty cycle to the desired duty cycle. This allows for a smooth transition that minimizes audible pops and clicks. When the part is shut down, the drivers are placed in the high-impedance state and transition slowly down through a 3-k $\Omega$  resistor, similarly minimizing pops and clicks. The shutdown transition time is independent of the SSTIMER pin capacitance. Larger capacitors increase the start-up time, while capacitors smaller than 2.2 nF decrease the start-up time. The SSTIMER pin should be left floating for BD modulation.

## CLOCK, AUTODETECTION, AND PLL

The TAS5731 is an I<sup>2</sup>S slave device. It accepts MCLK, SCLK, and LRCLK. The digital audio processor (DAP) supports all the sample rates and MCLK rates that are defined in the clock control register.

The TAS5731 checks to verify that SCLK is a specific value of 32  $f_S$ , 48  $f_S$ , or 64  $f_S$ . The DAP only supports a 1 x  $f_S$  LRCLK. The timing relationship of these clocks to SDIN is shown in subsequent sections. The clock section uses MCLK or the internal oscillator clock (when MCLK is unstable, out of range, or absent) to produce the internal clock (DCLK) running at 512 times the PWM switching frequency.

The DAP can autodetect and set the internal clock control logic to the appropriate settings for all supported clock rates as defined in the clock-control register.

The TAS5731 has robust clock error handling that uses the built-in trimmed oscillator clock to quickly detect changes/errors. Once the system detects a clock change/error, it mutes the audio (through a single-step mute) and then forces PLL to limp using the internal oscillator as a reference clock. Once the clocks are stable, the system autodetects the new rate and reverts to normal operation. During this process, the default volume is restored in a single step (also called hard unmute). The ramp process can be programmed to ramp back slowly (also called soft unmute) as defined in volume register (0x0E).

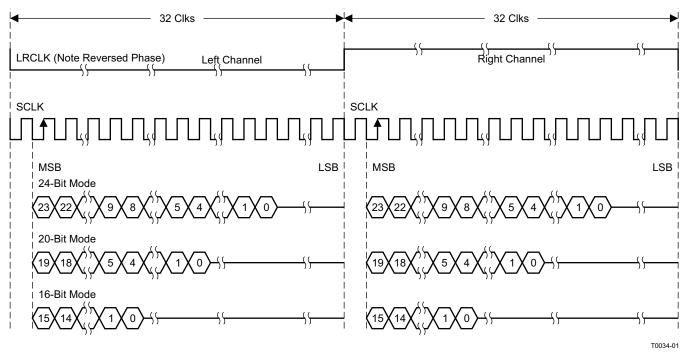

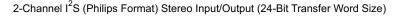

#### SERIAL DATA INTERFACE

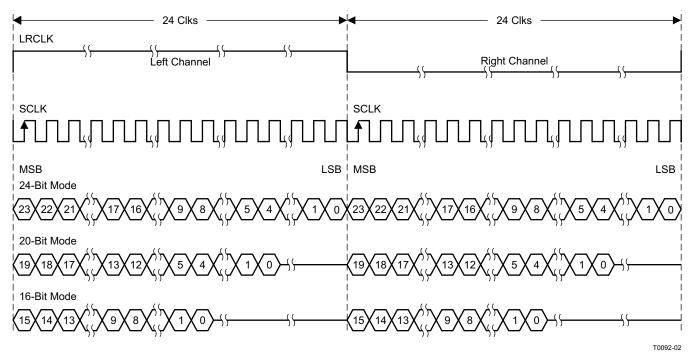

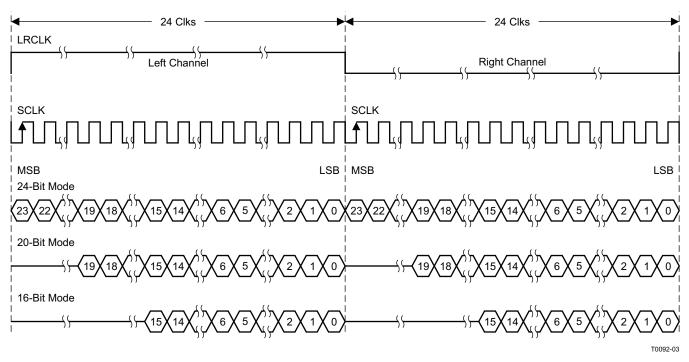

Serial data is input on SDIN. The PWM outputs are derived from SDIN. The TAS5731 DAP accepts serial data in 16-, 20-, or 24-bit left-justified, right-justified, and I<sup>2</sup>S serial data formats.

#### **PWM SECTION**

The TAS5731 DAP device uses noise-shaping and customized nonlinear correction algorithms to achieve high power efficiency and high-performance digital audio reproduction. The DAP uses a fourth-order noise shaper to increase dynamic range and SNR in the audio band. The PWM section accepts 24-bit PCM data from the DAP and outputs two BTL PWM audio output channels.

The PWM section has individual-channel dc-blocking filters that can be enabled and disabled. The filter cutoff frequency is less than 1 Hz. Individual-channel de-emphasis filters for 44.1 kHz and 48 kHz are included and can be enabled and disabled.

Finally, the PWM section has an adjustable maximum modulation limit of 93.8% to 99.2%.

For a detailed description of using audio processing features like DRC and EQ, see the User's Guide and TAS570X GDE software development tool documentation.

TAS5731

www.ti.com.cn

#### SERIAL INTERFACE CONTROL AND TIMING

#### I<sup>2</sup>S Timing

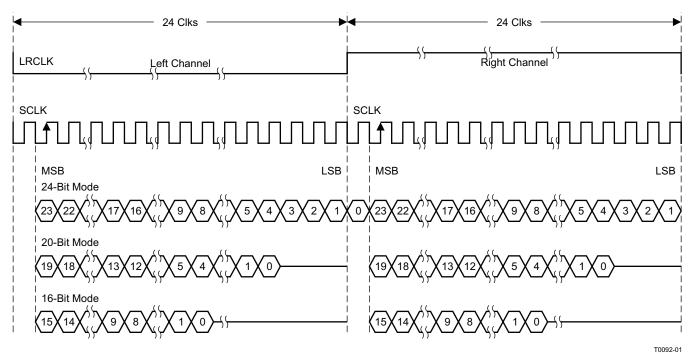

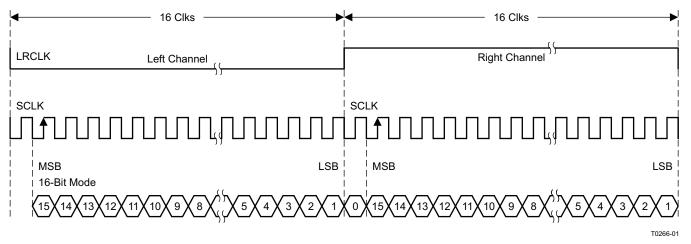

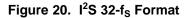

$I^2S$  timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is low for the left channel and high for the right channel. A bit clock running at 32, 48, or 64 × f<sub>S</sub> is used to clock in the data. There is a delay of one bit clock from the time the LRCLK signal changes state to the first bit of data on the data lines. The data is written MSB-first and is valid on the rising edge of bit clock. The DAP masks unused trailing data bit positions.

2-Channel I<sup>2</sup>S (Philips Format) Stereo Input

NOTE: All data presented in 2s-complement form with MSB first.

Figure 18. I<sup>2</sup>S 64-f<sub>S</sub> Format

Texas Instruments

www.ti.com.cn

NOTE: All data presented in 2s-complement form with MSB first.

Figure 19. I<sup>2</sup>S 48-f<sub>S</sub> Format

2-Channel I<sup>2</sup>S (Philips Format) Stereo Input

NOTE: All data presented in 2s-complement form with MSB first.

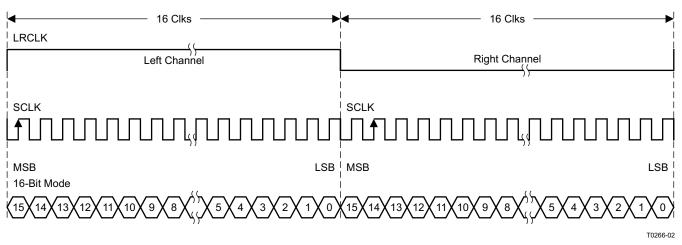

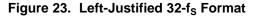

## Left-Justified

Left-justified (LJ) timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is high for the left channel and low for the right channel. A bit clock running at 32, 48, or  $64 \times f_S$  is used to clock in the data. The first bit of data appears on the data lines at the same time LRCLK toggles. The data is written MSB-first and is valid on the rising edge of the bit clock. The DAP masks unused trailing data bit positions.

ZHCS602A - DECEMBER 2011 - REVISED SEPTEMBER 2013

2-Channel Left-Justified Stereo Input

NOTE: All data presented in 2s-complement form with MSB first.

#### Figure 21. Left-Justified 64-f<sub>s</sub> Format

2-Channel Left-Justified Stereo Input (24-Bit Transfer Word Size)

NOTE: All data presented in 2s-complement form with MSB first.

#### Figure 22. Left-Justified 48-f<sub>S</sub> Format

www.ti.com.cn

2-Channel Left-Justified Stereo Input

NOTE: All data presented in 2s-complement form with MSB first.

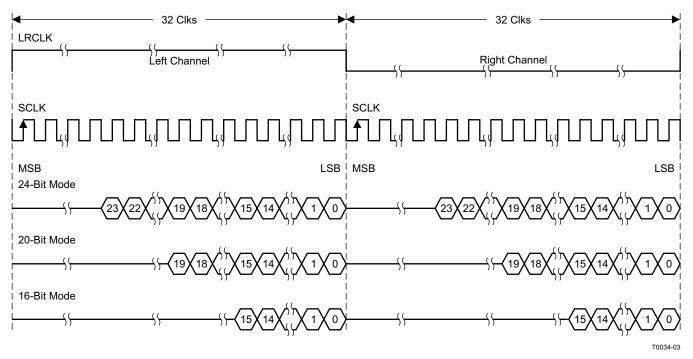

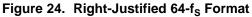

#### **Right-Justified**

Right-justified (RJ) timing uses LRCLK to define when the data being transmitted is for the left channel and when it is for the right channel. LRCLK is high for the left channel and low for the right channel. A bit clock running at 32, 48, or  $64 \times f_S$  is used to clock in the data. The first bit of data appears on the data 8 bit-clock periods (for 24-bit data) after LRCLK toggles. In RJ mode, the LSB of data is always clocked by the last bit clock before LRCLK transitions. The data is written MSB-first and is valid on the rising edge of bit clock. The DAP masks unused leading data bit positions.

2-Channel Right-Justified (Sony Format) Stereo Input

ZHCS602A – DECEMBER 2011 – REVISED SEPTEMBER 2013

2-Channel Right-Justified Stereo Input (24-Bit Transfer Word Size)

2-Channel Right-Justified (Sony Format) Stereo Input

Figure 26. Right-Justified 32-f<sub>S</sub> Format

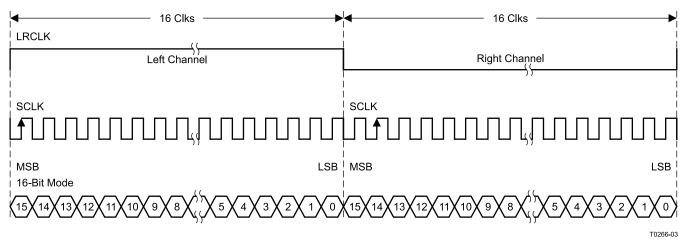

## I<sup>2</sup>C SERIAL CONTROL INTERFACE

The TAS5731 DAP has a bidirectional  $I^2C$  interface that is compatible with the Inter IC ( $I^2C$ ) bus protocol and supports both 100-kHz and 400-kHz data transfer rates for single- and multiple-byte write and read operations. This is a slave-only device that does not support a multimaster bus environment or wait-state insertion. The control interface is used to program the registers of the device and to read device status.

The DAP supports the standard-mode  $I^2C$  bus operation (100 kHz maximum) and the fast  $I^2C$  bus operation (400 kHz maximum). The DAP performs all  $I^2C$  operations without  $I^2C$  wait cycles.

#### General I<sup>2</sup>C Operation

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially, one bit at a time. The address and data can be transferred in byte (8-bit) format, with the most-significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus and ends with the master device driving a stop condition on the bus and ends with the master device driving a stop condition. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period. These conditions are shown in Figure 27. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The TAS5731 holds SDA low during the acknowledge clock period to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pullup resistor must be used for the SDA and SCL signals to set the high level for the bus.

#### Figure 27. Typical I<sup>2</sup>C Sequence

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in Figure 27.

The 7-bit address for TAS5731 is 0011 011 (0x36).

#### Single- and Multiple-Byte Transfers

The serial control interface supports both single-byte and multiple-byte read/write operations for subaddresses 0x00 to 0x1F. However, for the subaddresses 0x20 to 0xFF, the serial control interface supports only multiple-byte read/write operations (in multiples of 4 bytes).

During multiple-byte read operations, the DAP responds with data, a byte at a time, starting at the subaddress assigned, as long as the master device continues to respond with acknowledges. If a particular subaddress does not contain 32 bits, the unused bits are read as logic 0.

During multiple-byte write operations, the DAP compares the number of bytes transmitted to the number of bytes that are required for each specific subaddress. For example, if a write command is received for a biquad subaddress, the DAP must receive five 32-bit words. If fewer than five 32-bit data words have been received when a stop command (or another start command) is received, the received data is discarded.

#### ZHCS602A – DECEMBER 2011 – REVISED SEPTEMBER 2013

Supplying a subaddress for each subaddress transaction is referred to as random I<sup>2</sup>C addressing. The TAS5731 also supports sequential I<sup>2</sup>C addressing. For write transactions, if a subaddress is issued followed by data for that subaddress and the 15 subaddresses that follow, a sequential I<sup>2</sup>C write transaction has taken place, and the data for all 16 subaddresses is successfully received by the TAS5731. For I<sup>2</sup>C sequential-write transactions, the subaddress then serves as the start address, and the amount of data subsequently transmitted, before a stop or start is transmitted, determines how many subaddresses are written. As was true for random addressing, sequential addressing requires that a complete set of data be transmitted. If only a partial set of data is written to the last subaddress is discarded. However, all other data written is accepted; only the incomplete data is discarded.

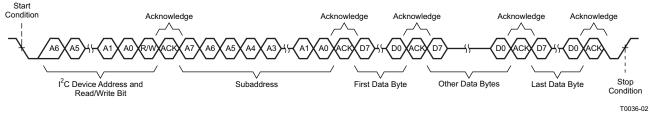

#### Single-Byte Write

As shown in Figure 28, a single-byte data-write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a data-write transfer, the read/write bit is a 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the DAP responds with an acknowledge bit. Next, the master transmits the address byte or bytes corresponding to the TAS5731 internal memory address being accessed. After receiving the address byte, the TAS5731 again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the data byte to be written to the memory address being accessed. After receiving the data byte, the TAS5731 again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data-write transfer.

Figure 28. Single-Byte Write Transfer

#### **Multiple-Byte Write**

A multiple-byte data-write transfer is identical to a single-byte data-write transfer except that multiple data bytes are transmitted by the master device to the DAP as shown in Figure 29. After receiving each data byte, the TAS5731 responds with an acknowledge bit.

Figure 29. Multiple-Byte Write Transfer

TEXAS INSTRUMENTS

www.ti.com.cn

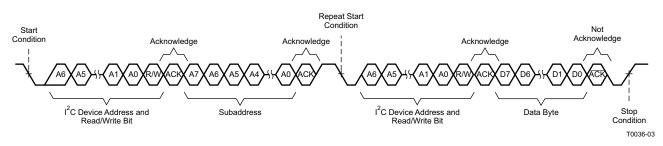

#### Single-Byte Read

As shown in Figure 30, a single-byte data-read transfer begins with the master device transmitting a start condition, followed by the I<sup>2</sup>C device address and the read/write bit. For the data read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte or bytes of the internal memory address to be read. As a result, the read/write bit becomes a 0. After receiving the TAS5731 address and the read/write bit, TAS5731 responds with an acknowledge bit. In addition, after sending the internal memory address byte or bytes, the master device transmits another start condition followed by the TAS5731 address and the read/write bit again. This time, the read/write bit becomes a 1, indicating a read transfer. After receiving the address and the read/write bit, the TAS5731 again responds with an acknowledge bit. Next, the TAS5731 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the single-byte data-read transfer.

Figure 30. Single-Byte Read Transfer

#### **Multiple-Byte Read**

A multiple-byte data-read transfer is identical to a single-byte data-read transfer except that multiple data bytes are transmitted by the TAS5731 to the master device as shown in Figure 31. Except for the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

Figure 31. Multiple-Byte Read Transfer

#### www.ti.com.cn

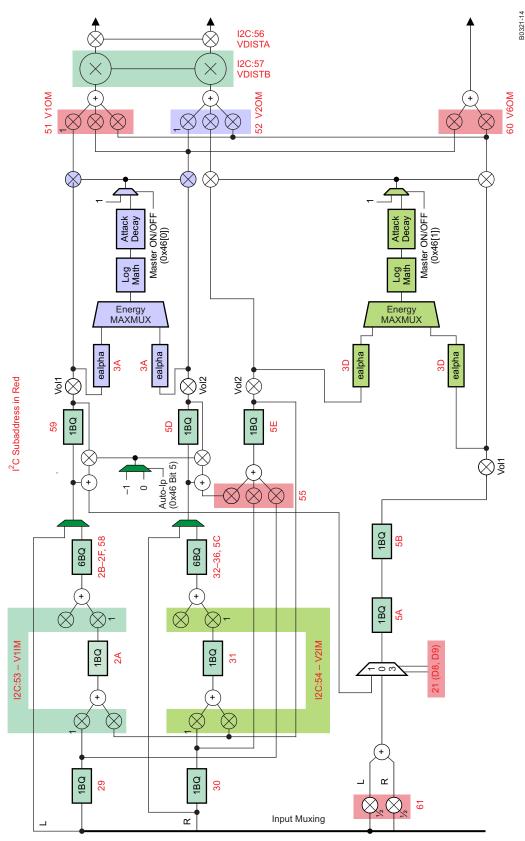

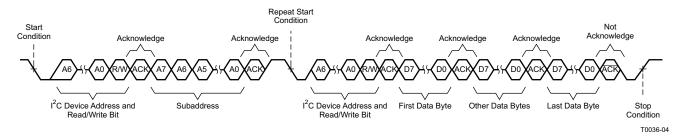

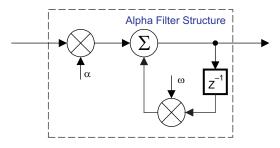

#### **Dynamic Range Control (DRC)**

The DRC scheme has two DRC blocks. There is one ganged DRC for the high-band left/right channels and one DRC for the low-band left/right channels.

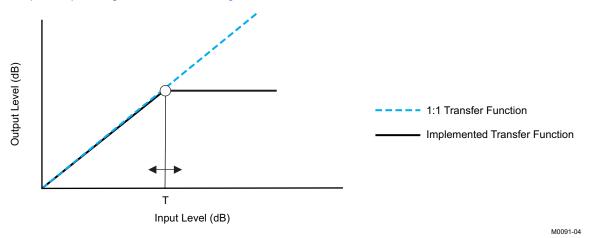

The DRC input/output diagram is shown in Figure 32.

Professional-quality dynamic range compression automatically adjusts volume to flatten volume level.

- Each DRC has adjustable threshold levels.

- Programmable attack and decay time constants

- Transparent compression: compressors can attack fast enough to avoid apparent clipping before engaging, and decay times can be set slow enough to avoid pumping.

#### Figure 32. Dynamic Range Control

|      | α, ω | Т    | $\alpha_{a}, \omega_{a} / \alpha_{d}, \omega_{d}$ |

|------|------|------|---------------------------------------------------|

| DRC1 | 0x3C | 0x3B | 0x40                                              |

| DRC2 | 0x3F | 0x3E | 0x43                                              |

B0265-04

T = 9.23 format, all other DRC coefficients are 3.23 format

#### Figure 33. DRC Structure

## **PWM LEVEL METER**

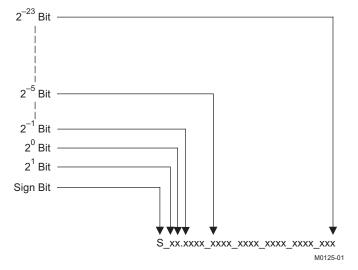

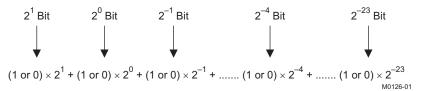

### 26-Bit 3.23 Number Format

All mixer gain coefficients are 26-bit coefficients using a 3.23 number format. Numbers formatted as 3.23 numbers means that there are 3 bits to the left of the binary point and 23 bits to the right of the binary point. This is shown in Figure 34.

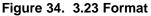

The decimal value of a 3.23 format number can be found by following the weighting shown in Figure 34. If the most significant bit is logic 0, the number is a positive number, and the weighting shown yields the correct number. If the most significant bit is a logic 1, then the number is a negative number. In this case every bit must be inverted, a 1 added to the result, and then the weighting shown in Figure 35 applied to obtain the magnitude of the negative number.

Figure 35. Conversion Weighting Factors—3.23 Format to Floating Point

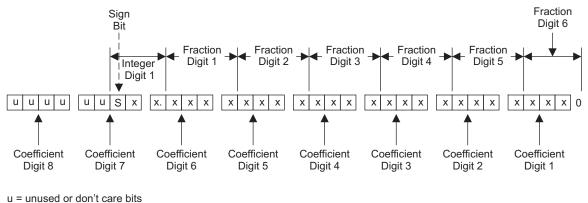

Gain coefficients, entered via the  $l^2C$  bus, must be entered as 32-bit binary numbers. The format of the 32-bit number (4-byte or 8-digit hexadecimal number) is shown in Figure 36.

Digit = hexadecimal digit

M0127-01

#### Figure 36. Alignment of 3.23 Coefficient in 32-Bit I<sup>2</sup>C Word

| db | Linear            | Decimal           | Hex (3.23 Format)  |

|----|-------------------|-------------------|--------------------|

| 0  | 1                 | 8,388,608         | 80 0000            |

| 5  | 1.77              | 14,917,288        | 00E3 9EA8          |

| -5 | 0.56              | 4,717,260         | 0047 FACC          |

| Х  | $L = 10^{(X/20)}$ | D = 8,388,608 × L | H = dec2hex (D, 8) |

#### Table 1. Sample Calculation for 3.23 Format

#### Table 2. Sample Calculation for 9.17 Format

| db | Linear            | Decimal         | Hex (9.17 Format)  |

|----|-------------------|-----------------|--------------------|

| 0  | 1                 | 131,072         | 2 0000             |

| 5  | 1.77              | 231,997         | 3 8A3D             |

| -5 | 0.56              | 73,400          | 1 1EB8             |

| Х  | $L = 10^{(X/20)}$ | D = 131,072 × L | H = dec2hex (D, 8) |

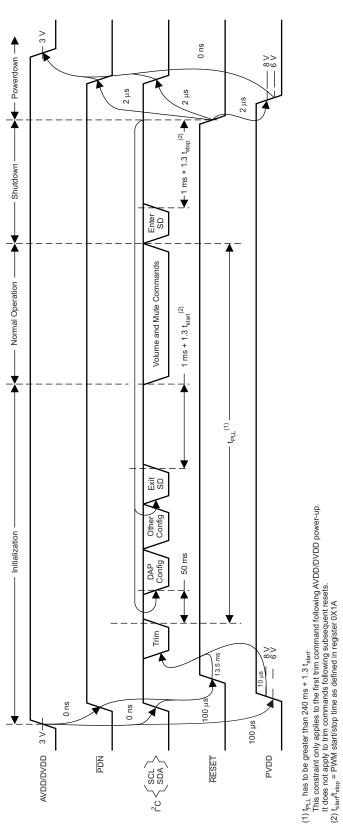

### Recommended Use Model

T0419-06

www.ti.com.cn

Figure 37. Recommended Command Sequence

Figure 38. Power-Loss Sequence

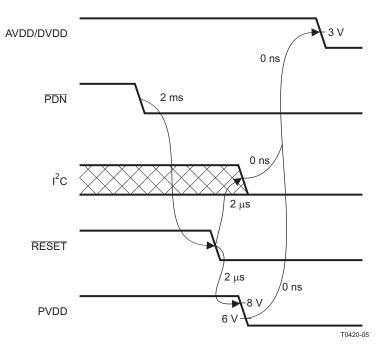

#### **Initialization Sequence**

Use the following sequence to power up and initialize the device:

- 1. Hold all digital inputs low and ramp up AVDD/DVDD to at least 3 V.

- 2. Initialize digital inputs and PVDD supply as follows:

- Drive  $\overline{\text{RESET}} = 0$ ,  $\overline{\text{PDN}} = 1$ , and other digital inputs to their desired state while ensuring that all are never more than 2.5 V above AVDD/DVDD. Wait at least 100 µs, drive  $\overline{\text{RESET}} = 1$ , and wait at least another 13.5 ms.

- Ramp up PVDD to at least 8 V while ensuring that it remains below 6 V for at least 100 µs after AVDD/DVDD reaches 3 V. Then wait at least another 10 µs.

- 3. Trim oscillator (write 0x00 to register 0x1B) and wait at least 50 ms.

- 4. Configure the DAP via I<sup>2</sup>C (see User's Guide for typical values).

- 5. Configure remaining registers.

- 6. Exit shutdown (sequence defined below).

#### **Normal Operation**

The following are the only events supported during normal operation:

- 1. Writes to master/channel volume registers

- 2. Writes to soft-mute register

- 3. Enter and exit shutdown (sequence defined below)

**Note:** Event 3 is not supported for 240 ms +  $1.3 \times t_{start}$  after trim following AVDD/DVDD power-up ramp (where  $t_{start}$  is specified by register 0x1A).

#### Shutdown Sequence

#### Enter:

- 1. Write 0x40 to register 0x05.

- 2. Wait at least 1 ms + 1.3 ×  $t_{stop}$  (where  $t_{stop}$  is specified by register 0x1A).

- 3. If desired, reconfigure by returning to step 4 of initialization sequence.

#### Exit:

- 1. Write 0x00 to register 0x05 (exit shutdown command may not be serviced for as much as 240 ms after trim following AVDD/DVDD power-up ramp).

- 2. Wait at least 1 ms + 1.3 ×  $t_{start}$  (where  $t_{start}$  is specified by register 0x1A).

- 3. Proceed with normal operation.

#### Power-Down Sequence

Use the following sequence to power down the device and its supplies:

- 1. If time permits, enter shutdown (sequence defined above); else, in case of sudden power loss, assert PDN = 0 and wait at least 2 ms.

- 2. Assert  $\overline{\text{RESET}} = 0$ .

- 3. Drive digital inputs low and ramp down PVDD supply as follows:

- Drive all digital inputs low after  $\overline{\text{RESET}}$  has been low for at least 2 µs.

- Ramp down PVDD while ensuring that it remains above 8 V until RESET has been low for at least 2 µs.

- 4. Ramp down AVDD/DVDD while ensuring that it remains above 3 V until PVDD is below 6 V and that it is never more than 2.5 V below the digital inputs.

#### www.ti.com.cn

# Table 3. Serial Control Interface Register Summary

| SUBADDRESS | REGISTER NAME                          | NO. OF<br>BYTES | CONTENTS                                | INITIALIZATION<br>VALUE |

|------------|----------------------------------------|-----------------|-----------------------------------------|-------------------------|

|            |                                        |                 | A u indicates unused bits.              |                         |

| 0x00       | Clock control register                 | 1               | Description shown in subsequent section | 0x6C                    |

| 0x01       | Device ID register                     | 1               | Description shown in subsequent section | 0x00                    |

| 0x02       | Error status register                  | 1               | Description shown in subsequent section | 0x00                    |

| 0x03       | System control register 1              | 1               | Description shown in subsequent section | 0xA0                    |

| 0x04       | Serial data interface<br>register      | 1               | Description shown in subsequent section | 0x05                    |

| 0x05       | System control register 2              | 1               | Description shown in subsequent section | 0x40                    |

| 0x06       | Soft mute register                     | 1               | Description shown in subsequent section | 0x00                    |

| 0x07       | Master volume                          | 1               | Description shown in subsequent section | 0xFF (mute)             |

| 0x08       | Channel 1 vol                          | 1               | Description shown in subsequent section | 0x30 (0 dB)             |

| 0x09       | Channel 2 vol                          | 1               | Description shown in subsequent section | 0x30 (0 dB)             |

| 0x0A       | Channel 3 vol                          | 1               | Description shown in subsequent section | 0x30 (0 dB)             |

| 0x0B-0x0D  |                                        | 1               | Reserved <sup>(1)</sup>                 |                         |

| 0x0E       | Volume configuration register          | 1               | Description shown in subsequent section | 0x91                    |

| 0x0F       |                                        | 1               | Reserved <sup>(1)</sup>                 |                         |

| 0x10       | Modulation limit register              | 1               | Description shown in subsequent section | 0x02                    |

| 0x11       | IC delay channel 1                     | 1               | Description shown in subsequent section | 0xAC                    |

| 0x12       | IC delay channel 2                     | 1               | Description shown in subsequent section | 0x54                    |

| 0x13       | IC delay channel 3                     | 1               | Description shown in subsequent section | 0xAC                    |

| 0x14       | IC delay channel 4                     | 1               | Description shown in subsequent section | 0x54                    |

| 0x15-0x18  |                                        | 1               | Reserved <sup>(1)</sup>                 |                         |