- Two Independent Controllers for Regulation of:

- Fixed 2.5-V and an Adjustable Output

- ±2% (Max) Regulation Across

Temperature and Load (1 mA to 3 A)

- Adjustable Output Can Be Set Via an External Reference Pin, Allowing for the Creation of a Tracking Regulator

- Great Design Flexibility With Minimal External Components

- Applications: High-Current, Low-Dropout Regulators for:

- DDR/RDRAM Memory Termination

- Motherboards

- Chipset I/O

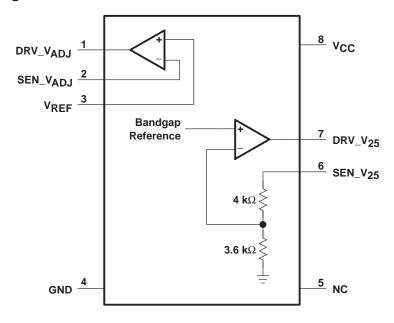

- GTLP Termination

# D OR PW PACKAGE (TOP VIEW) DRV\_V<sub>ADJ</sub> 1 8 V<sub>CC</sub> SEN\_V<sub>ADJ</sub> 2 7 DRV\_V<sub>25</sub> V<sub>REF</sub> 3 6 SEN\_V<sub>25</sub> GND 4 5 NC

NC - No internal connection

# description/ordering information

The LFC789D25 is a dual linear FET controller that simplifies the design of dual power supplies. The device consists of two independent controllers, each of which drives an external MOSFET to implement a low-dropout regulator. One controller is programmed to regulate a fixed 2.5-V output, while the second controller can be programmed to regulate any desired output voltage via a reference input pin, allowing for the creation of a tracking regulator often needed for termination schemes. And, because heating effects of the external FETs easily can be isolated from the controllers, the controllers can regulate the output voltages to a maximum tolerance of  $\pm 2\%$  across temperature and load.

The LFC789D25 allows designers a great deal of flexibility in selecting external components and topology to implement their specific power-supply needs. With appropriate heat sinking, the designer can build a regulator with as much current capability as allowed by the external MOSFET and power supply. And, because the dropout of the regulator simply is the product of the  $R_{DS(on)}$  of the external power MOSFET and the load current, very low dropout can be achieved via proper selection of the power MOSFET.

Packaged in 8-pin SOIC and space-saving TSSOP, the LFC789D25 is characterized for operation from 0°C to 70°C.

#### ORDERING INFORMATION

| TA          | PACKAC     | ∋E†          | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|-------------|------------|--------------|--------------------------|---------------------|

|             | 0010 (P)   | Tube of 75   | LFC789D25CD              | KADAO               |

| 0°C to 70°C | SOIC (D)   | Reel of 2500 | LFC789D25CDR             | KADAC               |

| 0 0 10 70 0 | TCCOD (DW) | Tube of 150  | LFC789D25CPW             | KADAC               |

|             | TSSOP (PW) | Reel of 2000 | LFC789D25CPWR            | KADAC               |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# functional block diagram

# PIN DESCRIPTION

| PIN | PIN NAME             | PIN FUNCTION                                                                                                |

|-----|----------------------|-------------------------------------------------------------------------------------------------------------|

| 1   | DRV_V <sub>ADJ</sub> | Output of adjustable controller. Drives gate(s) of FET(s) to output user-programmable voltage (VADJ).       |

| 2   | SEN_V <sub>ADJ</sub> | Sense input of adjustable controller. Senses changes in V <sub>ADJ</sub> .                                  |

| 3   | V <sub>REF</sub>     | Input pin used to program V <sub>ADJ</sub> , allowing V <sub>ADJ</sub> to track changes in V <sub>REF</sub> |

| 4   | GND                  | Ground                                                                                                      |

| 5   | NC                   | No connection                                                                                               |

| 6   | SEN_V <sub>25</sub>  | Sense Input of 2.5-V controller. Senses changes in 2.5-V supply.                                            |

| 7   | DRV_V <sub>25</sub>  | Output of 2.5-V controller. Drives gate(s) of FET(s) to output fixed 2.5 V.                                 |

| 8   | Vcc                  | Power supply for device                                                                                     |

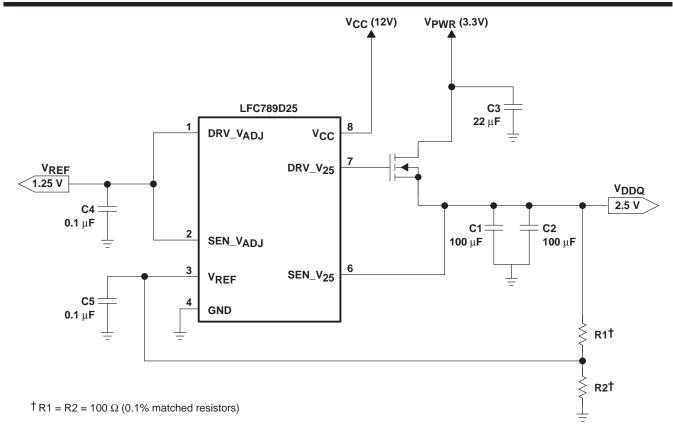

Figure 1. Typical Application Circuit for DDR1 - Memory Voltage (VDDQ) and VREF Buffer for DIMMs

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡

| Supply voltage, V <sub>CC</sub> (see Note 1)                                        | 18 V           |

|-------------------------------------------------------------------------------------|----------------|

| Input voltage range, V <sub>RFF</sub> , SEN_V <sub>AD,I</sub> , SEN_V <sub>25</sub> | -0.3 V to 18 V |

| Package thermal impedance, θ <sub>JA</sub> (see Notes 2 and 3): D package           | 97°C/W         |

| PW package                                                                          | 149°C/W        |

| Operating virtual junction temperature, T <sub>J</sub>                              | 150°C          |

| Storage temperature range, T <sub>stg</sub>                                         |                |

<sup>‡</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All voltage values are with respect to the network ground terminal.

- 2. Maximum power dissipation is a function of  $T_J(max)$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = (T_J(max) T_A)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of 150°C can impact reliability.

- 3. The package thermal impedance is calculated in accordance with JESD 51-7.

# recommended operating conditions

|     |                                | MIN | MAX | UNIT |

|-----|--------------------------------|-----|-----|------|

| VCC | Supply voltage                 | 9   | 16  | V    |

| TA  | Operating free-air temperature | 0   | 70  | °C   |

# LFC789D25 DUAL LINEAR FET CONTROLLER

SLLS565B - MARCH 2003 - REVISED SEPTEMBER 2004

# electrical characteristics, $V_{CC}$ = 12 V $\pm$ 5%, $T_{A}$ = 25°C (unless otherwise noted)

|                                  | PARAM                 | ETER                                       | TEST CONDITIONS                                     | TA                   | MIN                        | TYP              | MAX                        | UNIT |  |

|----------------------------------|-----------------------|--------------------------------------------|-----------------------------------------------------|----------------------|----------------------------|------------------|----------------------------|------|--|

|                                  |                       | V conce nin current                        |                                                     |                      |                            | -20              |                            | ~ A  |  |

| Sense                            | I <sub>SEN_VADJ</sub> | V <sub>ADJ</sub> sense-pin current         |                                                     | Full range           |                            |                  | -500                       | nA   |  |

| Sense                            | ١,                    | Va- conce pin current                      | Vo 25 V                                             |                      |                            | 125              |                            | μА   |  |

|                                  | SEN_V <sub>25</sub>   | V <sub>25</sub> sense-pin current          | V <sub>25</sub> = 2.5 V                             | Full range           |                            |                  | 500                        | μΑ   |  |

|                                  | V <sub>DRV</sub>      | Driver output voltage                      | I <sub>DRV</sub> = 0                                |                      | V <sub>C</sub> C<br>– 1.5  |                  |                            | V    |  |

| Driver                           |                       |                                            | Full range                                          | V <sub>C</sub> C – 3 |                            |                  |                            |      |  |

|                                  |                       | Duit can acuta cut accumant                | V <sub>DRV</sub> = 4 V,                             |                      |                            | 10               |                            | mA   |  |

|                                  | IDRV                  | Driver output current                      | V <sub>SEN</sub> = 0.8 V <sub>OUT</sub> (nom)       | Full range           | 5                          |                  |                            |      |  |

| Deference                        | ١,                    | Din ourrant \/                             | ,                                                   |                      |                            | -20              | -250                       | ~^   |  |

| Reference                        | I <sub>VREF</sub>     | Pin current, V <sub>REF</sub>              |                                                     | Full range           |                            |                  | -500                       | nA   |  |

|                                  |                       | V <sub>25</sub> output voltage             | $I_{OUT} = 1 \text{ mA to } 3 \text{ A},$           |                      |                            | 2.5              |                            |      |  |

| Output roout                     | lation                | regulation                                 | $V_{PWR} = 3.3 V \pm 10\%$                          | Full range           | 2.45                       | 2.5              | 2.55                       |      |  |

| Output regulation (see Figure 1) | V output voltage      | I <sub>OUT</sub> = 1 mA to 2 A,            |                                                     |                      | $V_{REF}$                  |                  | V                          |      |  |

|                                  | ,                     | V <sub>ADJ</sub> output voltage regulation | $V_{PWR} = 3.3 V \pm 10\%,$<br>$V_{REF} = V_{25}/2$ | Full range           | 0.98 ×<br>V <sub>REF</sub> | V <sub>REF</sub> | 1.02 ×<br>V <sub>REF</sub> |      |  |

| Supply                           | laa                   | Supply current                             |                                                     |                      |                            | 2                |                            | mA   |  |

| Supply                           | Icc                   | Supply current                             |                                                     | Full range           |                            |                  | 2.5                        | IIIA |  |

#### **APPLICATION INFORMATION**

#### **FUNCTIONAL DESCRIPTION**

A linear voltage regulator can be broken down into four essential building blocks: a pass transistor, a voltage reference, a feedback network, and a control circuit to drive the pass element, based on the comparison between the output voltage (as sampled by the feedback network) and the voltage reference. With the exception of the pass transistor, the -ADJ provides the other three building blocks needed. Thus, with minimal external components and low overall solution cost, a designer can create two independent, tightly regulated output voltages capable of delivering high currents in excess of 3 A (as limited by the external pass transistor). One output is fixed at 2.5 V. The other output can be adjusted to any desired voltage via an externally applied signal to the V<sub>REF</sub> pin. Because the output of the regulator always tracks any changes to this V<sub>REF</sub> pin, it is relatively easy to implement a tracking regulator. See the *typical application circuit* (Figure 1).

#### internal reference

The fixed 2.5-V output controller uses an internal temperature-compensated bandgap reference centered at 1.2 V. Its tolerance is designed to be <±2% over the specified temperature range, which, when coupled with the low offset of the driver circuit, allows the 2.5-V output to have a tolerance of 2% over the specified temperature range and full load.

## external reference pin (V<sub>REF</sub>)

For the adjustable output controller, the  $V_{REF}$  pin allows great flexibility for the designer. Taking a simple resistor divider tied to an external voltage source and connecting the divider to the  $V_{REF}$  pin allows the controller to regulate an output voltage that is some fraction of the external voltage source. And, because any changes in the external voltage source are sensed by the voltage divider, the regulated output tracks those changes.

If a tracking regulator is not desired, a fixed voltage can be achieved by applying a constant voltage to the V<sub>REF</sub> pin. This signal can be provided by a simple device such as the TL431 adjustable shunt regulator.

The  $V_{REF}$  pin typically *sources* a current of 20 nA and, as such, has a minimal loading effect on the resistor divider or the shunt regulator. The accuracy of the adjustable output depends on the accuracy of the signal applied to the  $V_{REF}$  pin. Using high-precision resistors or a TL431A (1% output tolerance) helps achieve good accuracy.

## feedback network (SENSE pins)

The 2.5-V controller senses the output voltage via the SEN\_V<sub>25</sub> pin. This pin is tied to an internal resistor divider that essentially halves the sensed output voltage and feeds it back to the controller for comparison to the internal bandgap reference.

For the adjustable output controller, the SEN\_V<sub>ADJ</sub> pin provides direct feedback of the output voltage to the controller for comparison to the externally applied V<sub>RFF</sub> signal.

## controller/driver

Both drivers essentially are error amplifiers that can output a worst-case minimum of 9 V (10.5 V at 25°C) when the LFC789D25 is powered by 12 V. This allows the controllers to regulate a large range of output voltages, as limited by the threshold voltages of the external NMOS. Both drivers sample the output voltage via a SEN pin. For the adjustable version, this SEN pin typically *sources* a current of 20 nA and, thus, has minimal loading on the output voltage. For the 2.5-V version, this SEN pin *sinks* a current of approximately 125  $\mu$ A (including the currents through the internal resistor divider); this results in minimal loading on the output voltage.

Although not tested, both of these controllers are designed with very low offset (typically less than 4 mV), resulting in very accurate control of the drive signals.

#### **APPLICATION INFORMATION**

#### MOSFET SELECTION: BENEFITS OF NMOS PASS ELEMENTS REVISITED

A great benefit of having an external pass element is that the control circuitry can be powered by a separate supply ( $V_{CC}$ ), other than the one used as the input to the pass element ( $V_{PWR}$ ). This feature allows the use of an NMOS pass element, which requires a positive  $V_{GS} > V_T$  for operation. With a separate  $V_{CC}$  pin to the controller, the voltage at the gate of the NMOS readily can exceed the voltage at the drain; thus,  $V_{GS}$  easily can exceed  $V_{DS} + V_T$ , allowing the NMOS to operate in the triode region ( $V_{DS} \ge V_{GS} - V_T$ ). In the triode region,  $V_{DS}$  can be very small, thus achieving very low dropout.

The external NMOS selected for the pass transistor has significant impact on the overall characteristics of the regulator, as discussed in the following paragraphs.

# Maximum output current

A benefit of an external pass element is that the designer can size the NMOS to easily sustain the maximum I<sub>OUT</sub> expected. This allows great flexibility, along with cost and space savings, because each regulator has its pass element tailored to its individual needs. In addition, using an NMOS pass element allows for smaller size (and subsequently, lower cost) than a PMOS element for the same current-carrying ability.

#### Dropout

Choosing an NMOS with very low  $R_{DS(on)}$  characteristics provides the regulator with very low dropout because dropout will be  $\sim I_{OUT} \times R_{DS(on)}$ . This lower dropout also results in better efficiency and lower heat dissipation in the pass element for a given  $I_{OUT}$ .

## Maximum programmable output voltage and NMOS threshold voltage, V<sub>T</sub>

The maximum output voltage that can be regulated by the programmable regulator depends on the device's power supply ( $V_{CC}$ ) and threshold voltage ( $V_{T}$ ) of the NMOS. With the drive voltage tied to the gate and  $V_{OUT}$  connected to the source of the NMOS, a minimum  $V_{GS} = V_{T}$  must be maintained in order to maintain the n-channel inversion layer. The maximum  $V_{OUT}$  is calculated as follows:

$$V_{OUT} = V_S = V_G - V_T$$

With  $V_{CC} = 12$  V and a corresponding worst-case gate drive voltage of 9 V, the highest achievable  $V_{OUT} = 9$  V - V<sub>T</sub>.

#### Stability

A quality of the old npn regulators was their inherent stability under almost any type of load conditions and output capacitors. An NMOS regulator has the same benefit. Thus, capacitor selection and equivalent-series-resistance (ESR) values are not needed for stability, but still should be chosen properly for best transient response (see below).

#### capacitor selection

C<sub>out</sub>: Although a minimum capacitance is not needed for stability with an NMOS pass device, higher capacitance values improve transient response. In addition, low-ESR capacitors also help transient response. Tantalum or aluminum electrolytics can be used for bulk capacitances, while ceramic bypass capacitors can be used to decouple high-frequency transients due to their low ESL (equivalent series inductance).

$C_{in}$ : Input capacitors placed at the drain of the NMOS pass transistor ( $V_{PWR}$ ) help improve the overall transient response by suppressing surges in  $V_{PWR}$  during fast load changes. Low-ESR tantalum or aluminum electrolytic capacitors can be used; higher capacitance values improve transient response. A 0.1- $\mu$ F ceramic capacitor can be placed at the  $V_{CC}$  pin of the LFC789D25 to provide bypassing.

SLLS565B - MARCH 2003 - REVISED SEPTEMBER 2004

#### **APPLICATION INFORMATION**

# layout

Another benefit of a separate controller and pass element is that the heat dissipated in the external NMOS can be well isolated from the controller, which has very low power dissipation. Both of these factors allow the bandgap reference and control circuitry to operate over a more stable temperature range, resulting in very good accuracy over full-load conditions. The LFC789D25 should be placed as close as possible to the external pass element because short PCB traces allow minimal EMI coupling to both the drive and sense lines.

For best accuracy, connect the SEN pins as close to the load as possible, not to the source of the NMOS. Also, place the SEN trace in the same direction and plane as the power trace that connects the source of the NMOS to the load. Also, it is good practice to keep the load current return path as far as possible from the SEN trace.

Place the 0.1- $\mu$ F bypass capacitor as close as possible to the  $V_{CC}$  pin and connect it directly to the ground plane. The GND pin of the LFC789D25 should be connected to the ground plane.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                    |              |                         |         |

| LFC789D25CDR     | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | KADAC                   | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 14-Jul-2012

# TAPE AND REEL INFORMATION

## **REEL DIMENSIONS**

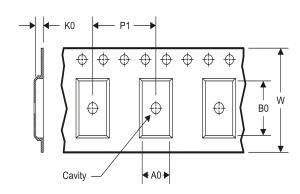

## **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

# TAPE AND REEL INFORMATION

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LFC789D25CDR  | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| LFC789D25CPWR | TSSOP           | PW                 | 8 | 2000 | 330.0                    | 12.4                     | 7.0        | 3.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 14-Jul-2012

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LFC789D25CDR  | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

| LFC789D25CPWR | TSSOP        | PW              | 8    | 2000 | 367.0       | 367.0      | 35.0        |

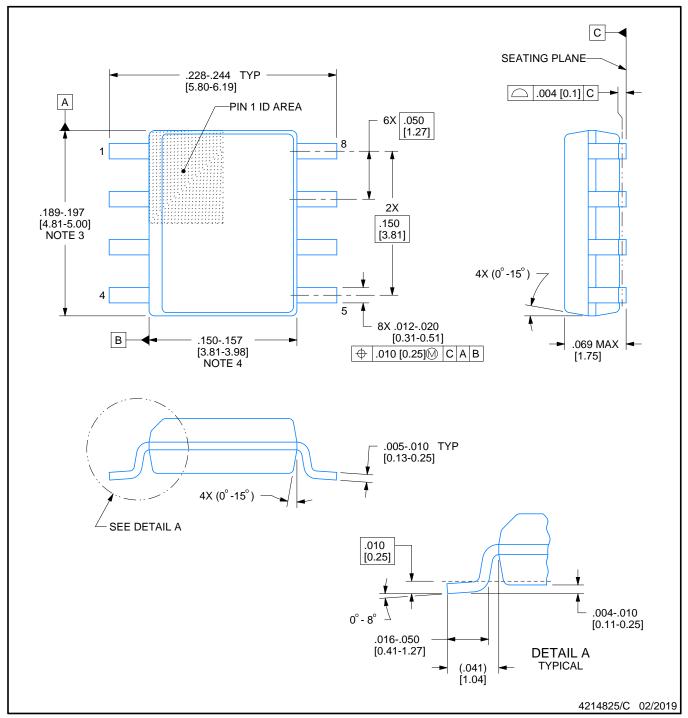

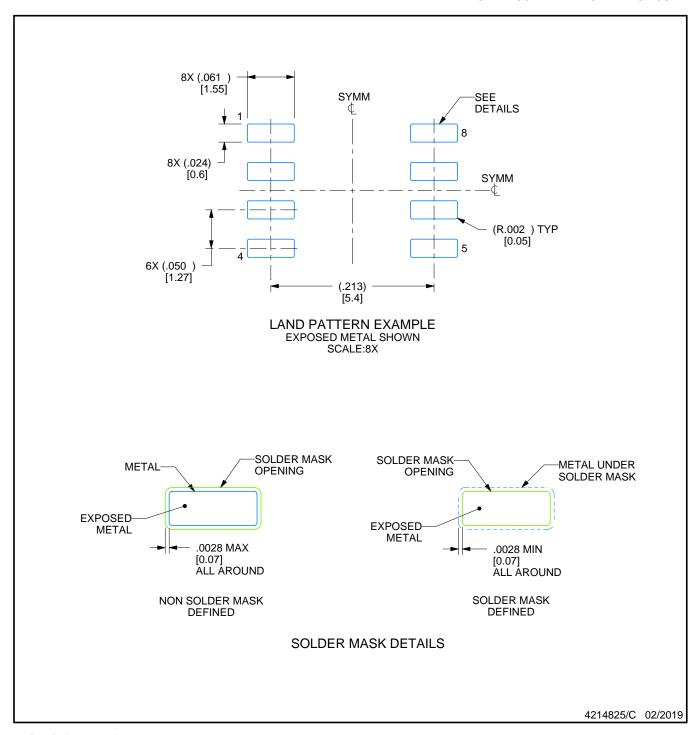

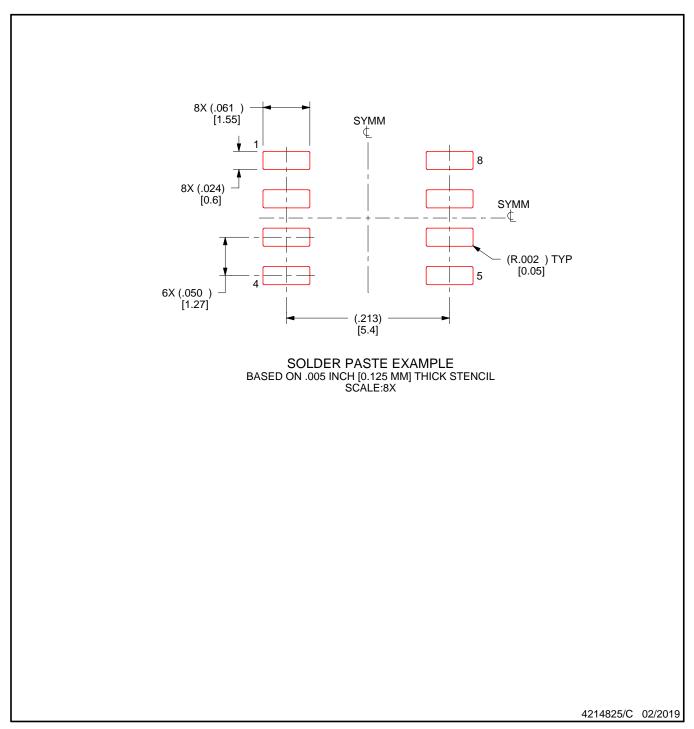

SMALL OUTLINE INTEGRATED CIRCUIT

# NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated