# Up to 3 A step-down switching regulator

Datasheet - production data

#### **Features**

- 3 A DC output current

- Operating input voltage from 5.5 V to 48 V

- 850 kHz internally fixed switching frequency

- Internal soft-start

- Power good open collector output

- · Current mode architecture

- Embedded compensation network

- Zero load current operation

- Internal current limiting

- · Inhibit for zero current consumption

- 2 mA maximum quiescent current over temperature range

- 250 mΩ typ. R<sub>DS(on)</sub>

- Thermal shutdown

### **Applications**

- · Factory automation

- Printers

- DC-DC modules

- · High current LED drivers

## **Description**

The ST1S14 is a step-down monolithic power switching regulator able to deliver up to 3 A DC current to the load depending on the application conditions. The high current level is also achieved thanks to a HSOP8 package with exposed frame, that allows to reduce the R<sub>th(JA)</sub> down to approximately 40 °C/W. The output voltage can be set from 1.22 V. The device uses an internal Nchannel DMOS transistor (with a typical  $R_{DS(on)}$  of 200 m $\Omega$ ) as the switching element to minimize the size of the external components. The internal oscillator fixes the switching frequency at 850 kHz. Power good open collector output validates the regulated output voltage as soon as it reaches the regulation. Pulse-by-pulse current limit offers an effective constant current short-circuit protection. Current foldback decreases overstress in a persistent short-circuit condition.

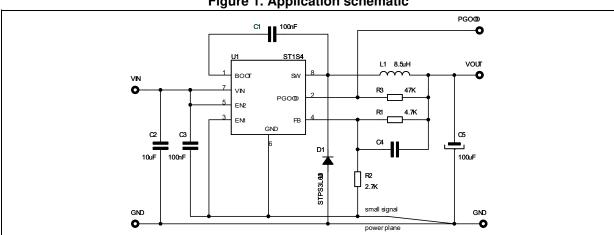

Figure 1. Application schematic

ST1S14 Contents

# **Contents**

2/46

| 1    | Pin s | settings                                                | 6          |

|------|-------|---------------------------------------------------------|------------|

|      | 1.1   | Pin connection                                          | 6          |

|      | 1.2   | Pin description                                         | 6          |

|      | 1.3   | Enable inputs                                           | 6          |

| 2    | Elec  | etrical data                                            | 7          |

|      | 2.1   | Maximum ratings                                         | 7          |

|      | 2.2   | Thermal data                                            | 7          |

|      | 2.3   | ESD protection                                          | 7          |

| 3    | Elec  | etrical characteristics                                 | 8          |

| 4    | Fund  | ction description                                       | 10         |

|      | 4.1   | Power supply and voltage reference                      |            |

|      | 4.2   | Voltage monitor                                         |            |

|      | 4.3   | Soft-start                                              |            |

|      | 4.4   | Error amplifier                                         | 13         |

|      | 4.5   | Inhibit function                                        | 13         |

|      | 4.6   | Thermal shutdown                                        |            |

| 5    | Add   | itional features and limitations                        | 14         |

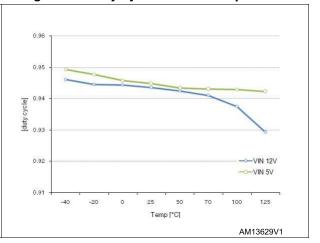

|      | 5.1   | Maximum duty cycle                                      | 14         |

|      | 5.2   | Minimum output voltage over $V_{\text{IN}}$ range       | 15         |

| 6    | Clos  | sing the loop                                           | 16         |

|      | 6.1   | G <sub>CO</sub> (s) control to output transfer function | 17         |

|      | 6.2   | Error amplifier compensation network                    | 18         |

|      | 6.3   | Voltage divider                                         | 19         |

|      | 6.4   | Total loop gain                                         | 20         |

| 7    | Арр   | lication information                                    | 22         |

|      | 7.1   | Component selection                                     | 22         |

|      |       | 7.1.1 Input capacitor                                   | 22         |

| 2/46 |       | DocID17977 Rev 3                                        | <b>A7/</b> |

DocID17977 Rev 3

|    |       | 7.1.2    | Output capacitor                          | . 23 |

|----|-------|----------|-------------------------------------------|------|

|    |       | 7.1.3    | Inductor                                  | . 24 |

|    | 7.2   | Layout   | considerations                            | 24   |

|    | 7.3   | Therma   | I considerations                          | 26   |

|    | 7.4   | Short-ci | rcuit protection                          | 27   |

|    |       | 7.4.1    | 300 mV < V <sub>FB</sub> < 1.22 V         | . 28 |

|    |       | 7.4.2    | V <sub>FB</sub> < 300 mV                  | . 31 |

|    |       | 7.4.3    | Start up phase in short circuit condition | . 33 |

|    | 7.5   | Applica  | tion circuit                              | 35   |

| 8  | Typic | al chara | acteristics                               | 38   |

| 9  | Packa | age med  | chanical data                             | 42   |

| 10 | Ordei | r code . |                                           | 44   |

| 11 | Revis | ion his  | tory                                      | 45   |

List of figure ST1S14

# List of figure

4/46

| Figure 1.  | Application schematic                                                             | 1  |

|------------|-----------------------------------------------------------------------------------|----|

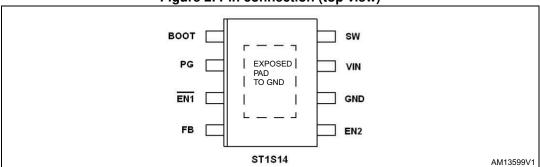

| Figure 2.  | Pin connection (top view)                                                         | 6  |

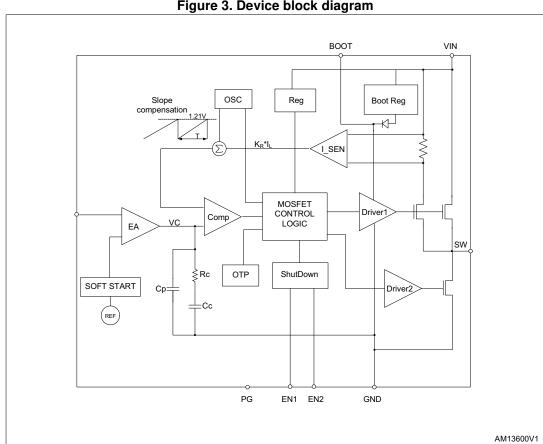

| Figure 3.  | Device block diagram                                                              | 10 |

| Figure 4.  | Internal circuit                                                                  | 11 |

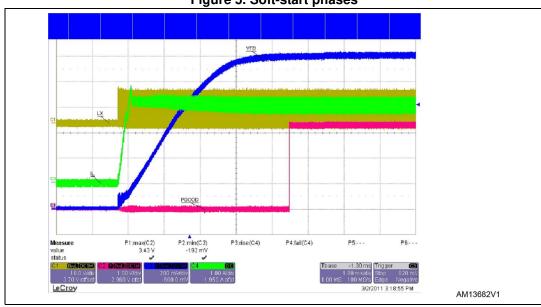

| Figure 5.  | Soft-start phases                                                                 | 12 |

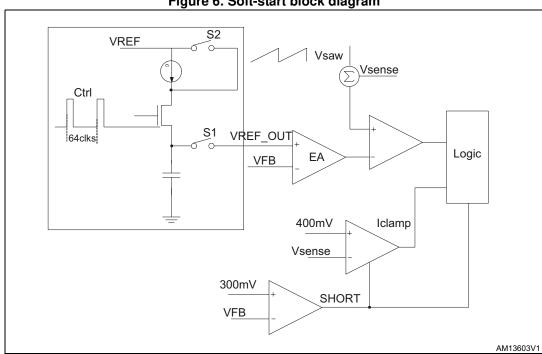

| Figure 6.  | Soft-start block diagram                                                          | 12 |

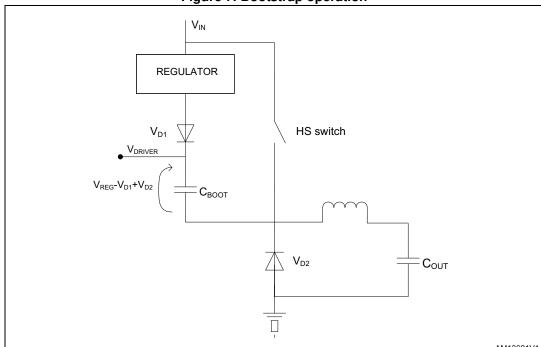

| Figure 7.  | Bootstrap operation                                                               | 14 |

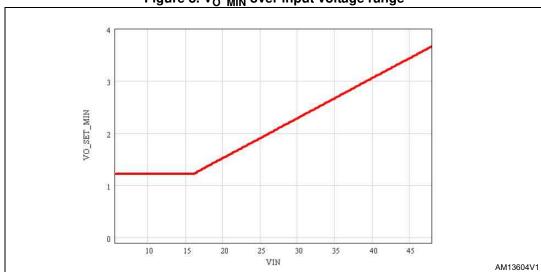

| Figure 8.  | V <sub>O MIN</sub> over input voltage range                                       | 15 |

| Figure 9.  | Block diagram of the loop                                                         | 16 |

| Figure 10. | Transconductance embedded error amplifier                                         | 18 |

| Figure 11. | Leading network example                                                           | 19 |

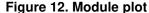

| Figure 12. | Module plot                                                                       | 20 |

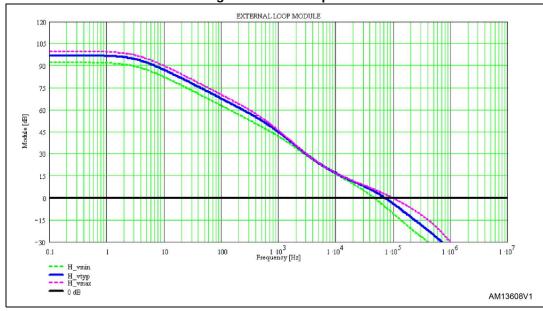

| Figure 13. | Phase plot                                                                        | 21 |

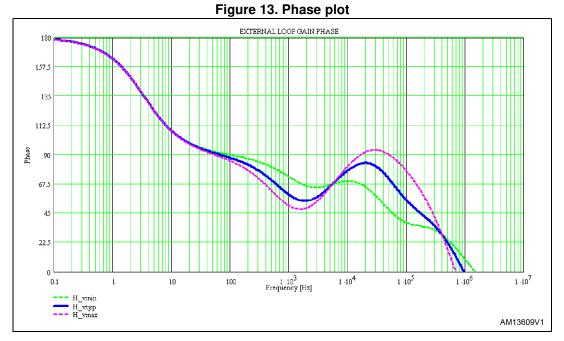

| Figure 14. | Layout example                                                                    | 25 |

| Figure 15. | Switching losses                                                                  |    |

| Figure 16. | Minimum V <sub>FB</sub> for effective pulse-by-pulse protection over VIN          | 30 |

| Figure 17. | I <sub>L</sub> diverging triggers hiccup protection (V <sub>IN</sub> = 48 V)      | 30 |

| Figure 18. | Current and frequency foldback triggered when V <sub>FB</sub> <300 mV (red trace) |    |

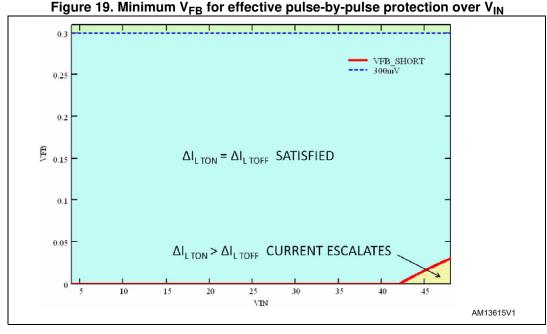

| Figure 19. | Minimum V <sub>FB</sub> for effective pulse-by-pulse protection over VIN          | 32 |

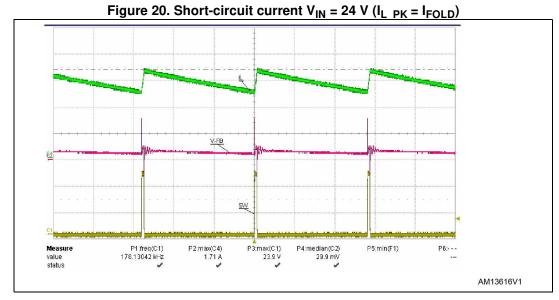

| Figure 20. | Short-circuit current VIN = 24 V (I <sub>L PK</sub> = I <sub>FOLD</sub> )         | 33 |

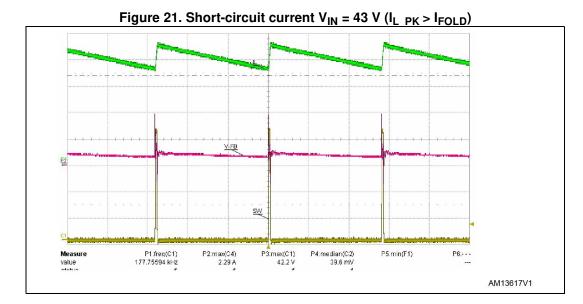

| Figure 21. | Short-circuit current VIN = 43 V (I <sub>L PK</sub> > I <sub>FOLD</sub> )         |    |

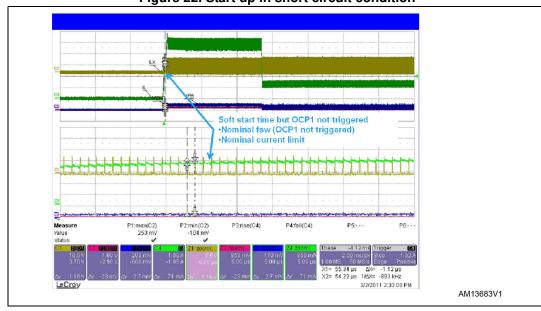

| Figure 22. | Start up in short circuit condition                                               |    |

| Figure 23. | Over current protection triggers the frequency foldback                           | 34 |

| Figure 24. | Over current protection triggers the current and frequency foldback               |    |

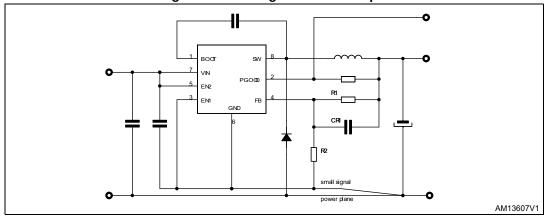

| Figure 25. | Demonstration board application circuit                                           | 35 |

| Figure 26. | PCB layout (component side)                                                       | 36 |

| Figure 27. | PCB layout (bottom side)                                                          | 37 |

| Figure 28. | Line regulation                                                                   | 38 |

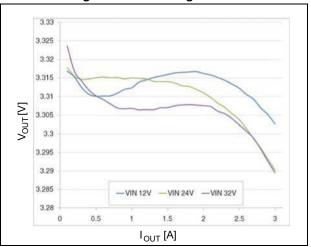

| Figure 29. | Load regulation                                                                   | 38 |

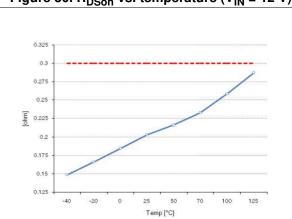

| Figure 30. | RDSon vs. temperature (VIN = 12 V)                                                | 38 |

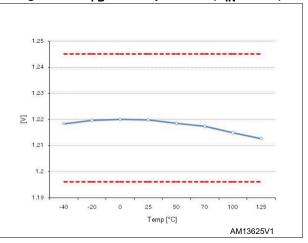

| Figure 31. | VFB vs. temperature (VIN = 12 V)                                                  | 38 |

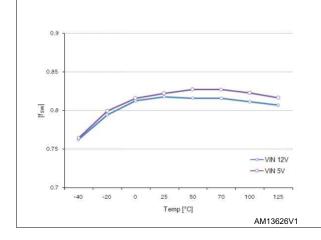

| Figure 32. | fSW vs. temperature                                                               | 38 |

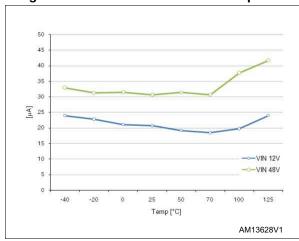

| Figure 33. | Quiescent current vs. temperature                                                 | 38 |

| Figure 34. | Shutdown current vs. temperature                                                  |    |

| Figure 35. | Duty cycle max vs. temperature                                                    | 39 |

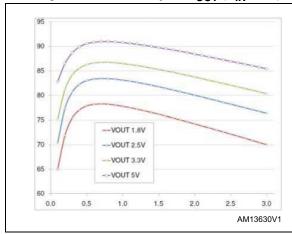

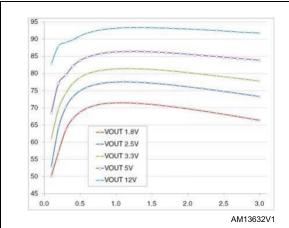

| Figure 36. | Efficiency vs. I <sub>OUT</sub> (V <sub>IN</sub> 12 V)                            | 39 |

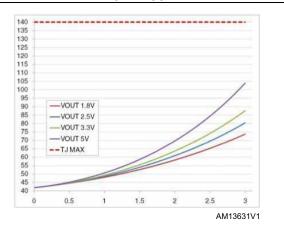

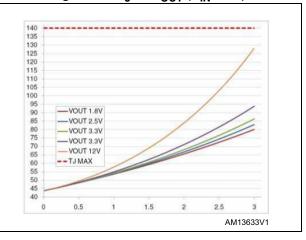

| Figure 37. | T <sub>J</sub> vs. I <sub>OUT</sub> (V <sub>IN</sub> 12 V)                        |    |

| Figure 38. | Efficiency vs. I <sub>OUT</sub> (V <sub>IN</sub> 24 V)                            | 39 |

| Figure 39. | T <sub>.I</sub> vs. I <sub>OUT</sub> (V <sub>IN</sub> 24 V)                       | 39 |

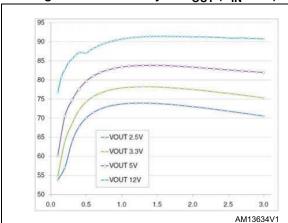

| Figure 40. | Efficiency vs. I <sub>OUT</sub> (V <sub>IN</sub> 32 V)                            | 40 |

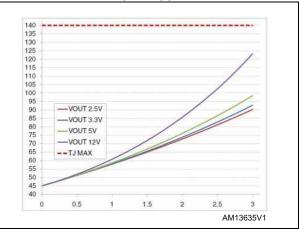

| Figure 41. | T <sub>J</sub> vs. I <sub>OUT</sub> (V <sub>IN</sub> 32 V)                        | 40 |

| Figure 42. | 1 A to 3 A load transient (V <sub>IN</sub> 12 V)                                  | 40 |

| Figure 43. | Zoom - 1 A to 3 A load transient (V <sub>IN</sub> 12 V)                           | 40 |

| Figure 44. | Zoom - 1 A to 3 A rising edge load transient (V <sub>IN</sub> 12 V)               |    |

| Figure 15  | 1 A to 3 A falling edge load transient (V.,, 24 V)                                | 40 |

DocID17977 Rev 3

ST1S14 List of figure

| Figure 46. | Zoom - 1 A to 3 A rising edge load transient (V <sub>IN</sub> 24 V)  | . 41 |

|------------|----------------------------------------------------------------------|------|

| Figure 47. | Zoom - 1 A to 3 A falling edge load transient (V <sub>IN</sub> 24 V) | . 41 |

| Figure 48. | 1 A to 3 A load transient (V <sub>IN</sub> 32 V)                     | . 41 |

| Figure 49. | Zoom - 1 A to 3 A rising edge load transient (V <sub>IN</sub> 32 V)  | . 41 |

| Figure 50. | Zoom - 1 A to 3 A falling edge load transient (V <sub>IN</sub> 32 V) | . 41 |

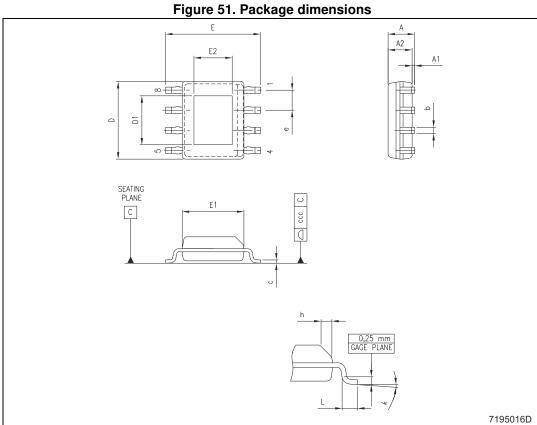

| Figure 51. | Package dimensions                                                   | . 43 |

Pin settings ST1S14

# 1 Pin settings

# 1.1 Pin connection

Figure 2. Pin connection (top view)

# 1.2 Pin description

Table 1. Pin description

| N | Pin             | Description                                                                                          |  |

|---|-----------------|------------------------------------------------------------------------------------------------------|--|

| 1 | воот            | Bootstrap capacitor for N-channel gate driver. Connects 100 nF low ESR capacitor from BOOT pin to SW |  |

| 2 | PG              | Power good                                                                                           |  |

| 3 | EN1             | Enable pin active low                                                                                |  |

| 4 | FB              | Feedback voltage                                                                                     |  |

| 5 | EN2             | Enable pin active high                                                                               |  |

| 6 | GND             | Ground pin                                                                                           |  |

| 7 | V <sub>IN</sub> | Input supply pin                                                                                     |  |

| 8 | SW              | Switching node                                                                                       |  |

|   | E.p.            | Exposed pad must be connected to GND                                                                 |  |

# 1.3 Enable inputs

Table 2. Truth table

| EN1 | EN2 | Device status |

|-----|-----|---------------|

| Н   | L   | INH           |

| Н   | Н   | INH           |

| L   | L   | INH           |

| L   | Н   | ON            |

ST1S14 Electrical data

# 2 Electrical data

# 2.1 Maximum ratings

Table 3. Absolute maximum ratings

| Symbol            | Parameter                            | Value                          | Unit |

|-------------------|--------------------------------------|--------------------------------|------|

| V <sub>IN</sub>   | Power supply input voltage           | -0.3 to 52                     | V    |

| V <sub>EN1</sub>  | Enable 1 voltage                     | -0.3 to 7                      | V    |

| V <sub>EN2</sub>  | Enable 2 voltage                     | -0.3 to (V <sub>IN</sub> +0.3) | V    |

| PG                | Power good                           | -0.3 to (V <sub>IN</sub> +0.3) | V    |

| BOOT              | Bootstrap pin                        | -0.3 to 55                     | V    |

| SW                | Switching node                       | -1 to (V <sub>IN</sub> +0.3)   | V    |

| V <sub>FB</sub>   | Feedback voltage                     | -0.3 to 3                      | V    |

| T <sub>J</sub>    | Operating junction temperature range | -40 to 150                     | °C   |

| T <sub>STG</sub>  | Storage temperature range            | -65 to 150                     | °C   |

| T <sub>LEAD</sub> | Lead temperature (soldering 10 sec.) | 260                            | °C   |

## 2.2 Thermal data

Table 4. Thermal data

| Symbol             | Parameter                           | Value | Unit |

|--------------------|-------------------------------------|-------|------|

| R <sub>th JA</sub> | Thermal resistance junction-ambient | 40    | °C/W |

# 2.3 ESD protection

Table 5. ESD protection

| Symbol | Test condition | Value | Unit |

|--------|----------------|-------|------|

| ESD    | НВМ            | 4     | kV   |

| LSD    | ММ             | 500   | V    |

Electrical characteristics ST1S14

# 3 Electrical characteristics

All the population tested at  $T_J$  = 25 °C,  $V_{CC}$  =12 V,  $V_{EN1}$  = 0 V,  $V_{EN2}$  =  $V_{CC}$  unless otherwise specified.

The specification is guaranteed from (-40 to +125 °C)  $T_J$  temperature range by design, characterization, and statistical correlation.

**Table 6. Electrical characteristics**

| Symbol               | Parameter                                     | Test condition                              |     | Min   | Тур                       | Max   | Unit |

|----------------------|-----------------------------------------------|---------------------------------------------|-----|-------|---------------------------|-------|------|

| V <sub>IN</sub>      | Operating input voltage range                 |                                             |     | 5.5   |                           | 48    | ٧    |

| R <sub>DS(on)</sub>  | MOSFET on resistance                          | I <sub>SW</sub> =1 A                        |     |       | 0.2                       | 0.4   | Ω    |

| I <sub>SW</sub>      | Maximum limiting current                      |                                             |     | 3.7   | 4.5                       | 5.2   | Α    |

| t <sub>HICCUP</sub>  | Hiccup time                                   |                                             |     |       | 16                        |       | ms   |

| f <sub>SW</sub>      | Switching frequency                           |                                             |     | 600   | 850                       | 1000  | kHz  |

|                      | Duty cycle                                    |                                             | (1) |       | 90                        |       | %    |

| T <sub>ON MIN</sub>  | Minimum conduction time of the power element  |                                             | (1) |       | 90                        |       | ns   |

| T <sub>OFF MIN</sub> | Minimum conduction time of the external diode |                                             | (1) | 75    | 90                        | 120   | ns   |

| DC chara             | cteristics                                    |                                             | ,   |       |                           |       |      |

| V                    | Voltage feedback                              | I <sub>LOAD</sub> =0 A                      |     | 1.202 | 1.22                      | 1.239 | V    |

| $V_{FB}$             |                                               | I <sub>LOAD</sub> =10 mA to 3 A             |     | 1.196 | 1.22                      | 1.245 | V    |

| I <sub>FB</sub>      | FB biasing current                            |                                             |     |       | 50                        |       | nA   |

| 1                    | Quiescent current                             | V <sub>FB</sub> =2 V                        |     |       | 1.3                       | 2     | mA   |

| Ιq                   | Quiescent current                             | V <sub>FB</sub> =2 V, V <sub>IN</sub> =48 V |     |       | 1.7                       | 2.4   | mA   |

| I <sub>qst-by</sub>  | Standby quiescent current                     | Device OFF (see <i>Table 2</i> )            |     |       | 16                        | 34    | μΑ   |

|                      | Power good threshold                          | V <sub>FB</sub> rising edge                 |     |       | 0.92*<br>V <sub>OUT</sub> |       | V    |

| PG                   | Fower good tilleshold                         | V <sub>FB</sub> falling edge                |     |       | 0.8*<br>V <sub>OUT</sub>  |       | V    |

|                      | PG output voltage (open collector active)     | I <sub>SINK</sub> =6 mA                     |     |       |                           | 0.4   | V    |

| Inhibit              |                                               |                                             |     |       |                           |       |      |

Table 6. Electrical characteristics (continued)

| Symbol             | Parameter                    | Test condition                                                 |     | Min | Тур  | Max  | Unit |

|--------------------|------------------------------|----------------------------------------------------------------|-----|-----|------|------|------|

|                    | Enable 1 levels              | Device ON<br>V <sub>IN</sub> =5.5 V to 48 V                    |     |     |      | 0.5  | V    |

| V <sub>EN1</sub>   |                              | Device OFF<br>V <sub>IN</sub> =5.5 V to 48 V                   |     | 1.5 |      |      | V    |

| I <sub>EN1</sub>   | Enable 1 biasing current     | V <sub>EN1</sub> =5 V                                          |     | 0.7 | 1.6  | 3.5  | μА   |

| V <sub>EN2</sub>   | Enable 2 levels              | Device ON<br>V <sub>IN</sub> =5.5 V to 48 V                    |     | 1.5 |      |      | V    |

|                    |                              | Device OFF<br>V <sub>IN</sub> =5.5 V to 48 V                   |     |     |      | 0.5  | V    |

|                    | Enable 2 biasing current     | V <sub>EN1</sub> =0 V; V <sub>EN2</sub> =0 V                   |     | -1  | -2.4 | -4.5 | μΑ   |

| I <sub>EN2</sub>   |                              | V <sub>EN1</sub> =0 V; V <sub>EN2</sub> =12 V                  |     | 2.7 | 5.8  | 10   | μΑ   |

|                    |                              | V <sub>EN1</sub> =0 V; V <sub>CC</sub> =V <sub>EN2</sub> =48 V |     | 3.0 | 6.0  | 10   | μА   |

| Thermal shutdown   |                              |                                                                |     |     |      |      |      |

| T <sub>SHDWN</sub> | Thermal shutdown temperature |                                                                | (1) | 140 | 150  | 160  | °C   |

| T <sub>HYS</sub>   | Thermal shutdown hysteresis  |                                                                | (1) |     | 15   |      | °C   |

<sup>1.</sup> Parameter guaranteed by design

ST1S14 **Function description**

#### 4 **Function description**

The ST1S14 is based on a "peak current mode", constant frequency control. As a consequence the intersection between the error amplifier output and the sensed inductor current generates the control signal to drive the power switch.

The main internal blocks shown in the block diagram in *Figure 3* are:

- A fully integrated sawtooth oscillator with a typical frequency of 850 kHz

- A transconductance error amplifier

- A high side current sense amplifier to track the inductor current

- A pulse width modulator (PWM) comparator and the circuitry necessary to drive the internal power element

- Soft-start circuitry to decrease the inrush current at power-up

- Current limitation circuit based on the pulse-by-pulse current protection with frequency divider based on FB voltage and the hiccup protection

- Bootstrap circuitry to drive the embedded N-MOS switch

- A multi input inhibit block for standby operation

- A circuit to implement the thermal protection function

Figure 3. Device block diagram

### 4.1 Power supply and voltage reference

The internal regulator circuit consists of a start-up circuit, an internal voltage pre-regulator, the bandgap voltage reference, and the bias block that provides current to all the blocks. The starter supplies the start-up current to the entire device when the input voltage goes high and the device is enabled (inhibit pin connected to ground). The pre-regulator block supplies the bandgap cell with a pre-regulated voltage that has a very low supply voltage noise sensitivity.

### 4.2 Voltage monitor

An internal block continuously senses the  $V_{cc}$ ,  $V_{ref}$ , and  $V_{bg}$ . If the monitored voltages are good, the regulator begins operating. There is also a hysteresis on the  $V_{CC}$  (UVLO).

STARTER PREREGULATOR

VREG

BANDGAP

IC BIAS

VREF

AM13601V1

4.3 Soft-start

The startup phase minimizes the inrush current and decreases the stress of the power components at the power up. The startup takes place when VIN crosses the selected UVLO threshold. A internal counter (2816 clks) sets the soft start time (see Figure 5).

The reference of the error amplifier is ramped smootly in 704 steps (one step every 4 clks).

A low pass filter smooths each step to minimize output discontinuity. Considering the typical 850 kHz switching frequency, the phase two duration is 3.3 msec

The device has full load current capability during the soft start time in order to charge the output capacitor (see Figure 5).

**Function description** ST1S14

Figure 5. Soft-start phases

During normal operation a new soft start cycle takes place in case of:

- HICCUP mode current protection

- thermal shutdown event

- **UVLO** event

- the device is driven in INH mode

Figure 6. Soft-start block diagram

### 4.4 Error amplifier

The voltage error amplifier is the core of the loop regulation. It is a transconductance operational amplifier whose non inverting input is connected to the internal voltage reference (1.222 V), while the inverting input (FB) is connected to the external divider or directly to the output voltage.

The error amplifier is internally compensated to minimize the size of the final application.

Table 7. Uncompensated error amplifier characteristics

| Description        | Values |

|--------------------|--------|

| Transconductance   | 218 μS |

| Low frequency gain | 93 dB  |

| C <sub>P</sub>     | 24 pF  |

| C <sub>C</sub>     | 211 pF |

| R <sub>C</sub>     | 200 kΩ |

The error amplifier output is compared with the inductor current sense information to perform PWM control.

#### 4.5 Inhibit function

The inhibit feature is used to set the device in standby mode according to *Table 2*. When the device is disabled, the power consumption is reduced to less than 40  $\mu$ A. The EN2 pin is also V<sub>IN</sub> compatible.

#### 4.6 Thermal shutdown

The shutdown block generates a signal that turns off the power stage if the temperature of the chip goes higher than a fixed internal threshold (150±10 °C). The sensing element of the chip is very close to the PDMOS area, ensuring fast and accurate temperature detection. A hysteresis of approximately 15 °C keeps the device from turning on and off continuously.

### 5 Additional features and limitations

## 5.1 Maximum duty cycle

The bootstrap circuitry charges, cycle-by-cycle, the external bootstrap capacitor to generate a voltage higher than  $V_{IN}$  necessary to drive the internal N-channel power element.

An internal linear regulator charges the  $C_{BOOT}$  during the conduction time of the external freewheeling diode during the switching activity. The internal logic implements a minimum OFF time of the high side switch (90 nsec typ.) to prevent the bootstrap discharge at high duty cycle. As a consequence, the ST1S14 can operate at a maximum duty cycle of around 90 % typ.

The ST1S14 embeds the diode  $V_{D1}$  required for the bootstrap operation.

Figure 7. Bootstrap operation

## 5.2 Minimum output voltage over V<sub>IN</sub> range

The minimum regulated output voltage at a given input voltage is limited by the minimum conduction time of the power element, that is 90 nsec typ. for the ST1S14:

#### **Equation 1**

$$V_{O\_MIN}(V_{IN}) = V_{IN} \cdot D_{MIN} = V_{IN} \cdot \frac{T_{ON\_MIN}}{T_{SW}} = V_{IN} \cdot \frac{90 \text{ns}}{1.18 \mu \text{s}}$$

which is plotted in Figure 14. The reference of the embedded error amplifier (1.22 V) sets the minimum  $V_{O\ SET}$  at low  $V_{IN}$ .

Figure 8. V<sub>O MIN</sub> over input voltage range

*Figure 8* shows the minimum output voltage over input voltage range to have constant switching activity and a predictable output voltage ripple.

The regulator can, however, regulate the minimum input voltage over the entire input voltage range but, given the 90 ns minimum conduction time of the power element, it skips some pulses to keep the output voltage in regulation when *Equation 1* is not satisfied.

This operation is not recommended at the nominal input voltage of the application mainly because it affects the output voltage ripple, but it is generally accepted during a line transient event.

Closing the loop ST1S14

# 6 Closing the loop

PWM control

Current sens e

HS

switch

L C filter

resistor divider

Court

R1

Compensation network

PWM comparator

Cp

Rc

Error amplifier

AM13605V1

Figure 9. Block diagram of the loop

16/46 DocID17977 Rev 3

ST1S14 Closing the loop

## 6.1 G<sub>CO</sub>(s) control to output transfer function

The accurate control to output transfer function for a buck peak current mode converter can be written as:

#### **Equation 2**

$$G_{CO}(s) = \frac{R_0}{R_i} \cdot \frac{1}{1 + \frac{R_0 \cdot T_{SW}}{L} \cdot [m_C \cdot (1 - D) - 0.5]} \cdot \frac{\left(1 + \frac{s}{\omega_z}\right)}{\left(1 + \frac{s}{\omega_p}\right)} \cdot F_H(s)$$

where  $R_0$  represents the load resistance,  $R_i$  the equivalent sensing resistor of the current sense circuitry,  $\omega_p$  the single pole introduced by the LC filter, and  $\omega_z$  the zero given by the ESR of the output capacitor.

F<sub>H</sub>(s) accounts for the sampling effect performed by the PWM comparator on the output of the error amplifier that introduces a double pole at one half of the switching frequency.

#### **Equation 3**

$$\omega_{Z} = \frac{1}{\mathsf{ESR} \cdot \mathsf{C}_{\mathsf{OUT}}}$$

#### **Equation 4**

$$\omega_{n} = \frac{1}{R_{LOAD} \cdot C_{OUT}} + \frac{m_{C} \cdot (1 - D) - 0.5}{L \cdot C_{OUT} \cdot f_{SW}}$$

where:

#### **Equation 5**

$$\begin{cases} m_C = 1 + \frac{S_e}{S_n} \\ S_e = V_{pp} \cdot f_{SW} \\ S_n = \frac{V_{IN} - V_{OUT}}{L} \cdot R_i \end{cases}$$

$S_n$  represents the ON time slope of the sensed inductor current, and  $S_e$  the ON time slope of the external ramp ( $V_{PP}$  peak to peak amplitude) that implements the slope compensation to avoid sub-harmonic oscillations at duty cycle over 50 %.

The sampling effect contribution  $F_H(s)$  is:

#### **Equation 6**

$$F_{H}(s) = \frac{1}{1 + \frac{s}{\omega_{n} \cdot Q_{P}} + \frac{s^{2}}{\omega_{n}^{2}}}$$

where:

Closing the loop ST1S14

#### **Equation 7**

$$Q_{P} = \frac{1}{\pi \cdot [m_{C} \cdot (1-D) - 0.5]}$$

## 6.2 Error amplifier compensation network

The ST1S14 embeds the error amplifier (see *Figure 10*) and a pre-defined compensation network which is effective in stabilizing the system in most of the application conditions.

Figure 10. Transconductance embedded error amplifier

$R_C$  and  $C_C$  introduce a pole and a zero in the open loop gain.  $C_P$  does not significantly affect system stability but it is useful to reduce the noise at the output of the error amplifier.

The transfer function of the error amplifier and its compensation network is:

#### **Equation 8**

$$\mathsf{A}_0(s) = \frac{\mathsf{A}_{\mathsf{V}0} \cdot (1 + s \cdot \mathsf{R}_c \cdot \mathsf{C}_c)}{s^2 \cdot \mathsf{R}_0 \cdot (\mathsf{C}_0 + \mathsf{C}_p) \cdot \mathsf{R}_c \cdot \mathsf{C}_c + s \cdot (\mathsf{R}_0 \cdot \mathsf{C}_c + \mathsf{R}_0 \cdot (\mathsf{C}_0 + \mathsf{C}_p) + \mathsf{R}_c \cdot \mathsf{C}_c) + 1}$$

where  $A_{vo} = G_m \cdot R_o$ .

The poles of this transfer function are (if  $C_c >> C_0 + C_P$ ):

#### **Equation 9**

$$f_{PLF} = \frac{1}{2 \cdot \pi \cdot R_0 \cdot C_c}$$

18/46 DocID17977 Rev 3

ST1S14 Closing the loop

#### **Equation 10**

$$f_{P HF} = \frac{1}{2 \cdot \pi \cdot R_c \cdot (C_0 + C_p)}$$

whereas the zero is defined as:

#### **Equation 11**

$$F_Z = \frac{1}{2 \cdot \pi \cdot R_c \cdot C_c}$$

The embedded compensation network is  $R_C=200$  K,  $C_P=24$  pF,  $C_C=211$  pF and  $C_O$  can be considered negligible, so the singularities are:

#### **Equation 12**

$$f_Z = 3,77 \text{ kHz}$$

$f_{P \, LF} = 3,01 \text{ Hz}$   $f_{P \, HF} = 33,16 \text{ kHz}$

## 6.3 Voltage divider

The contribution of a simple voltage divider is:

#### **Equation 13**

$$G_{DIV}(s) = \frac{R_2}{R_1 + R_2}$$

Figure 11. Leading network example

A small signal capacitor in parallel to the upper resistor (see *Figure 11*.) of the voltage divider implements a leading network ( $f_{zero} < f_{pole}$ ), sometimes necessary to improve the system phase margin:

#### **Equation 14**

Closing the loop ST1S14

$$G_{\text{DIV}}(s) = \frac{R_2}{R_1 + R_2} \cdot \frac{(1 + s \cdot R_1 \cdot C_{R1})}{\left(1 + s \cdot \frac{R_1 \cdot R_2}{R_1 + R_2} \cdot C_{R1}\right)}$$

where:

$$f_Z = \frac{1}{2 \cdot \pi \cdot R_1 \cdot C_{R1}}$$

$$f_P = \frac{1}{2 \cdot \pi \cdot \frac{R_1 \cdot R_2}{R_1 + R_2} \cdot C_{R1}}$$

$$f_Z < f_P$$

### 6.4 Total loop gain

In summary, the open loop gain can be expressed as:

#### **Equation 15**

$$G(s) = G_{DIV}(s) \cdot G_{CO}(s) \cdot A_0(s)$$

Example:  $V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ ,  $R_{OUT} = 2 \Omega$ .

The resistor divider is  $R_1$ =5.6 K,  $R_2$ =3.3 K.

$C_{R1}$ =150 nF implements a leading network ( $f_Z$ =190 kHz,  $f_P$ =510 kHz).

Selecting L = 8.2  $\mu$ H,  $C_{OUT}$  = 100  $\mu$ F, and ESR = 75  $m\Omega$ , the gain and phase bode diagrams are plotted respectively in *Figure 12* and *13* over input voltage range ( $V_{IN}$ =6 V to 48 V,  $I_{OUT}$ =3 A).

47/

ST1S14 Closing the loop

The cut-off frequency and the phase margin are:

#### **Equation 16**

$$\begin{split} V_{IN} &= 6V & f_C &= 46 \text{ kHz} & pm &= 49^{\circ} \\ V_{IN} &= 12V & f_C &= 71 \text{ kHz} & pm &= 62^{\circ} \\ V_{IN} &= 48V & f_C &= 97 \text{ kHz} & pm &= 78^{\circ} \end{split}$$

# 7 Application information

### 7.1 Component selection

### 7.1.1 Input capacitor

The input capacitor must be able to support the maximum input operating voltage and the maximum RMS input current.

Since step-down converters draw current from the input in pulses, the input current is squared and the height of each pulse is equal to the output current. The input capacitor has to absorb all this switching current, whose RMS value can be up to the load current divided by two (worst case, with duty cycle of 50 %). For this reason, the quality of these capacitors must be very high to minimize the power dissipation generated by the internal ESR, thereby improving system reliability and efficiency. The critical parameter is usually the RMS current rating, which must be higher than the RMS current flowing through the capacitor. The maximum RMS input current (flowing through the input capacitor) is:

#### **Equation 17**

$$I_{RMS} = I_O \cdot \sqrt{D - \frac{2 \cdot D^2}{\eta} + \frac{D^2}{\eta^2}}$$

where  $\eta$  is the expected system efficiency, D is the duty cycle, and  $I_O$  is the output DC current. Considering  $\eta=1$  this function reaches its maximum value at D = 0.5 and the equivalent RMS current is equal to  $I_O$  divided by 2. The maximum and minimum duty cycles are:

#### **Equation 18**

$$D_{MAX} = \frac{V_{OUT} + V_{F}}{V_{INMIN} - V_{SW}}$$

and

#### **Equation 19**

$$D_{MIN} = \frac{V_{OUT} + V_{F}}{V_{INMAX} - V_{SW}}$$

Where  $V_F$  is the freewheeling diode forward voltage and  $V_{SW}$  the voltage drop across the internal PDMOS. Considering the range  $D_{MIN}$  to  $D_{MAX}$ , it is possible to determine the maximum IRMS going through the input capacitor. Capacitors that may be considered are:

#### **Electrolytic capacitors:**

These are widely used due to their low cost and their availability in a wide range of RMS current ratings.

The only drawback is that, considering ripple current rating requirements, they are physically larger than other capacitors.

#### Ceramic capacitors:

If available for the required value and voltage rating, these capacitors usually have a higher RMS current rating for a given physical dimension (due to very low ESR).

The drawback is the considerably high cost.

#### **Tantalum capacitors:**

Small tantalum capacitors with very low ESR are becoming more available. However, they can occasionally burn if subjected to very high current during charge.

Therefore, it is suggested to avoid this type of capacitor for the input filter of the device as they could be stressed by a high surge current when connected to the power supply.

Table 8. List of ceramic capacitors for the ST1S14

| Manufacturer | Series              | Capacitor value (µ) | Rated voltage (V) |

|--------------|---------------------|---------------------|-------------------|

| TAIYO YUDEN  | UMK325BJ106MM-T     | 10                  | 50                |

| MURATA       | GRM42-2 X7R 475K 50 | 4.7                 | 50                |

If the selected capacitor is ceramic (so neglecting the ESR contribution), the input voltage ripple can be calculated as:

#### **Equation 20**

$$V_{IN\,PP} = \frac{I_O}{C_{IN} \cdot f_{SW}} \cdot \left[ \left( 1 - \frac{D}{\eta} \right) \cdot D + \frac{D}{\eta} \cdot (1 - D) \right]$$

### 7.1.2 Output capacitor

The output capacitor is very important to meet the output voltage ripple requirement.

Using a small inductor value is useful to reduce the size of the choke but it increases the current ripple. So, to reduce the output voltage ripple, a low ESR capacitor is required. Nevertheless, the ESR of the output capacitor introduces a zero in the open loop gain, which helps to increase the phase margin of the system. If the zero goes to a very high frequency, its effect is negligible.

#### **Ceramic capacitors**

Ceramic capacitors and very low ESR capacitors that introduce a zero outside the designed bandwidth ( $f_Z=1/(2*pi*ESR*C_{OUT}$ , see *Section 6: Closing the loop*) in general should be avoided. A leading network across the upper resistor of the voltage divider is useful to increase the phase margin and compensate the system (see *Section 6.3: Voltage divider*). The effectiveness of the leading network increases at high output voltage because the singularities become more split.

#### **High ESR capacitors**

The "high ESR capacitor" definition stands for a capacitor having an ESR value able to introduce a zero into the designed system bandwidth, which can be, as a general rule, up to f<sub>SW</sub>/5 at maximum. Tantalum or electrolytic capacitors belong to this group.

#### **Equation 21**

$$f_Z = \frac{1}{2 \cdot \pi \cdot ESR \cdot COUT} < BW < \frac{f_{SW}}{5}$$

Table 9. Output capacitor selection ESR  $(m\Omega)^{(1)}$ Manufacturer Rated voltage (V) Cap value (μF)<sup>(1)</sup> Series Nippon Chemicon **KZE** 6.3 to 50 Sanyo POSCAP(2) TAE 4 to 16 THB/C/E 4 to 16  $f_Z = \frac{1}{2 \cdot \pi \cdot FSB \cdot COUT} < BW$ **AVX TPS** 4 to 35

A list of some tantalum capacitor manufacturers is provided in *Table 9*.

- 1. see Section 6: Closing the loop for the selection of the output capacitor

- 2. POSCAP capacitors have some characteristics which are very similar to tantalum.

#### 7.1.3 Inductor

The inductor value is very important as it fixes the ripple current flowing through the output capacitor. The ripple current is usually fixed at 20 - 40 % of  $I_{omax}$ , which is 0.6 - 1.2 A with  $I_{omax} = 3$  A. The approximate inductor value is obtained using the following formula:

#### **Equation 22**

$$L = \frac{(V_{IN} - V_{OUT})}{\Delta I} \cdot T_{ON}$$

where  $T_{ON}$  is the ON time of the internal switch, given by D · T. For example, with  $V_{OUT}$  = 3.3 V,  $V_{IN}$  = 24 V, and  $\Delta I_{O}$  = 0.8 A, the inductor value is about 4.7  $\mu$ H. The peak current through the inductor is given by:

#### **Equation 23**

$$I_{PK} = I_O + \frac{\Delta I}{2}$$

and it can be observed that if the inductor value decreases, the peak current (which must be lower than the current limit of the device) increases. So, when the peak current is fixed, a higher inductor value allows a higher value for the output current. In *Table 10*, some inductor manufacturers are listed.

Table 10. Inductor selection

| Manufacturer     | Series      | Inductor value (μH) | Saturation current (A) |

|------------------|-------------|---------------------|------------------------|

| Wurth Elektronik | WE-HCI 7040 | 1 to 4.7            | 20 to 7                |

|                  | WE-HCI 7050 | 4.9 to 10           | 20 to 4.0              |

| Coilcraft        | XPL 7030    | 2.2 to 10           | 29 to 7.2              |

# 7.2 Layout considerations

The layout of switching DC-DC converters is very important to minimize noise and interference. Power-generating portions of the layout are the main cause of noise and so

high switching current loop areas should be kept as small as possible and lead lengths as short as possible.

High impedance paths (in particular the feedback connections) are susceptible to interference, so they should be as far as possible from the high current paths. A layout example is provided in *Figure 14* below.

The input and output loops are minimized to avoid radiation and high frequency resonance problems. The feedback pin connections to the external divider are very close to the device in order to avoid pick-up noise. Another important issue is the ground plane of the board. As the package has an exposed pad, it is very important to connect it to an extended ground plane in order to reduce the thermal resistance junction-to-ambient.

To increase the design noise immunity, different signal and power ground should be implemented in the layout (see *Section 7.5: Application circuit*). The signal ground serves the small signal components, the device ground pin, the exposed pad, and a small filtering capacitor connected to the VCC pin. The power ground serves the external diode and the input filter. The different grounds are connected underneath the output capacitor. Neglecting the current ripple contribution, the current flowing through this component is constant during the switching activity and so this is the cleanest ground point of the buck application circuit.

Figure 14. Layout example

#### 7.3 Thermal considerations

The dissipated power of the device is tied to three different sources:

Conduction losses due to the not insignificant R<sub>DSON</sub>, which are equal to:

#### **Equation 24**

$$P_{ON} = R_{DSON} \cdot (I_{OUT})^2 \cdot D$$

where D is the duty cycle of the application. Note that the duty cycle is theoretically given by the ratio between  $V_{OUT}$  and  $V_{IN}$ , but in practice it is substantially higher than this value to compensate for the losses in the overall application. For this reason, the conduction losses related to the  $R_{DSON}$  increase compared to an ideal case.

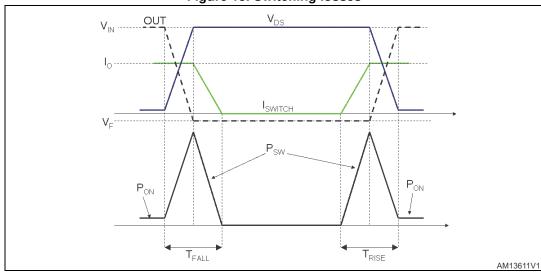

Switching losses due to turning on and off. These are derived using the following equation:

#### **Equation 25**

$$\mathsf{P}_{\mathsf{SW}} = \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \frac{(\mathsf{T}_{\mathsf{RISE}} + \mathsf{T}_{\mathsf{FALL}})}{2} \cdot \mathsf{F}_{\mathsf{SW}} = \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \mathsf{T}_{\mathsf{SW\_EQ}} \cdot \mathsf{F}_{\mathsf{SW}}$$

where  $T_{RISE}$  and  $T_{FALL}$  represent the switching times of the power element that cause the switching losses when driving an inductive load (see *Figure 15*).  $T_{SW}$  is the equivalent switching time.

Figure 15. Switching losses

Quiescent current losses.

#### **Equation 26**

$$P_O = V_{IN} \cdot I_O$$

Example:

-  $V_{IN} = 24 V$

-  $V_{OUT} = 5 V$

-  $I_{OUT} = 3 A$

$R_{DS(on)}$  has a typical value of 0.2  $\Omega$  @ 25 °C and increases to a maximum value of 0.4  $\Omega$  @ 125 °C. We can consider a value of 0.3  $\Omega$ .

T<sub>SW EQ</sub> is approximately 12 ns.

$I_Q$  has a typical value of 2 mA @  $V_{IN}$  = 24 V.

The overall losses are:

#### **Equation 27**

$$P_{TOT} = R_{DSON} \cdot (I_{OUT})^2 \cdot D + V_{IN} \cdot I_{OUT} \cdot T_{SW} \cdot F_{SW} + V_{IN} \cdot I_{Q} = ""$$

$$= 0.3 \cdot (3)^2 \cdot 0.137 + 24 \cdot 3 \cdot 12 \cdot 10^{-9} \cdot 850 \cdot 10^{-3} + 24 \cdot 2 \cdot 10^{-3} \approx 1.15W$$

The junction temperature of the device is:

#### **Equation 28**

$$T_J = T_A + Rth_{J-A} \cdot P_{TOT}$$

where  $T_A$  is the ambient temperature and  $Rth_{J-A}$  is the thermal resistance junction-to-ambient. Considering that the device is mounted on board with a good ground plane, that it has a thermal resistance junction-to-ambient ( $Rth_{J-A}$ ) of about 40 °C/W, and an ambient temperature of about 40 °C:

$$T_{.J} = 40 + 1.15 \cdot 40 \cong 86^{\circ}C$$

## 7.4 Short-circuit protection

In overcurrent protection mode, when the peak current reaches the current limit, the device disables the power element and it is able to reduce the conduction time down to the minimum value (approximately 90 nsec typical) to keep the inductor current limited. This is the pulse by pulse current limitation to implement constant current protection feature.

For the ST1S14, the operation of the pulse by pulse current limitation out of the soft start time depends on the FB voltage:

- 300 mV <VFB <1.22 V: the device operates at nominal switching frequency and the current limitation value

- VFB < 300mV: the switching frequency is decreased five times the nominal value (170 kHz = 850 kHz/5) if the current protection is triggered. The frequency foldback helps to prevent the current diverging at low VOUT / high input voltage. The current foldback, which is active out of the soft start time, reduces the stress of the embedded power element and the external power components in case of persistent short circuit at the output. The current foldback is disabled during the soft start time to provide full current capability to charge the output capacitor at the power-up phase. The foldback peak current value is to 1.45 A typical. In overcurrent condition, the duty cycle is strongly</p>

reduced and, in most applications, this is enough to limit the switch current to the active current threshold, nominal or foldback depending on the FB voltage.

The inductor current ripple during ON and OFF phases can be written as:

ON phase

#### **Equation 29**

$$\Delta I_{L\,TON} = \frac{V_{IN} - V_{OUT} - (DCR_L + R_{DSON}) \cdot I}{L} (T_{ON})$$

OFF phase

#### **Equation 30**

$$\Delta I_{L\,TON} = \frac{-(V_D + V_{OUT} + DCR_L \cdot I)}{L} (T_{OFF})$$

where  $V_D$  is the voltage drop across the diode, DCR<sub>L</sub> is the series resistance of the inductor.

The pulse-by-pulse current limitation is effective in implementing constant current protection when:

#### **Equation 31**

$$|\Delta I_{L TON}| = |\Delta I_{L TOFF}|$$

The overcurrent protection is operating over the entire output voltage, which goes from the regulated output voltage ( $V_{O\_SET}$ ) down to GND during heavy short circuit applied at the output.

From *Equation 29* and *Equation 30* we can gather that the implementation of the constant current protection becomes more critical the lower is the  $V_{OUT}$  and the higher is  $V_{IN}$ .

In fact, the voltage applied to the inductor during the OFF time becomes equal to the voltage drop across parasitic components (typically the DCR of the inductor and the  $V_{FW}$  of the free wheeling diode) when VOUT is negligible, while during  $T_{ON}$  the voltage applied the inductor is maximized and it is approximately equal to  $V_{IN}$ . In general the worst case scenario is heavy short-circuit at the output with maximum input voltage.

### 7.4.1 $300 \text{ mV} < V_{FB} < 1.22 \text{ V}$

The nominal output voltage can be written as:

#### **Equation 32**

$$V_{O\_SET} = V_{FB} \cdot \left(1 + \frac{R_1}{R_2}\right) = 1.22 \cdot \left(1 + \frac{R_1}{R_2}\right)$$

From *Equation 32* the voltage can be expressed as:

#### **Equation 33**

$$\left(1 + \frac{R_1}{R_2}\right) = \frac{V_{O\_SET}}{1.22}$$

so the output voltage is:

#### **Equation 34**

$$V_O = V_{FB} \cdot \left(1 + \frac{R_1}{R_2}\right) = V_{FB} \cdot \frac{V_{O\_SET}}{1.22}$$

Equation 29 and 30, in overcurrent conditions, can be simplified to:

#### **Equation 35**

$$\Delta I_{L\,TON} = \frac{V_{IN} - (DCR_L + R_{DSON}) \cdot I}{L} (T_{ON\,MIN}) \cong \frac{V_{IN}}{L} (90 \text{ns})$$

considering T<sub>ON</sub> which has already been reduced to its minimum.

#### **Equation 36**

$$\Delta I_{L \; TOFF} \; = \; \frac{-(V_D + V_{O\_MIN} + DCR_L \cdot I)}{I} (T_{SW} - 90 \, \text{ns}) \cong \frac{-\left(V_D + V_{FB} \cdot \frac{V_{O\_SET}}{1.22} + DCR_L \cdot I\right)}{I} (1.18 \mu \text{s})$$

where T<sub>SW</sub>=1/f<sub>SW</sub> and considering the nominal f<sub>SW</sub>.

The voltage divider introduces a gain factor K between the  $V_{O\_SET}$  and  $V_{FB}$  that affect the effectiveness of the current protection. The worst case scenario is the minimum K, that is the minimum output voltage, over the input voltage (*Chapter 5.2: Minimum output voltage over V<sub>IN</sub> range*).

As a consequence the minimum feedback voltage to keep the inductor current limited over the input voltage range can be expressed making Equation~35 equal to Equation~36 and expressing  $V_O$  SET as given in Equation 1:

#### **Equation 37**

$$V_{FB}(V_{IN}) = 1.22 - \left(\frac{1.22 \cdot T_{SW}}{V_{IN} \cdot T_{ON MIN}} \cdot (V_D + (I_L \cdot DCR))\right)$$

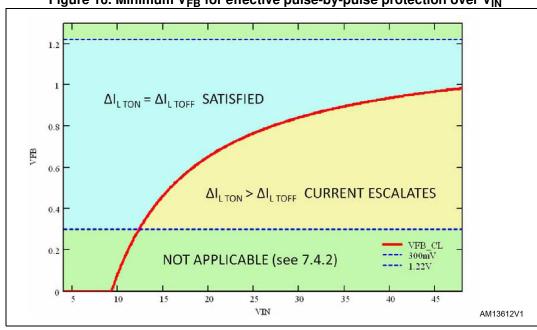

Equation 37 expresses the worst case scenario as it considers the minimum K gain of the voltage divider over the entire input voltage range. The Figure 16 plots the Equation 37 considering the minimum value of the peak current limit given in Table 6: Electrical characteristics on page 8.

Figure 16. Minimum V<sub>FB</sub> for effective pulse-by-pulse protection over V<sub>IN</sub>

As a consequence of  $V_{IN} > 12$  V the pulse-by-pulse current protection (in the worst case scenario which is the minimum  $V_{\mbox{\scriptsize OSET}}$ ) may not be effective to limit the inductor current to the peak current limitation over the entire FB range 300 mV <  $V_{FB}$  < 1.22 V.

In fact, at higher input voltage,  $\Delta I_{L TON}$  may be higher than  $\Delta I_{L TOFF}$  and so the inductor current could escalate. The system typically meets Equation 31 at a current level higher than the nominal value thanks to the voltage drop across stray components.

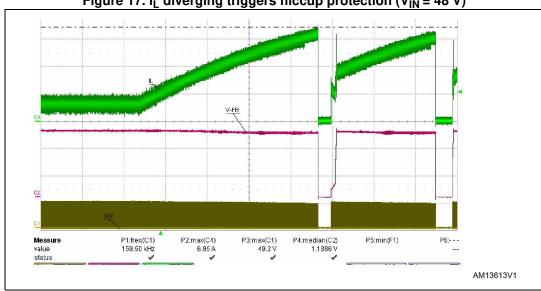

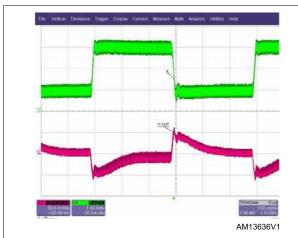

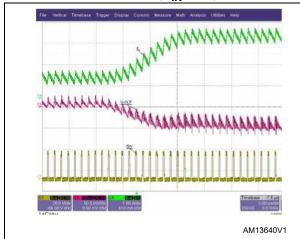

Figure 17. I<sub>L</sub> diverging triggers hiccup protection (V<sub>IN</sub> = 48 V)

In most of the application conditions the pulse-by-pulse current limitation is effective in limiting the inductor current.

Whenever the current escalates, a second level current protection called "hiccup mode" is enabled. In case the hiccup current level (6.2 A typ.) is triggered the switching activity is

prevented for 16 ms and then a new soft-start phase takes place (see *Figure 17*).

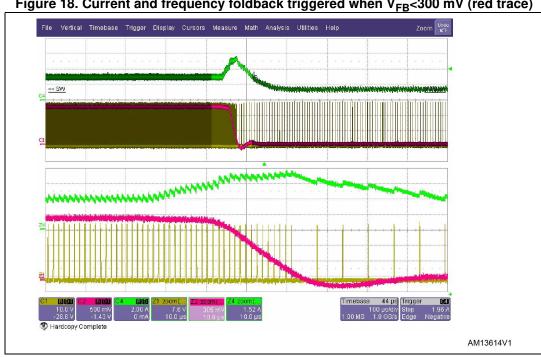

#### 7.4.2 $V_{FB} < 300 \text{ mV}$

The device reduces the switching frequency by five times the nominal value when V<sub>FB</sub><300 mV. The frequency foldback makes the pulse-by-pulse current protection effective to keep the current limited when the output voltage is shorted and V<sub>OUT</sub> negligible.

Equation 29 and 30 in overcurrent conditions can be simplified to:

#### **Equation 38**

$$\Delta I_{L TON} = \frac{V_{IN} - (DCR_L + R_{DSON}) \cdot I}{L} (T_{ON MIN}) \cong \frac{V_{IN}}{L} (90 ns)$$

considering T<sub>ON</sub> which has already been reduced to its minimum.

#### **Equation 39**

$$\Delta I_{L \; TOFF} \; = \; \frac{-(V_D + V_{O\_MIN} + DCR_L \cdot I)}{L} \Big( \frac{T_{SW}}{5} - 90 \, ns \Big) \\ \cong \frac{-\Big(V_D + V_{FB} \cdot \frac{V_{O\_SET}}{1.22} + DCR_L \cdot I\Big)}{L} (5.9 \mu s)$$

taking into consideration the frequency foldback feature.

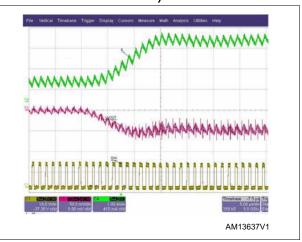

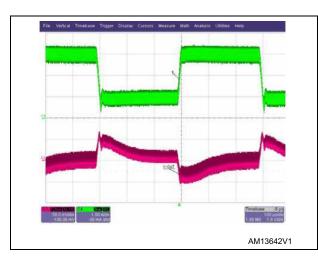

Figure 18. Current and frequency foldback triggered when V<sub>FB</sub><300 mV (red trace)

The content given in Section 7.4.1 is valid and the equivalent expression of Equation 37 is:

#### **Equation 40**

$$V_{FB}(V_{IN}) = \frac{1.22}{5} - \left(\frac{1.22 \cdot T_{SW}}{V_{IN} \cdot T_{ON\_MIN}} \cdot (V_D + (I_L \cdot DCR))\right)$$

The *Figure 19* plots the *Equation 40* considering the foldback current limitation threshold (1.45A) given in *Table 6: Electrical characteristics* which is active out of the soft start time.

Equation 40 expresses the worst case scenario as it considers the minimum K gain of the voltage divider over the entire input voltage range (see *Figure 14*).

In most of the application conditions the pulse by pulse current limitation with frequency foldback is effective to limit the inductor current in short circuit condition. The current foldback helps to decrease the power component stress in persistent short circuit condition out of the sift start time.

The hiccup protection offers an additional protection against heavy short circuit condition at very high input voltage even considering the spread of the minimum conduction time of the power element. In case the hiccup current level (6.2 A typical) is triggered the switching activity is prevented for 15 ms and then a new soft start phase takes place.

*Figure 20* shows the effectiveness of the constant current protection limiting the inductor current to the peak current of 1.45 A typ. during a short circuit event.

*Figure 21* shows the operation of the constant current protection when a short-circuit is applied at the output at the maximum input voltage. According to *Figure 20*, the maximum inductor current escalates over the foldback current limitation.

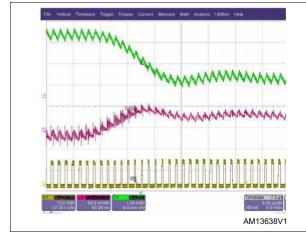

### 7.4.3 Start up phase in short circuit condition

The start up phase in short circuit condition rapresents a preparatory example to show the current protection strategy.

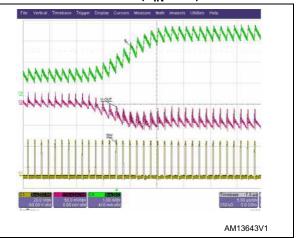

*Figure 25* shows the first switching pulses at power up when the switch current rises but is lower than the current protection level, called OCP1. As a consequence the switching frequency is not reduced.

Figure 22. Start up in short circuit condition

As soon as the current escalates to the current protection threshold (OCP1) the switching frequency is foldback 5 times the nomimal value. The OCP1 threshold is not foldback even if the VFB v< 300 mV (see *Chapter 7.4.2*) because the device is operating in soft start time.

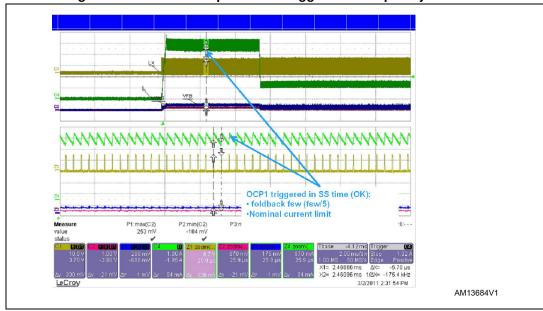

Figure 23. Over current protection triggers the frequency foldback

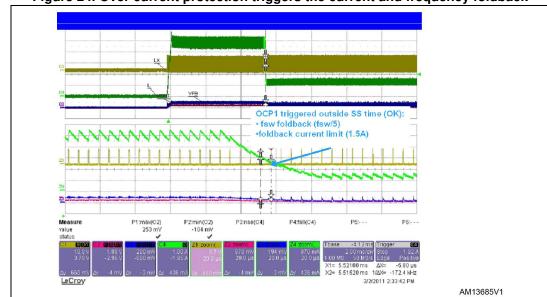

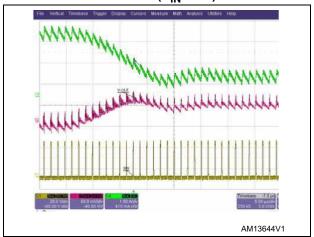

Out of soft start time the device support frequency and current foldback operation to keep the siwtch current limited and reduce the stress of the power components.

Figure 24. Over current protection triggers the current and frequency foldback

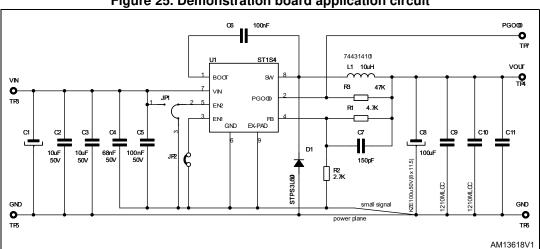

#### 7.5 **Application circuit**

Figure 25. Demonstration board application circuit

Table 11. Component list

| Reference | Part number     | Description                | Manufacturer |

|-----------|-----------------|----------------------------|--------------|

| C2, C3    | UMK325BJ106MM-T | 10 μF 50 V<br>(size 1210)  | Taiyo Yuden  |

| C6, C6    |                 | 100 nF 50 V<br>(size 0603) |              |

Table 11. Component list (continued)

| Reference        | Part number        | Description                                                                         | Manufacturer    |

|------------------|--------------------|-------------------------------------------------------------------------------------|-----------------|

| C7               |                    | 150 pF 50 V<br>(size 0603)                                                          |                 |

| C8               | EKZE500ESS101MHB5D | 100 μF 50 V<br>(size 8 x 11.5 mm)                                                   | Nippon Chemicon |

| C1, C9, C10, C11 |                    | Not Mounted                                                                         |                 |

| R1               |                    | 4.7 KΩ<br>(size 0603)                                                               |                 |

| R2               |                    | 2.7 KΩ<br>(size 0603)                                                               |                 |

| R3               |                    | 47 KΩ<br>(size 0603)                                                                |                 |

| D1               | STPS3L60U          | 3 A 60 V<br>(size SMB)                                                              | ST              |

| L1               | 744314850          | 8.5 μH<br>I <sub>SAT</sub> =4.5 A, I <sub>RMS</sub> =4 A<br>(size 7 x 6.9 x 4.8 mm) | Wurth           |

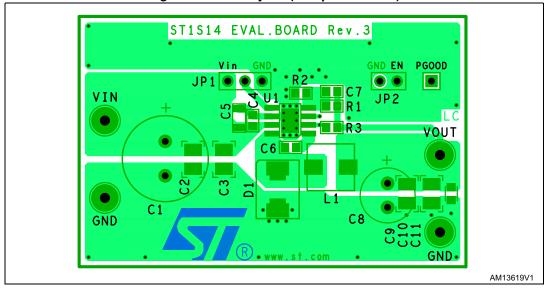

Figure 26. PCB layout (component side)

36/46 DocID17977 Rev 3

AM13620V1

Figure 27. PCB layout (bottom side)

# 8 Typical characteristics

Figure 28. Line regulation

3.34

3.33

3.32

3.31

3.32

3.29

3.28

3.27

—IOUT 1A —IOUT 2A —IOUT 3A

3.26

Figure 29. Load regulation

Figure 30.  $R_{DSon}$  vs. temperature ( $V_{IN}$  = 12 V)

$V_{IN}[V]$

Figure 31.  $V_{FB}$  vs. temperature ( $V_{IN}$  = 12 V)

Figure 32. f<sub>SW</sub> vs. temperature

1.5 YEL 1

Figure 33. Quiescent current vs. temperature

MAX

VIN 48V

Figure 34. Shutdown current vs. temperature

Figure 35. Duty cycle max vs. temperature

Figure 36. Efficiency vs.  $I_{OUT}(V_{IN} 12 V)$

Figure 37.  $T_J$  vs.  $I_{OUT}$  ( $V_{IN}$  12 V)

Figure 38. Efficiency vs. I<sub>OUT</sub> (V<sub>IN</sub> 24 V)

Figure 39.  $T_J$  vs.  $I_{OUT}$  ( $V_{IN}$  24 V)

Figure 40. Efficiency vs.  $I_{OUT}$  ( $V_{IN}$  32 V)

Figure 41.  $T_J$  vs.  $I_{OUT}$  ( $V_{IN}$  32 V)

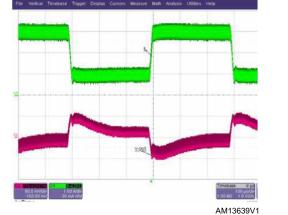

Figure 42. 1 A to 3 A load transient ( $V_{IN}$  12 V) Figure 43. Zoom - 1 A to 3 A load transient ( $V_{IN}$  12 V)

Figure 44. Zoom - 1 A to 3 A rising edge load transient (V<sub>IN</sub> 12 V)

Figure 45. 1 A to 3 A falling edge load transient (V<sub>IN</sub> 24 V)

40/46 DocID17977 Rev 3

Figure 46. Zoom - 1 A to 3 A rising edge load transient (V<sub>IN</sub> 24 V)

Figure 47. Zoom - 1 A to 3 A falling edge load transient (V<sub>IN</sub> 24 V)

File Verical Trinebase Trigger Display Cursors Measure Math Ashaptis Utilities Help

Figure 48. 1 A to 3 A load transient ( $V_{IN}$  32 V)

Figure 49. Zoom - 1 A to 3 A rising edge load transient ( $V_{\text{IN}}$  32 V)

Figure 50. Zoom - 1 A to 3 A falling edge load transient (V<sub>IN</sub> 32 V)

# 9 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

42/46 DocID17977 Rev 3

Table 12. HSOP8 mechanical data

| Dim. | mm   |      |      |

|------|------|------|------|

|      | Min. | Тур. | Max. |

| Α    |      |      | 1.75 |

| A1   |      |      | 0.15 |

| A2   | 1.25 |      |      |

| b    | 0.38 |      | 0.51 |

| С    | 0.17 |      | 0.25 |

| D    | 4.80 | 4.90 | 5.00 |

| D1   | 3.10 | 3.30 | 3.50 |

| E    | 5.80 | 6.00 | 6.20 |

| E1   | 3.80 | 3.90 | 4.00 |

| E2   | 2.20 | 2.40 | 2.60 |

| е    |      | 1.27 |      |

| h    | 0.30 |      | 0.50 |

| L    | 0.45 |      | 0.80 |

| k    | 0°   |      | 8°   |

Order code ST1S14

# 10 Order code

Table 13. Ordering information

| Order code | Package             | Packaging     |

|------------|---------------------|---------------|

| ST1S14PHR  | HSOP8 - exposed pad | Tape and reel |

ST1S14 Revision history

# 11 Revision history

Table 14. Document revision history

| Date        | Revision | Changes                                                                                                            |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------|

| 12-Nov-2010 | 1        | Initial release                                                                                                    |

| 04-Mar-2013 | 2        | Updated I <sub>EN2</sub> current limit. Updated Section 4.3: Soft-start and Section 7.4: Short-circuit protection. |

| 01-Dec-2020 | 3        | Updated Figure 28 and Figure 29.                                                                                   |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2020 STMicroelectronics - All rights reserved

46/46 DocID17977 Rev 3