UCD90320U

ZHCSJE0-SEPTEMBER 2018

# UCD90320U 32 轨 PMBus™ 电源序列发生器和系统管理器

Technical

Documents

🥭 Tools &

Software

# 1 特性

- 超低阿尔法 (ULA) 塑封料可减少由阿尔法粒子造成 的软错误

- 单粒子翻转 (SEU) 检测

- 可对 24 个电压轨和 8 个数字轨进行排序、监视和 裕度调节

- 过压 (OV)、欠压 (UV)、过流 (OC)、欠流 (UC)、 过热、超时以及通用输入 (GPI) 触发的故障

- 提供灵活的排序开启/关闭相关性、延时、布尔逻辑 和通用输入输出 (GPIO) 配置以支持复杂的排序 应 用

- 四个适用于自适应电压识别 (AVID) 稳压器的电源 轨配置文件

- 高精度闭环裕度调节

- 主动微调功能,可改善电源轨输出电压精度

- 高级非易失性事件记录功能,可协助系统调试

- 单一事件故障记录(100个条目)

- 峰值记录

- 黑盒故障记录,用于在首次发生故障时保存所有 电源轨和 I/O 引脚的状态

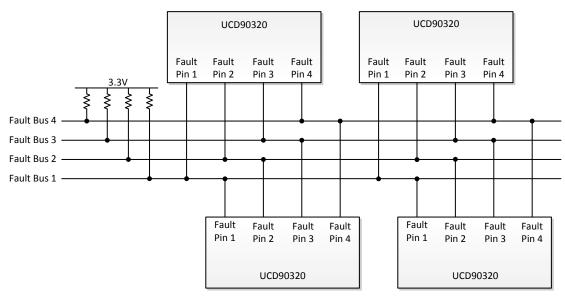

- 可轻松级联多达4个电源序列发生器并加以协调以 提供故障响应

- 可编程的看门狗定时器和系统复位

# 2 应用

- 工业和自动测试设备 (ATE)

- 电信及网络设备

- 服务器和存储系统

- 需要对多个电源轨进行排序和监视的系统

# 3 说明

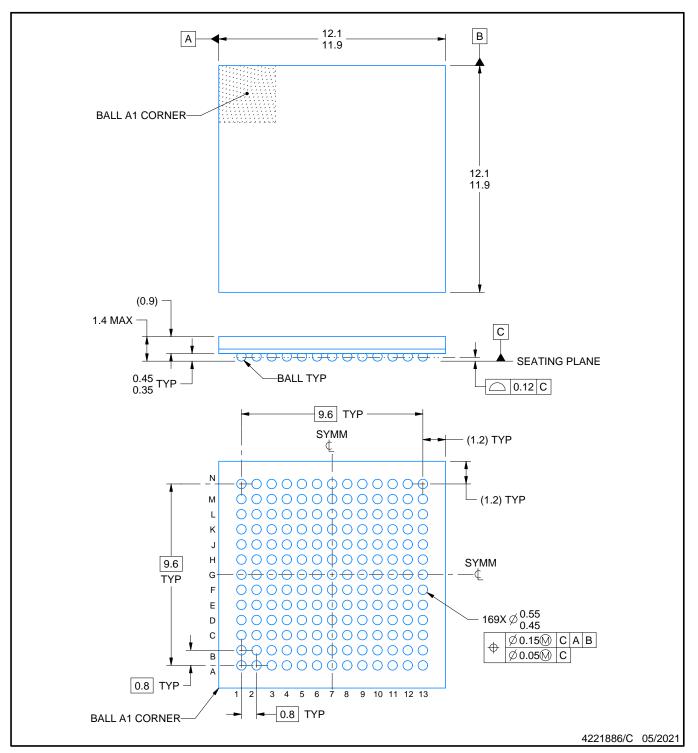

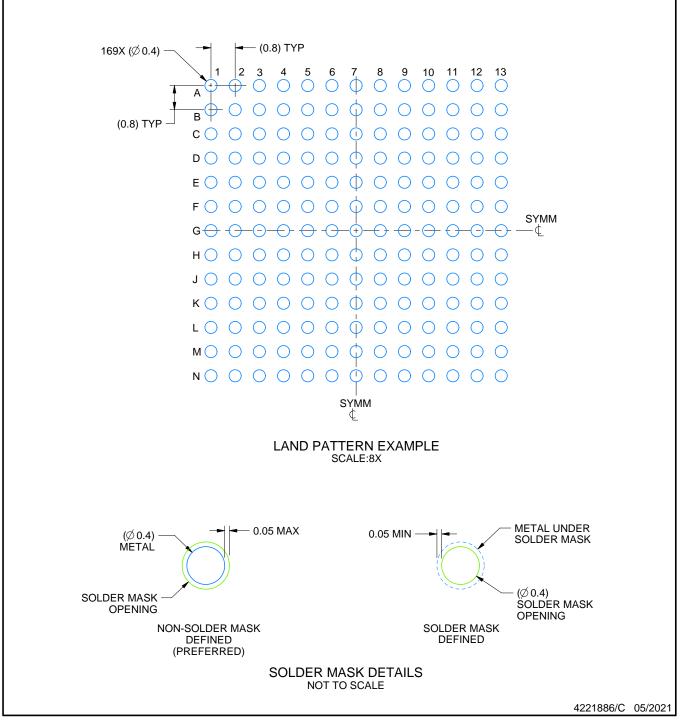

UCD90320U 器件是 32 轨 PMBus<sup>™</sup>可寻址电源序列 发生器和系统管理器,采用 0.8mm 间距 BGA 封装。 采用 ULA 塑封材料减少由阿尔法粒子造成的软错误。 该器件可通过扫描用户配置 SRAM 检测单粒子翻转 (SEU)。两种 特性 都可以为应用提供更高的 可靠性提 供足够的间距。

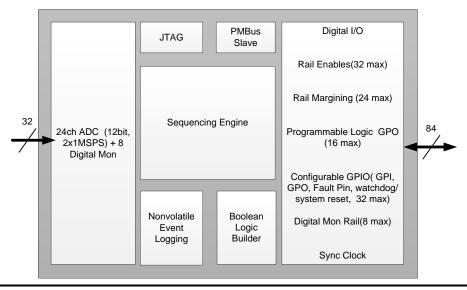

24 条集成 ADC 通道 (AMONx) 监视电源电压、电流和 温度。在 84 个 GPIO 引脚中, 8 个可用作数字监视器 (DMONx), 32 个可支持电源 (ENx), 24 个用于裕量调 节 (MARx), 16 个用于逻辑 GPO, 32 个 GPI 用于级 联和系统功能。

32 个 ENx 引脚和 16 个 LGPOx 引脚可配置为电平有 效驱动或开漏输出。

非易失性事件记录功能可在电源断电后保存故障事件。 黑盒故障记录功能会在首次发生故障后保存所有电源轨 和 I/O 引脚的状态。凭借级联功能,通过一条 SYNC\_CLK 引脚连接即可轻松管理多达 128 个电压 轨。

Support &

Community

22

| 器件信息( | 1) |

|-------|----|

|-------|----|

| 器件型号      | 封装        | 封装尺寸(标称值)       |  |  |  |

|-----------|-----------|-----------------|--|--|--|

| UCD90320U | BGA (169) | 12.0mm x 12.0mm |  |  |  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

| 1<br>2<br>3<br>4 | 应用<br>说明 |                                                         |

|------------------|----------|---------------------------------------------------------|

| 5                | 说明       |                                                         |

| 6                |          | Configuration and Functions 3                           |

| 7                | Spe      | cifications8                                            |

|                  | 7.1      | Absolute Maximum Ratings 8                              |

|                  | 7.2      | ESD Ratings 8                                           |

|                  | 7.3      | Recommended Operating Conditions 8                      |

|                  | 7.4      | Thermal Information 9                                   |

|                  | 7.5      | Electrical Characteristics9                             |

|                  | 7.6      | Non-Volatile Memory Characteristics 10                  |

|                  | 7.7      | I <sup>2</sup> C/PMBus Interface Timing Requirements 11 |

|                  | 7.8      | Typical Characteristics 12                              |

| 8                | Deta     | ailed Description 13                                    |

|                  | 8.1      | Overview 13                                             |

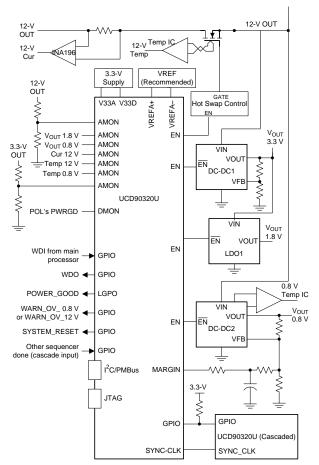

|                  | 8.2      | Functional Block Diagram 13                             |

# 目录

|    | 8.3  | Feature Description                  | . 14 |

|----|------|--------------------------------------|------|

|    | 8.4  | Device Functional Modes              | . 15 |

|    | 8.5  | Device Configuration and Programming | . 41 |

| 9  | Appl | ication and Implementation           | . 44 |

|    | 9.1  | Application Information              | . 44 |

|    |      | Typical Application                  |      |

| 10 | Pow  | er Supply Recommendations            | . 47 |

| 11 |      | put                                  |      |

|    |      | Layout Guidelines                    |      |

|    |      | Layout Example                       |      |

| 12 |      | 和文档支持                                |      |

|    | 12.1 | 社区资源                                 | . 49 |

|    | 12.2 | 接收文档更新通知                             | . 49 |

|    | 12.3 | 商标                                   | . 49 |

|    | 12.4 | 静电放电警告                               | . 49 |

|    | 12.5 | 术语表                                  | . 49 |

| 13 | 机械   | 、封装和可订购信息                            | . 49 |

|    |      |                                      |      |

**4 修订历史记录** 注: 之前版本的页码可能与当前版本有所不同。

| 日期         | 修订版本 | 说明     |

|------------|------|--------|

| 2018 年 9 月 | *    | 初始发行版。 |

2

www.ti.com.cn

# 5 说明 (续)

**FAULT** 引脚可以协调级联器件,使其对故障做出同步响应。引脚选择电源轨状态功能使用多达 3 个 GPI 控制多达 八个用户定义的电源状态。这些状态可实现*高级配置和电源接口* (ACPI) 规范中列出的系统低功耗模式。

TI Fusion Digital Power™设计软件是一款基于 PC 的直观图形用户界面 (GUI),可对所有系统工作参数进行配置、存储和监视。

# 6 Pin Configuration and Functions

|   | ZWS Package<br>169-Pin BGA<br>Top View |                |         |          |            |            |            |            |       |                 |                 |                 |                 |   |

|---|----------------------------------------|----------------|---------|----------|------------|------------|------------|------------|-------|-----------------|-----------------|-----------------|-----------------|---|

|   | 1                                      | 2              | 3       | 4        | 5          | 6          | 7          | 8          | 9     | 10              | 11              | 12              | 13              |   |

| A | DVSS                                   | Unused-<br>NC  | (AMON6) | AMON8    | AMON1<br>0 | AMON1<br>2 | AMON2<br>2 | AMON2<br>4 | LGP03 | JTAG_T<br>MS    | JTAG_T<br>DO    | GPIO4           | MAR15           | A |

| В | AMON1<br>5                             | AMON1<br>6     |         | AMON7    | AMON9      | AMON1<br>1 | AMON2<br>1 | AMON2<br>3 | LGPO2 | JTAG_T<br>DI    | GPI01           | GPIO2           | MAR16           | В |

| С | AMON1<br>3                             | (AMON1<br>4    | AVSS    | LGPO8    | LGPO6      | LGP07      | DVSS       | LGPO4      | LGP01 | JTAG_T<br>CK    | GPIO3           | (MAR14)         | MAR18           | С |

| D | VREFA-                                 | VREFA+         | V33A    | MAR5     | LGPO5      | BPCap      | V33D       | (MAR3)     | DVSS  | DMON4           | (MAR13)         | (MAR17)         |                 | D |

| E |                                        |                | AVSS    | MAR6     | DVSS       | V33D       | DVSS       | V33D       | V33D  |                 | PMBUS           | (MAR19)         | MAR20           | E |

| F | (AMON4)                                |                |         |          | MAR7       | DVSS       | DVSS       | DVSS       | DVSS  | V33D            | PMB<br>ALERT#   | EN26            | EN25            | F |

| G | (AMON1<br>8                            | (AMON1<br>7    |         | EN24     | DVSS       | DVSS       | DVSS       | DVSS       | DVSS  | RESET           | EN27            | Unused-<br>DVSS | Unused-<br>NC   | G |

| Н | (AMON1<br>9                            | (AMON2<br>0    | EN23    | EN22     | DVSS       | DVSS       | DVSS       | DVSS       | DVSS  | EN28            | EN31            | EN30            | EN29            | Н |

| J | BPCap                                  | EN20           | EN21    | EN19     | DVSS       | BPCap      | V33D       | DVSS       | V33D  | V33D            | DVSS            | (MAR24)         | (MAR1)          | J |

| к | PMBUS<br>ADDR2                         | SYNC_<br>CLK   | EN17    | EN18     | MAR10      | (MAR4)     | EN13       | EN10       | EN6   | EN4             | Unused-<br>DVSS | Unused-<br>V33D | BPCap           | К |

| L | PMBUS<br>ADDR1                         | PMBUS<br>ADDR0 | (LGPO9) | (LGPO13) | MAR2       | (MAR12)    | EN14       | EN9        | EN5   | EN3             |                 | (MAR22)         | EN32            | L |

| М | LGPO10                                 | (LGPO11)       | LGPO12  | (LGPO15) | MAR23      | (MAR11)    | EN12       | EN8        | EN1   | Unused-<br>DVSS |                 | Unused-<br>NC   | (MAR21)         | Μ |

| Ν | LGPO14                                 | LGPO16         | EN16    | EN15     | MAR8       | (MAR9)     | EN11       | EN7        | EN2   | Unused-<br>NC   |                 |                 | Unused-<br>DVSS | N |

|   | 1                                      | 2              | 3       | 4        | 5          | 6          | 7          | 8          | 9     | 10              | 11              | 12              | 13              |   |

UCD90320U ZHCSJE0-SEPTEMBER 2018

www.ti.com.cn

|                | Pin Functions         |     |                                                           |  |  |  |  |

|----------------|-----------------------|-----|-----------------------------------------------------------|--|--|--|--|

| PIN            |                       | 1/0 | DESCRIPTION                                               |  |  |  |  |

| NAME           | NO.                   |     | DESCRIPTION                                               |  |  |  |  |

| ANALOG MONITOR | R PINS <sup>(1)</sup> |     |                                                           |  |  |  |  |

| AMON1          | E2                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON2          | E1                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON3          | F2                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON4          | F1                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON5          | B3                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON6          | A3                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON7          | B4                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON8          | A4                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON9          | B5                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON10         | A5                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON11         | B6                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON12         | A6                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON13         | C1                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON14         | C2                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON15         | B1                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON16         | B2                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON17         | G2                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON18         | G1                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON19         | H1                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON20         | H2                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON21         | B7                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON22         | A7                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON23         | B8                    | I   | Analog input monitor pin                                  |  |  |  |  |

| AMON24         | A8                    | I   | Analog input monitor pin                                  |  |  |  |  |

| ENABLE PINS    |                       |     |                                                           |  |  |  |  |

| EN1(GPIO)      | M9                    | I/O | Digital output, rail enable signal or GPIO <sup>(2)</sup> |  |  |  |  |

| EN2(GPIO)      | N9                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN3(GPIO)      | L10                   | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN4(GPIO)      | K10                   | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN5(GPIO)      | L9                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN6(GPIO)      | K9                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN7(GPIO)      | N8                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN8(GPIO)      | M8                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN9(GPIO)      | L8                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN10(GPIO)     | K8                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN11(GPIO)     | N7                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN12(GPIO)     | M7                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN13(GPIO)     | K7                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN14(GPIO)     | L7                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN15(GPIO)     | N4                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN16(GPIO)     | N3                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN17(GPIO)     | K3                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN18(GPIO)     | K4                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

| EN19(GPIO)     | J4                    | I/O | Digital output, rail enable signal or GPIO                |  |  |  |  |

...

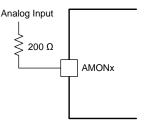

TI recommends placing a 200-Ω resistor between analog input and monitor pins.

GPIO: GPI, Command GPO, WDI, WDO, system reset (RESET), FAULT pin for multiple chip cascading

# Pin Functions (continued)

| PIN                     |           | 1/0 | DECODIDION                                    |  |  |  |  |

|-------------------------|-----------|-----|-----------------------------------------------|--|--|--|--|

| NAME                    | NO.       | I/O | DESCRIPTION                                   |  |  |  |  |

| EN20(GPIO)              | J2        | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN21(GPIO)              | J3        | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN22(GPIO)              | H4        | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN23(GPIO)              | H3        | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN24(GPIO)              | G4        | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN25(GPIO)              | F13       | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN26(GPIO)              | F12       | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN27(GPIO)              | G11       | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN28(GPIO)              | H10       | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN29(GPIO)              | H13       | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN30(GPIO)              | H12       | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN31(GPIO)              | H11       | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| EN32(GPIO)              | L13       | I/O | Digital output, rail enable signal or GPIO    |  |  |  |  |

| CLOSED-LOOP MA          | RGIN PINS |     |                                               |  |  |  |  |

| MAR1(GPIO)              | J13       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR2(GPIO)              | L5        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR3(GPIO)              | D8        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR4(GPIO)              | K6        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR5(GPIO)              | D4        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR6(GPIO)              | E4        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR7(GPIO)              | F5        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR8(GPIO)              | N5        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR9(GPIO)              | N6        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR10(GPIO)             | K5        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR11(GPIO)             | M6        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR12(GPIO)             | L6        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR13(GPIO)             | D11       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR14(GPIO)             | C12       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR15(GPIO)             | A13       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR16(GPIO)             | B13       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR17(GPIO)             | D12       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR18(GPIO)             | C13       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR19(GPIO)             | E12       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR20(GPIO)             | E13       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR21(GPIO)             | M13       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR22(GPIO)             | L12       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR23(GPIO)             | M5        | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| MAR24(GPIO)             | J12       | I/O | Closed-loop margin PWM output or General GPIO |  |  |  |  |

| GPIO AND CASCADING PINS |           |     |                                               |  |  |  |  |

| DMON1(GPIO)             | F4        | I/O | Digital input monitor pin or GPIO             |  |  |  |  |

| DMON2(GPIO)             | F3        | I/O | Digital input monitor pin or GPIO             |  |  |  |  |

| DMON3(GPIO)             | G3        | I/O | Digital input monitor pin or GPIO             |  |  |  |  |

| DMON4(GPIO)             | D10       | I/O | Digital input monitor pin or GPIO             |  |  |  |  |

| DMON5(GPIO)             | L11       | I/O | Digital input monitor pin or GPIO             |  |  |  |  |

| DMON6(GPIO)             | N12       | I/O | Digital input monitor pin or GPIO             |  |  |  |  |

| DMON7(GPIO)             | N11       | I/O | Digital input monitor pin or GPIO             |  |  |  |  |

# Pin Functions (continued)

| PIN             |                                        |          |                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|----------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.                                    | I/O      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          |

| DMON8(GPIO)     | M11                                    | I/O      | Digital input monitor pin or GPIO                                                                                                                                                                                                                                                                                                                                    |

| GPIO            |                                        |          |                                                                                                                                                                                                                                                                                                                                                                      |

| GPIO1           | B11                                    | I/O      | GPIO                                                                                                                                                                                                                                                                                                                                                                 |

| GPIO2           | B12                                    | I/O      | GPIO                                                                                                                                                                                                                                                                                                                                                                 |

| GPIO3           | C11                                    | I/O      | GPIO                                                                                                                                                                                                                                                                                                                                                                 |

| GPIO4           | A12                                    | I/O      | GPIO                                                                                                                                                                                                                                                                                                                                                                 |

| SYNC_CLK        | K2                                     | I/O      | Synchronization clock I/O for multiple chip cascading                                                                                                                                                                                                                                                                                                                |

| LOGIC GPO PINS  |                                        |          |                                                                                                                                                                                                                                                                                                                                                                      |

| LGPO1(GPIO)     | C9                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO2(GPIO)     | B9                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO3(GPIO)     | A9                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO4(GPIO)     | C8                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO5(GPIO)     | D5                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO6(GPIO)     | C5                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO7(GPIO)     | C6                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO8(GPIO)     | C4                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO9(GPIO)     | L3                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO10(GPIO)    | M1                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO11(GPIO)    | M2                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO12(GPIO)    | M3                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO13(GPIO)    | L4                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO14(GPIO)    | N1                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO15(GPIO)    | M4                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| LGPO16(GPIO)    | N2                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                                    |

| PMBus COMM INT  | ERFACE                                 |          |                                                                                                                                                                                                                                                                                                                                                                      |

| PMBUS_CLK       | E10                                    | Ι        | PMBus clock (must pull up to V33D)                                                                                                                                                                                                                                                                                                                                   |

| PMBUS_DATA      | D13                                    | I/O      | PMBus data (must pull up to V33D)                                                                                                                                                                                                                                                                                                                                    |

| PMBALERT        | F11                                    | 0        | PMBus alert, active-low, open-drain output (must pull up to V33D)                                                                                                                                                                                                                                                                                                    |

| PMBUS_CNTRL     | E11                                    | I        | PMBus control pin                                                                                                                                                                                                                                                                                                                                                    |

| PMBUS_ADDR0     | L2                                     | Ι        | PMBus digital address input. Bit 0                                                                                                                                                                                                                                                                                                                                   |

| PMBUS_ADDR1     | L1                                     | Ι        | PMBus digital address input. Bit 1                                                                                                                                                                                                                                                                                                                                   |

| PMBUS_ADDR2     | K1                                     | Ι        | PMBus digital address input. Bit 2                                                                                                                                                                                                                                                                                                                                   |

| JTAG            |                                        |          |                                                                                                                                                                                                                                                                                                                                                                      |

| JTAG_TMS        | A10                                    | Ι        | Test mode select with internal pull-up                                                                                                                                                                                                                                                                                                                               |

| JTAG_TCK        | C10                                    | Ι        | Test clock with internal pull-up                                                                                                                                                                                                                                                                                                                                     |

| JTAG_TDO        | A11                                    | 0        | Test data out with internal pull-up                                                                                                                                                                                                                                                                                                                                  |

| JTAG_TDI        | B10                                    | Ι        | Test data in with internal pull-up                                                                                                                                                                                                                                                                                                                                   |

| INPUT POWER, GI | ROUND, AND I                           | EXTERNAL | REFERENCE PINS                                                                                                                                                                                                                                                                                                                                                       |

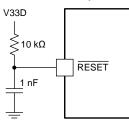

| RESET           | G10                                    | Ι        | Active-low device reset input. Pull up to V33D.                                                                                                                                                                                                                                                                                                                      |

| V33A            | D3                                     | Ι        | Analog 3.3-V supply. Decouple from V33D to minimize the electrical noise contained on V33D from affecting the analog functions.                                                                                                                                                                                                                                      |

| V33D            | D7, E6, E8,<br>E9, F10, J7,<br>J9, J10 | I        | Digital 3.3-V supply for I/O and some logic.                                                                                                                                                                                                                                                                                                                         |

| ВРСар           | D6, J1, J6,<br>K13                     | I        | Positive supply for most of the logic function, including the processor core and most peripherals. The voltage on this pin is 1.2 V and is supplied by the on-chip LDO. The BPCap pins should only be connected to each other and an external capacitor as specified in <i>On-Chip Low Drop-Out (LDO) Regulator</i> section of the Electrical Characteristics table. |

# Pin Functions (continued)

| PIN         |                                                                                                              | 1/0 | DESCRIPTION                                                                                                                          |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME        | NO.                                                                                                          | I/O | DESCRIPTION                                                                                                                          |  |  |  |

| AVSS        | C3, E3                                                                                                       | Ι   | Analog ground. These are separated from DVSS to minimize the electrical noise contained on V33D from affecting the analog functions. |  |  |  |

| DVSS        | A1, C7, D9,<br>E5, F9, H5,<br>H9, J5, J8,<br>J11, H6,<br>H7, H8, G5,<br>G6, G7, G8,<br>G9, F6, F7,<br>F8, E7 | I   | Ground reference for logic and I/O pins.                                                                                             |  |  |  |

| VREFA+      | D2                                                                                                           | I   | (Optional) positive node of external reference voltage                                                                               |  |  |  |

| VREFA-      | D1                                                                                                           | Ι   | (Optional) negative node of external reference voltage                                                                               |  |  |  |

| UNUSED PINS |                                                                                                              |     |                                                                                                                                      |  |  |  |

| UNUSED-NC   | A2, G13,<br>M12, N10                                                                                         | -   | Do not connect. Leave floating or isolated.                                                                                          |  |  |  |

| UNUSED-DVSS | G12, K11,<br>M10, N13                                                                                        | _   | Tie to DVSS.                                                                                                                         |  |  |  |

| UNUSED-V33D | K12                                                                                                          | -   | Tie to V33D.                                                                                                                         |  |  |  |

# 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                                                                                                                                  | MIN  | MAX                     | UNIT |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-------------------------|------|

| Cupply voltogo                                 | V33D to DVSS                                                                                                                     | 0    | 4                       | V    |

| Supply voltage                                 | V33A to AVSS                                                                                                                     | 0    | 4                       | V    |

| Input voltage                                  | on all I/O pins except PMBUS_CNTRL, PMBALERT, MARGIN19, and MARGIN20, regardless of whether the device is powered <sup>(2)</sup> | -0.3 | 5.5                     | V    |

| Input voltage                                  | PMBUS_CNTRL, PMBALERT, MARGIN19, and MARGIN20                                                                                    | -0.3 | V <sub>V33D</sub> + 0.3 | V    |

| Output current                                 | Maximum current per output pin                                                                                                   |      | 25                      | mA   |

| Operating junction temperature, T <sub>J</sub> |                                                                                                                                  | TBD  | 150                     | °C   |

| Storage temperatur                             | re, T <sub>stg</sub>                                                                                                             | -65  | 150                     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those listed in the Recommended Operating Conditions table. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Applies to static and dynamic signals including overshoot.

# 7.2 ESD Ratings

|                 |                          |                                                                                | VALUE | UNIT |

|-----------------|--------------------------|--------------------------------------------------------------------------------|-------|------|

| V               |                          | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | N/   |

| V <sub>(E</sub> | <sup>SD)</sup> discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                  |                                | MIN  | NOM | MAX  | UNIT |

|----------------------------------|--------------------------------|------|-----|------|------|

| V <sub>V33D</sub>                | Cumply input veltage           | 3.15 | 3.3 | 3.63 | V    |

| V <sub>V33A</sub> <sup>(1)</sup> | Supply input voltage           | 2.97 | 3.3 | 3.63 | V    |

| T <sub>A</sub>                   | Operating ambient temperature  | -40  |     | 85   | °C   |

| T <sub>C</sub>                   | Operating case temperature     | -40  |     | 90   | °C   |

| TJ                               | Operating junction temperature | -40  |     | 93   | °C   |

(1) It is recommended to connect the V33A pin and the V33D pin to the same supply. V33A must be powered before V33D if sourced from different supplies. There is no restriction on the ordering sequence for powering off.

#### 7.4 Thermal Information

|                       |                                                             | UCD90320U |      |

|-----------------------|-------------------------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                               | ZWS (BGA) | UNIT |

|                       |                                                             | 169 PINS  |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance <sup>(2)(3)</sup>    | 41.6      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance <sup>(2)</sup>    | 15.8      | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance <sup>(2)(4)(5)</sup>   | 18.9      | °C/W |

| ΨJT                   | Junction-to-top characterization parameter <sup>(6)</sup>   | 0.3       | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter <sup>(4)</sup> | 20.3      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance                | n/a       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

Junction to ambient thermal resistance ( $\theta_{JA}$ ), junction to board thermal resistance ( $\theta_{JB}$ ), and junction to case thermal resistance ( $\theta_{JC}$ ) (2) numbers are determined by a package simulator.

$\begin{array}{l} T_J = T_A + (P \times \theta_{JA}) \\ T_J = T_{PCB} + (P \times \Psi_{JB}) \\ T_J = T_B + (P \times \theta_{JB})^{(l)} \\ T_J = T_C + (P \times \Psi_{JT}) \end{array}$ (3)

(4)

(5)

(6)

#### 7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                                                                             | TEST CONDITIONS                               | MIN                 | TYP  | MAX                 | UNIT |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------|------|---------------------|------|

| SUPPLY              | CURRENT                                                                                                               |                                               |                     |      | ·                   |      |

| I <sub>V33</sub>    | Supply Current                                                                                                        | V <sub>V33D</sub> = V <sub>V33A</sub> = 3.3 V |                     | 31.4 | 54.9                | mA   |

| ON-CHIP             | LOW DROP-OUT (LDO) REGULATOR                                                                                          |                                               |                     |      | ·                   |      |

| C <sub>LDO</sub>    | External filter capacitor size for internal power supply <sup>(1)</sup>                                               |                                               | 2.5                 |      | 4                   | μF   |

| V <sub>LDO</sub>    | LDO output voltage                                                                                                    |                                               | 1.08                | 1.2  | 1.32                | V    |

| I <sub>INRUSH</sub> | Inrush current                                                                                                        |                                               | 50                  |      | 250                 | mA   |

| ANALOG              | -TO-DIGITAL CONVERTER (ADC) <sup>(2)(3)</sup>                                                                         | •                                             | •                   |      |                     |      |

| V33A                | ADC supply voltage                                                                                                    |                                               | 2.97                | 3.3  | 3.63                | V    |

| AVSS                | ADC ground voltage                                                                                                    |                                               |                     | 0    |                     | V    |

| C <sub>V33A</sub>   | Voltage reference decoupling capacitance between V33A and AVSS (if using internal reference) <sup>(4)</sup>           |                                               |                     | 1.01 |                     | μF   |

| V <sub>REFA+</sub>  | Positive external voltage reference on<br>VREFA+ pin                                                                  |                                               | 2.4                 |      | 3                   | V    |

| V <sub>REFA-</sub>  | Negative external voltage reference on<br>VREFA– pin                                                                  |                                               | V <sub>AVSS</sub>   | AVSS | 0.3                 | V    |

| C <sub>REF</sub>    | Voltage reference decoupling capacitance<br>between VREFA+ and VREFA– (if using<br>external reference) <sup>(4)</sup> |                                               |                     | 1.01 |                     | μF   |

| .,                  | Analog input range, internal reference <sup>(5)</sup>                                                                 |                                               | 0                   |      | V33A                |      |

| V <sub>ADCIN</sub>  | Analog input range, external reference <sup>(6)</sup>                                                                 |                                               | V <sub>VREFA-</sub> |      | V <sub>VREFA+</sub> | V    |

| ۱L                  | ADC input leakage current                                                                                             |                                               |                     |      | 2                   | μA   |

| R <sub>ADC</sub>    | ADC equivalent input resistance                                                                                       |                                               |                     |      | 2.5                 | kΩ   |

| C <sub>ADC</sub>    | ADC equivalent input capacitance                                                                                      |                                               |                     |      | 10                  | pF   |

| F <sub>CONV</sub>   | ADC conversion rate (on each ADC channel) <sup>(1)</sup>                                                              |                                               |                     | 1    |                     | MSPS |

Connect the capacitor as close as possible to pin D6. (1)

Total of two ADC channels run independently during normal operation. (2)

- Total unadjusted error is the maximum error at any one code versus the ideal ADC curve. It includes offset error, gain error, and INL at (3) any given ADC code.

- Two capacitors (1.0  $\mu F$  and 0.01  $\mu F)$  connected in parallel. (4)

Internal reference is connected directly between V33A and AVSS. (5)

External reference noise level must be under 12 bit (-74 dB) of full scale input, over input bandwidth, measured at VREFA+ - VREFA-. (6)

EXAS ISTRUMENTS

www.ti.com.cn

### **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                                                    | TEST CONDITIONS                        | MIN                         | TYP  | MAX                         | UNIT |

|--------------------|------------------------------------------------------------------------------|----------------------------------------|-----------------------------|------|-----------------------------|------|

| N                  | ADC resolution                                                               |                                        |                             | 12   |                             | bits |

| F                  | Total unadjusted error, over full input rangea when using internal reference |                                        |                             | ±10  | ±30                         | LSB  |

| Ε <sub>T</sub>     | Total unadjusted error, over full input range when using external reference  |                                        |                             | ±2.5 | ±4                          | LOD  |

| DIGITAL IN         | IPUTS AND OUTPUTS (GPIO, Logic GPO, E                                        | EN, AND MARGIN PINS)                   |                             |      |                             |      |

| V <sub>IH</sub>    | I/O high-level input voltage <sup>(7)</sup>                                  |                                        | 0.65 ×<br>V <sub>V33D</sub> |      | 5.5                         | V    |

| V <sub>IL</sub>    | I/O low-level input voltage                                                  |                                        | 0                           |      | 0.35 ×<br>V <sub>V33D</sub> | V    |

| V <sub>HYS</sub>   | I/O input hysteresis                                                         |                                        | 0.2                         |      |                             | V    |

| V <sub>OH</sub>    | I/O high-level output voltage                                                |                                        | 2.4                         |      |                             | V    |

| V <sub>OL</sub>    | I/O low-level output voltage                                                 |                                        |                             |      | 0.4                         | V    |

| I <sub>OH</sub>    | High-level source current                                                    | V <sub>OH</sub> = 2.4 V <sup>(8)</sup> | 4                           |      |                             | mA   |

| I <sub>OL</sub>    | Low-level sink current                                                       | $V_{OL} = 0.4 V^{(8)}$                 | 4                           |      |                             | mA   |

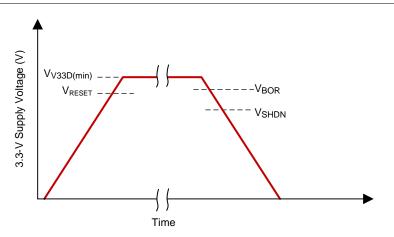

| RESET AN           | D BROWNOUT                                                                   |                                        |                             |      |                             |      |

| V33DSlew           | Minimum V33D slew rate between 2.8 V and 3.2 V                               |                                        | 0.1                         |      |                             | V/ms |

| V <sub>RESET</sub> | Supply voltage at which device comes out of reset                            |                                        | 2                           | 2.3  | 2.6                         | V    |

| V <sub>BOR</sub>   | Supply voltage at which device enters brownout                               |                                        | 2.93                        | 3.02 | 3.11                        | V    |

| V <sub>SHDN</sub>  | Supply voltage at which device shuts down                                    |                                        | 2.7                         | 2.78 | 2.87                        | V    |

| t <sub>RESET</sub> | Minimum low-pulse width needed at RESET pin                                  |                                        |                             | 250  |                             | ns   |

| t <sub>IRT</sub>   | Internal reset time <sup>(9)</sup>                                           |                                        |                             | 9    | 11.5                        | ms   |

(7)

(8)

PMBUS\_CNTRL, PMBALERT, MARGIN19 and MARGIN20 pins have  $V_{V33D}$  + 0.3 V as maximum input voltage rating. Io specifications reflect the maximum current where the corresponding output voltage meets the  $V_{OH}/V_{OL}$  thresholds. If power-loss or brown-out event occurs during an EEPROM program or erase operation, and EEPROM needs to be repaired (which is a (9) rare case), the internal reset time may be longer.

# 7.6 Non-Volatile Memory Characteristics

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                                               | TEST CONDITIONS                          | MIN     | TYP | MAX | UNIT   |  |  |  |  |

|----------------------------|-------------------------------------------------------------------------|------------------------------------------|---------|-----|-----|--------|--|--|--|--|

| CONFIGURATION FLASH MEMORY |                                                                         |                                          |         |     |     |        |  |  |  |  |

| PE <sub>CYC</sub>          | Number of program and erase<br>cycles before failure                    |                                          | 100,000 |     |     | Cycles |  |  |  |  |

| T <sub>RET</sub>           | Data retention                                                          | $-40^{\circ}C \le T_{J} \le 85^{\circ}C$ | 20      |     |     | Years  |  |  |  |  |

| FAULT AN                   | ND EVENT LOGGING EEPROM                                                 |                                          |         |     |     |        |  |  |  |  |

| EPE <sub>CYC</sub>         | Number of mass program and erase cycles of a single word before failure |                                          | 500,000 |     |     | Cycles |  |  |  |  |

| ET <sub>RET</sub>          | Data retention                                                          | –40°C ≤ T <sub>J</sub> ≤ 85°C            | 20      |     |     | Years  |  |  |  |  |

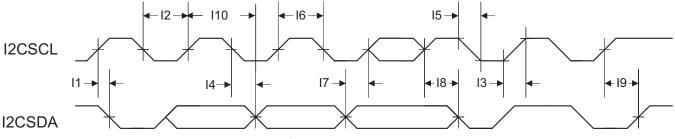

### 7.7 I<sup>2</sup>C/PMBus Interface Timing Requirements

|     |                       |                                                   | MIN | NOM   | MAX                | UNIT |

|-----|-----------------------|---------------------------------------------------|-----|-------|--------------------|------|

| 11  | t <sub>(HD:STA)</sub> | Start condition hold time                         | 450 |       |                    | ns   |

| 12  | t <sub>(LOW)</sub>    | Clock low period <sup>(1)</sup>                   | 450 |       |                    | ns   |

| 13  | t <sub>r</sub>        | Clock rise time and data rise time <sup>(2)</sup> |     |       | See <sup>(2)</sup> | ns   |

| 14  | t <sub>(HD:DAT)</sub> | Data hold time                                    |     | 25    |                    | ns   |

| 15  | t <sub>f</sub>        | Clock fall time and data fall time <sup>(3)</sup> |     | 112.5 | 125                | ns   |

| 16  | t <sub>(HIGH)</sub>   | Clock high time                                   | 300 |       |                    | ns   |

| 17  | t <sub>(SU:DAT)</sub> | Data setup time                                   | 225 |       |                    | ns   |

| 18  | t <sub>(SU:STA)</sub> | Start condition setup time (repeated start only)  | 450 |       |                    | ns   |

| 19  | t <sub>(SU:STO)</sub> | Stop condition setup time                         | 300 |       |                    | ns   |

| l10 | t <sub>(DV)</sub>     | Data valid                                        |     | 25    |                    | ns   |

PMBus host must support clock stretching per PMBus Power System Management Protocol Specification Part I General Requirements, (1) Transport and Electrical Interface, Revision 1.2, Section 5.2.6.

Because the I2CSCL signal and the I2CSDA signal operate as open-drain-type signals, which the controller can actively drive only (2)

"Low", the time that either signal takes to reach a high level depends on external signal capacitance and pull-up resistor values.

Specified at a nominal 50-pF load. (3)

Figure 1. I<sup>2</sup>C/PMBus Timing Diagram

UCD90320U ZHCSJE0-SEPTEMBER 2018

www.ti.com.cn

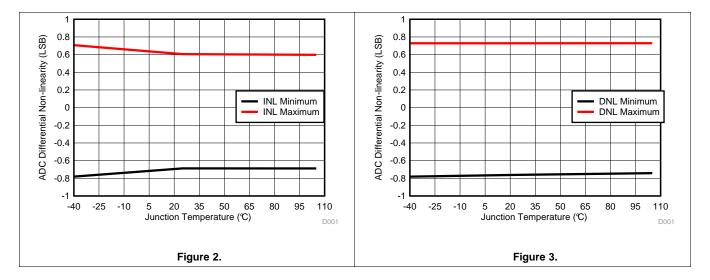

# 7.8 Typical Characteristics

### 8 Detailed Description

#### 8.1 Overview

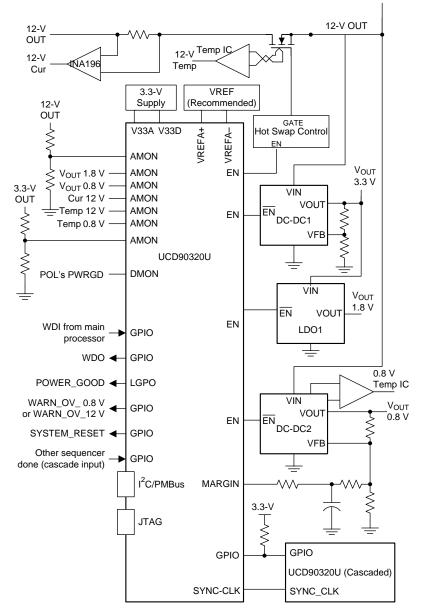

Electronic systems such as CPU, DSP, microcontroller, FPGA, and ASIC can have multiple voltage rails and require certain power-ON and power-OFF sequences in order to function correctly. The UCD90320U device can control up to 32 voltage rails and ensure correct power sequences during normal condition and fault conditions.

In addition to sequencing, the device can continuously monitor rail voltages, currents, temperatures, fault conditions, and report the system health information to upper computers through a PMBus interface, improving long term reliability.

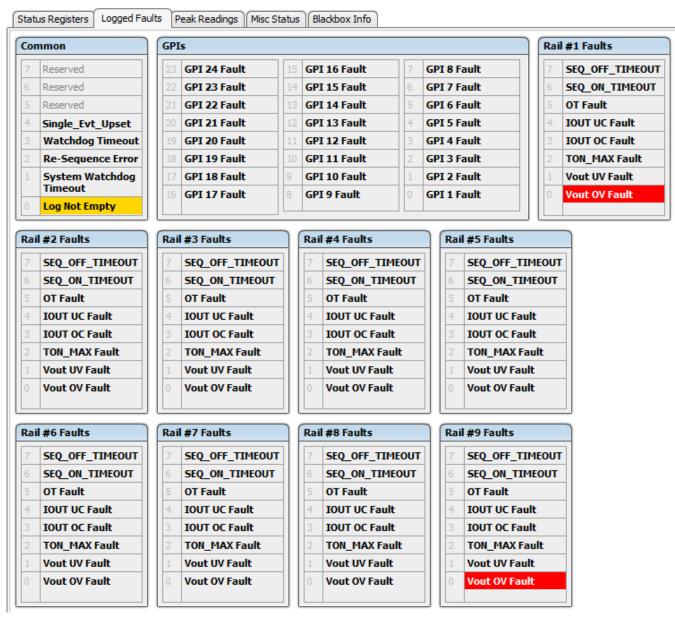

The device can protect electronic systems by responding to power system faults. The fault responses are conveniently configured by users through *Fusion Digital Power Designer* software. Fault events are stored in onchip nonvolatile flash memory in order to assist failure analysis. A Black Box Fault Log feature stores comprehensive system statuses at the moment when the first fault occurs. With this feature, failure analysis can be more effective.

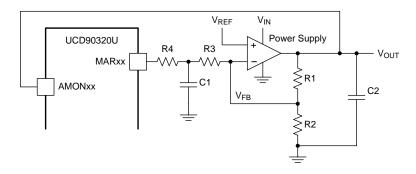

System reliability can be improved through four-corner testing during system verification. During four-corner testing, each voltage rail is required to operate at the minimum and maximum output voltages, commonly known as margining. The device can perform accurate closed-loop margining for up to 24 voltage rails. During normal operation, UCD90320U can also actively trim DC output voltages using the same margining circuitry. This feature allows tuning rail voltages to an optimal level.

The UCD90320U device supports control environments via both PMBus interface and pin-based interface. The device functions as a PMBus slave. It can communicate with upper computers with PMBus commands, and control voltage rails accordingly. In addition to rail enable (EN) pins, up to 32 GPIO pins can be configured as GPOs and directly controlled by PMBus commands. The device can be controlled by up to 32 GPIO configured GPI pins. The GPIs can be used as fault inputs which can shut down rails. The GPIs can be also used as Boolean logic input to control the 16 Logic GPO outputs. Each of the 16 Logic GPO pins has a flexible Boolean logic builder. Input signals of the Boolean logic builder can include GPIs, other GPOs, and selectable system flags such as POWER\_GOOD, faults, warnings, and so forth. A simple state machine is also available for each Logic GPO pin.

The device provides additional features such as cascading, pin-selected states, system watchdog, system reset, run time clock, peak value log, reset counter, and so forth. Cascading feature offers convenient ways to cascade up to 4 UCD90320U devices and manage up to 128 voltage rails through one SYNC\_CLK pin connection. Pin-selected states feature allows users to define up to 8 rail states. These states can implement system low-power modes as set out in the *Advanced Configuration and Power Interface (ACPI)* specification. The *Feature Description* section of this datasheet describes other device features.

#### 8.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

#### 8.3 Feature Description

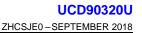

#### 8.3.1 TI Fusion Digital Power Designer software

The Texas Instruments Fusion Digital Power Designer software allows the user to configure the device. This PCbased graphic user interface (GUI) offers an intuitive I<sup>2</sup>C and PMBus interface to the device. The *Fusion Digital Power Designer* software allows the design engineer to configure the system operating parameters for the application without directly using PMBus commands, store the configuration to on-chip nonvolatile memory, and observe system status (voltage, current, temperature, faults, and so forth). This data sheet references the Fusion Digital Power Designer software is as *Fusion Digital Power Designer* software and many sections include screenshots. Download the *Fusion Digital Power Designer* software from TI here. After configuration, the device can perform all designed functions independently without further need for the Fusion GUI.

#### 8.3.2 PMBUS Interface

PMBus refers to a serial interface specifically designed to support power management. The PMBus interface is based on the SMBus interface that is built on the I<sup>2</sup>C physical specification. The UCD90320U device supports revision 1.2 of the PMBus standard. Wherever possible, standard PMBus interface commands support the function of the device. Unique features of the device are defined to configure or activate via the MFR\_SPECIFIC commands. These commands are defined in the, *UCD90320U Sequencer and System Health Controller PMBUS Command Reference*. The most current UCD90320U PMBus<sup>™</sup> Command Reference can be found within the TI Fusion Digital Power Designer software through the Help Menu (*Help, Documentation & Help Center, Sequencers tab, Documentation* section).

This data sheet makes frequent mention of the PMBus specification. Specifically, this document is *PMBus Power System Management Protocol Specification Part II – Command Language*, Revision 1.2, dated 6 September 2010. The specification is published by the Power Management Bus Implementers Forum and is available from www.pmbus.org.

The UCD90320U device meets all of the requirements of the *Compliance* section of the PMBus specification. The firmware complies with the SMBus 1.2 specification, including support for the SMBus ALERT function. The hardware supports either 100-kHz or 400-kHz PMBus operation.

#### 8.3.3 Rail Setup

Power rails are defined under the **Pin Assignment** tab, as shown in Figure 4. Click corresponding buttons to add or delete a rail. After a rail is added, AMON, DMON, EN, and MARGIN pins can be assigned to the rail. UCD90320U has 24 AMON pins, 8 DMON pins, 32 EN pins, and 24 MARGIN pins, thus can support up to 32 rails.

| Rails - Monitors & Enables |                                                       |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|----------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Rail Name                  | Voltage                                               | Temperature                                                                                                                                                             | Current                                                                                                                                                                                                                                                                                                                                                              | Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Trim/Margin PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |