📕 Order

Now

#### **DRV8889-Q1**

ZHCSJO5B-NOVEMBER 2019-REVISED JANUARY 2020

Support &

Community

22

# 具有集成电流感应、1/256 微步进和失速检测功能的 DRV8889-Q1 汽车步 进驱动器

Technical

Documents

🧷 Tools &

Software

- 1 特性

- 符合面向汽车应用的 AEC-Q100

- 最大 1/256 微步进 .

- 集成式电流感应功能 •

- 无需使用检测电阻器

- 智能调优衰减技术、 ٠ 固定缓慢和混合衰减选项

- 4.5V 至 45V 的工作电源电压范围

- 低 R<sub>DS(ON)</sub>: 900mΩ HS + LS (在 13.5V 和 25°C 条件下)

- 每个桥都具有高电流容量 - 2.4A 峰值、1.5A 满量程、1.1A rms

- TRQ DAC 位可调节满量程电流 •

- 可配置的关断时间 PWM 斩波

- 7µs、16µs、24µs 或 32µs。

- 简单的 STEP/DIR 接口

- 支持菊花链的 SPI

- 低电流睡眠模式 (2µA) .

- 可编程输出压摆率

- 扩频时钟可将 EMI 降至最低

- 保护 特性

- VM 欠压锁定

- 过流保护

- 失速检测

- 开路负载检测

- 过热警告和关断

- 欠温警告

- 故障条件指示引脚 (nFAULT)

## 2 应用

- 汽车双极步进电机 •

- 前照灯位置调节

- 抬头显示 (HUD)

- HVAC 步进电机 ٠

- 电子燃油喷射 (EFI) ٠

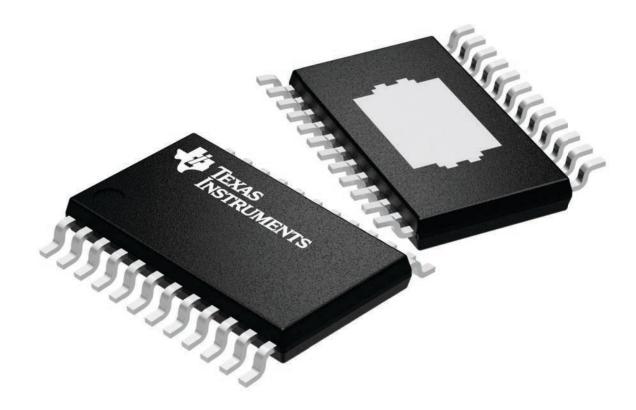

## 3 说明

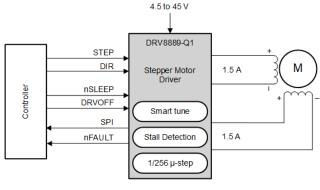

DRV8889-Q1 是一款完全集成的步进电机驱动器,可 支持高达 1.5A 的满量程电流, 配备内部微步进索引 器、智能调谐衰减技术、先进的失速检测算法和集成电 流感应功能。

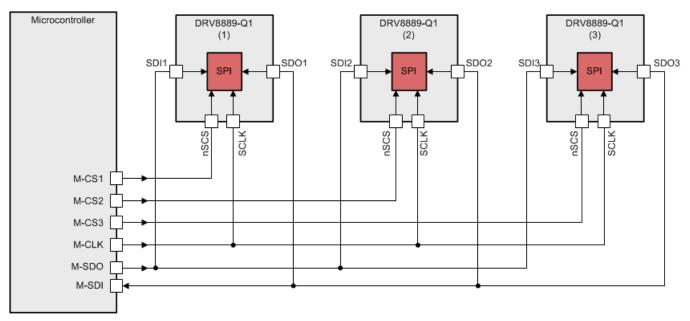

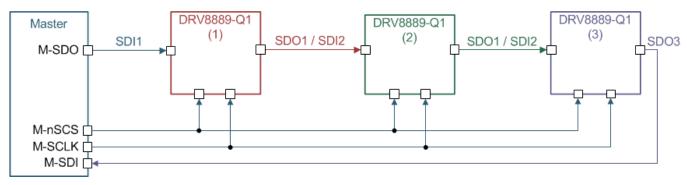

DRV8889-Q1 具有一个简单的步进/方向控制接口来管 理方向和步进速率,最多支持 1/256 级微步进,以实 现平滑的运动规划。集成电流感应功能消除了对两个外 部电阻的需求,从而节省了布板空间和成本。利用先进 的失速检测算法,设计人员可以检测电动机是否停止运 行,并根据需要采取措施,从而提高效率并降低噪声。 DRV8889-Q1 提供 8 种衰减模式选项,包括:智能调 优、慢速和混合衰减选项。智能调优技术可自动调节, 以实现出色的电流调节性能并对任何电机变化和老化效 应进行补偿。该器件还包括一个集成的扭矩 DAC,该 扭矩 DAC 允许控制器通过 SPI 调整输出电流,而无需 调整 VREF 电压基准。该器件采用 nSLEEP 引脚,可 提供一种低功耗的休眠模式,从而实现极低待机电流。 此器件 具有 全双工、4 线同步 SPI 通信功能,并允许 通过菊花链方式串联最多 63 个器件以实现可配置性和 提供详细故障报告。

在 ti.com 上查看我们完整的步进电机驱动器产品系列

#### 器件信息(1)

| 器件型号            | 封装                   | 封装尺寸(标称值)       |

|-----------------|----------------------|-----------------|

| DRV8889QPWPRQ1  | HTSSOP (24)          | 7.80mm × 4.40mm |

| DRV8889QWRGERQ1 | VQFN (24)(可<br>湿性侧面) | 4.00mm × 4.00mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

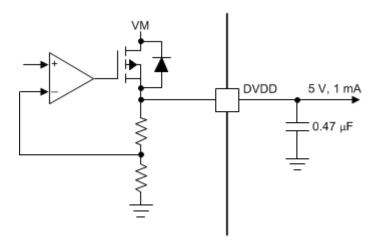

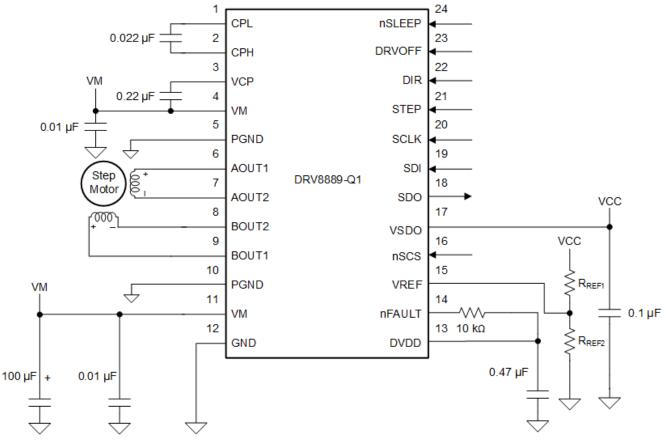

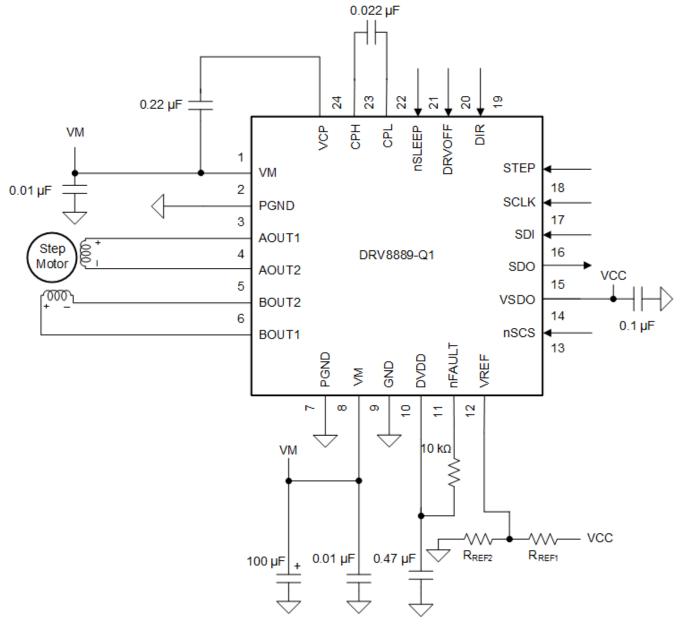

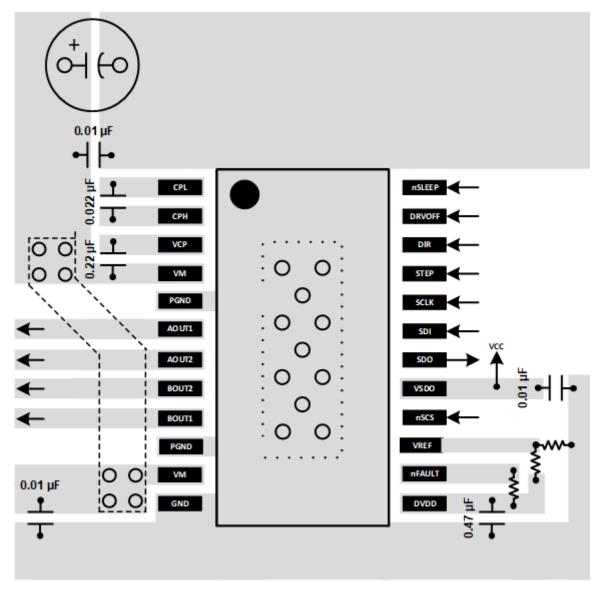

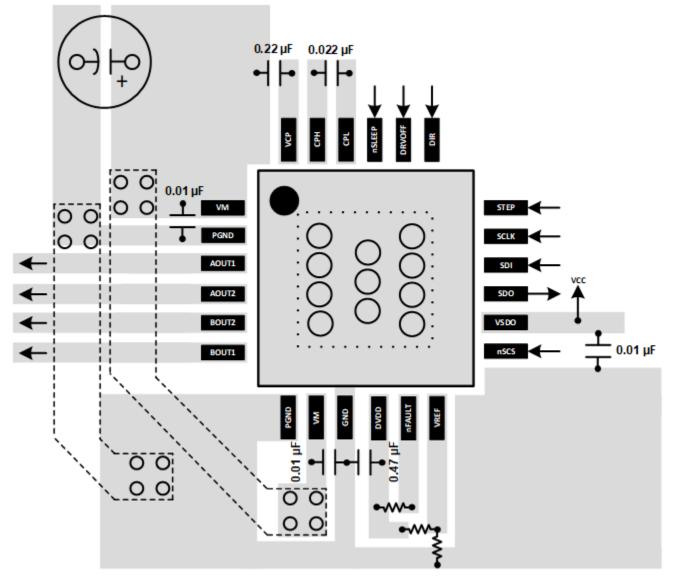

简化原理图

# 目录

7.6

11.2

8

9

| 1 | 特性   | 1                                |

|---|------|----------------------------------|

| 2 | 应用   | 1                                |

| 3 | 说明   | 1                                |

| 4 | 修订   | 历史记录 2                           |

| 5 | Pin  | Configuration and Functions 3    |

| 6 | Spe  | cifications5                     |

|   | 6.1  | Absolute Maximum Ratings 5       |

|   | 6.2  | ESD Ratings5                     |

|   | 6.3  | Recommended Operating Conditions |

|   | 6.4  | Thermal Information 6            |

|   | 6.5  | Electrical Characteristics7      |

|   | 6.6  | SPI Timing Requirements 9        |

|   | 6.7  | Indexer Timing Requirements 10   |

|   | 6.8  | Typical Characteristics 11       |

| 7 | Deta | ailed Description 13             |

|   | 7.1  | Overview 13                      |

|   | 7.2  | Functional Block Diagram 14      |

|   | 7.3  | Feature Description 15           |

|   | 7.4  | Device Functional Modes          |

# 4 修订历史记录

2

注: 之前版本的页码可能与当前版本有所不同。

| C | hanges from Revision A (December 2019) to Revision B                                 | Page |

|---|--------------------------------------------------------------------------------------|------|

| • | 已更改 R-C time constant for low-pass filter in <i>Controlling VREF with an MCU DAC</i> | 19   |

| • | 已添加 table to <i>Disable Mode (nSLEEP = 1, DRVOFF = 1)</i>                            | 37   |

| • | 已添加 new scope shot to <i>Application Curves</i>                                      | 54   |

| • | 已添加 data on thermal parameters in Thermal Parameters for HTSSOP Package              | 58   |

# Changes from Original (November 2019) to Revision A

| • 己更改 将器件状态更改为生产数据 | 1 |

|--------------------|---|

|--------------------|---|

Page

Register Maps..... 43

Application and Implementation ...... 51 8.1 Application Information..... 51

9.1 Bulk Capacitance ..... 63 10.1 Layout Guidelines ..... 64 10.2 Layout Example ..... 65 11 器件和文档支持 ...... 67 11.1 文档支持...... 67

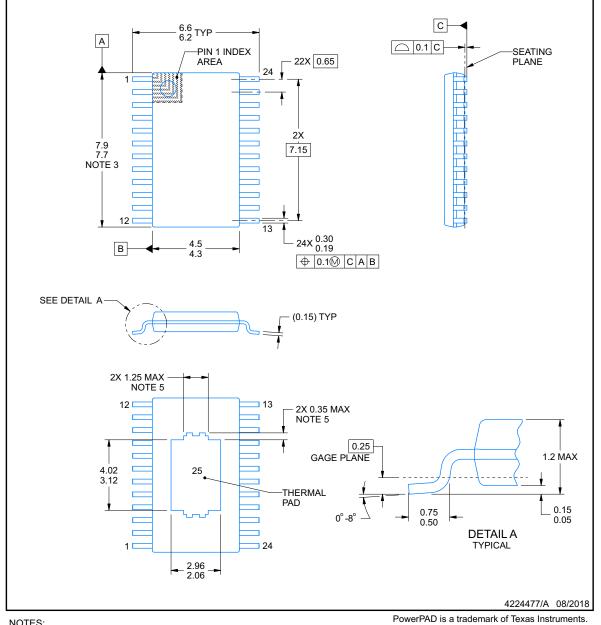

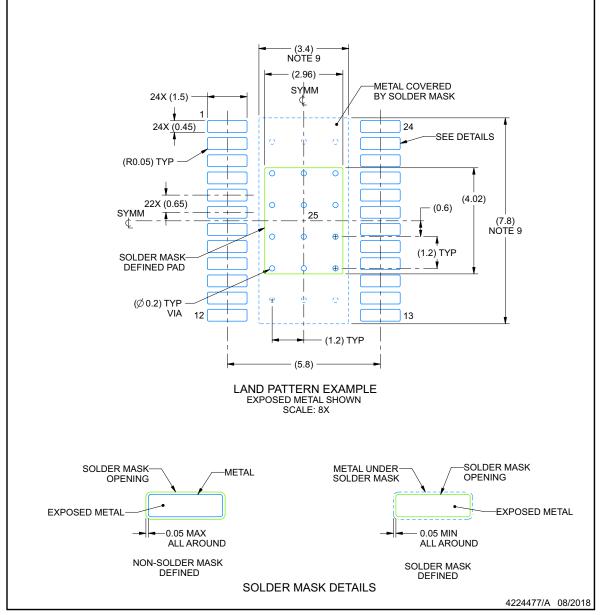

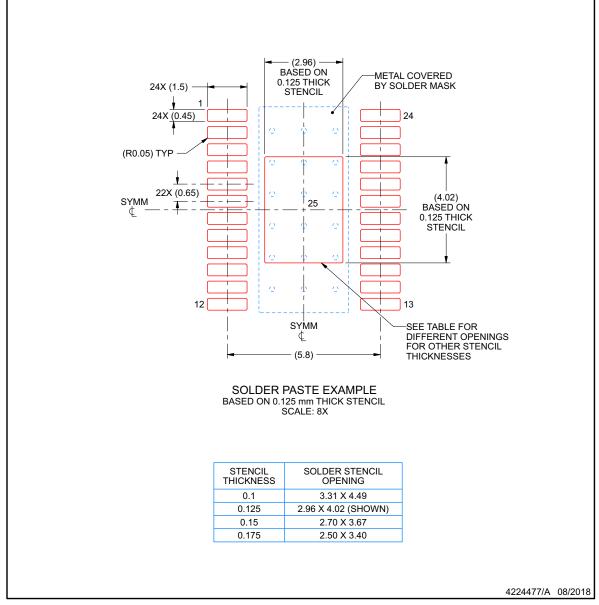

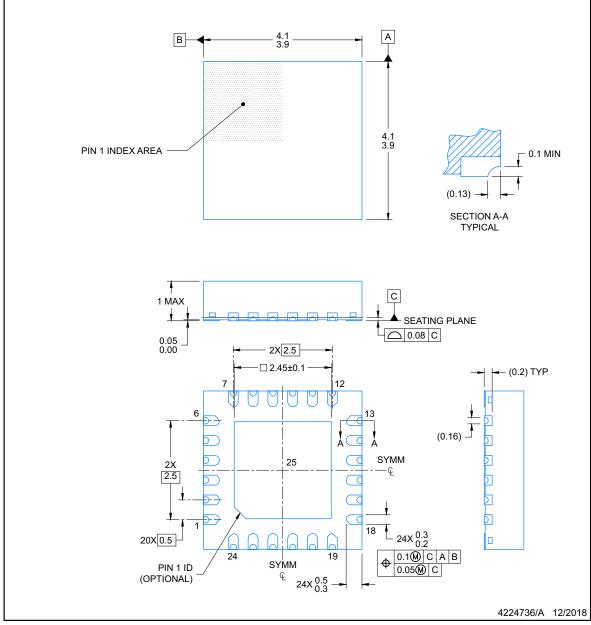

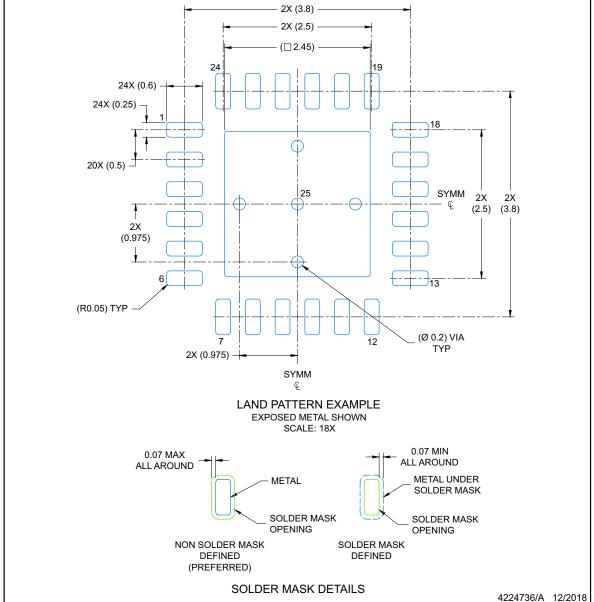

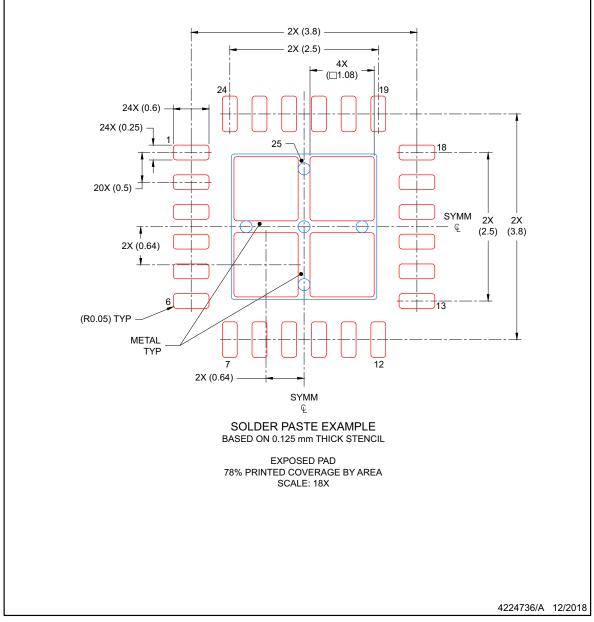

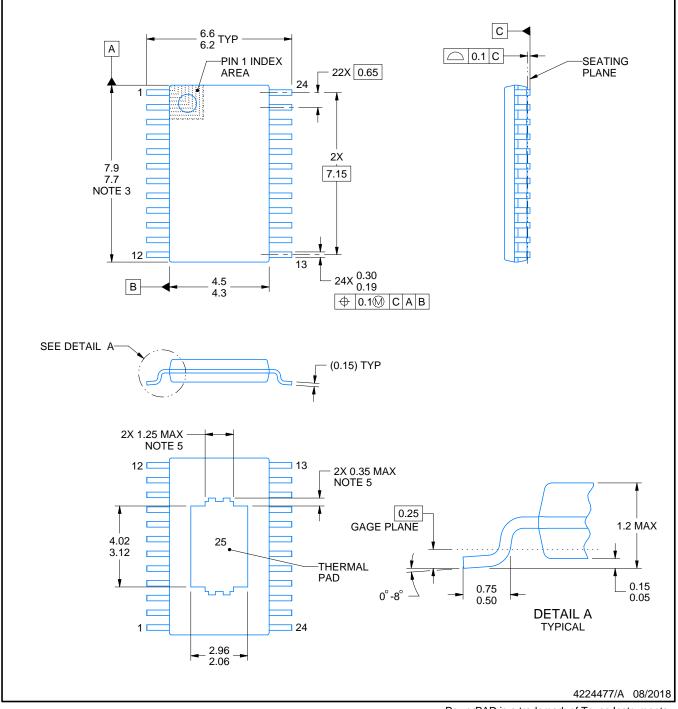

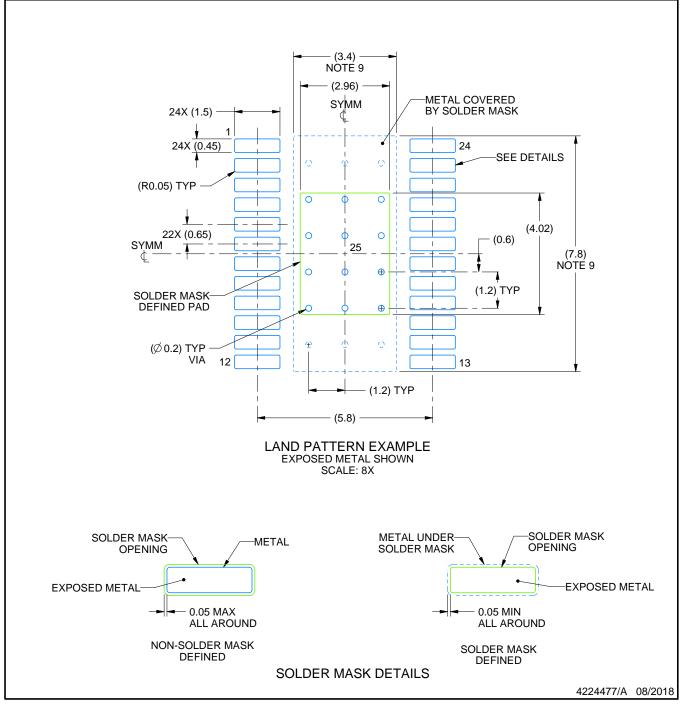

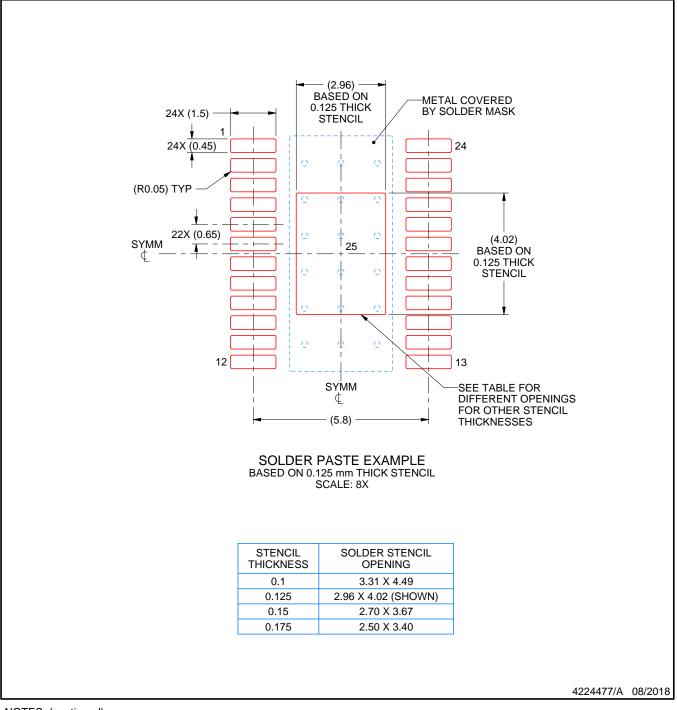

接收文档更新通知 ...... 67 11.5 静电放电警告...... 67 12 机械、封装和可订购信息...... 68

EXAS

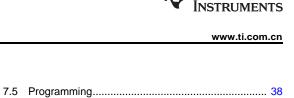

# 5 Pin Configuration and Functions

#### Pin Functions

| PIN    |        |      |     |           |                                                                                                                       |

|--------|--------|------|-----|-----------|-----------------------------------------------------------------------------------------------------------------------|

| NAME   | N      | 10.  | I/O | TYPE      | DESCRIPTION                                                                                                           |

|        | HTSSOP | VQFN |     |           |                                                                                                                       |

| AOUT1  | 6      | 3    | 0   | Output    | Winding A output. Connect to stepper motor winding.                                                                   |

| AOUT2  | 7      | 4    | 0   | Output    | Winding A output. Connect to stepper motor winding.                                                                   |

| PGND   | 5, 10  | 2, 7 | —   | Power     | Power ground. Both PGND pins are shorted internally. Connect to system ground on PCB.                                 |

| BOUT1  | 9      | 6    | 0   | Output    | Winding B output. Connect to stepper motor winding                                                                    |

| BOUT2  | 8      | 5    | 0   | Output    | Winding B output. Connect to stepper motor winding                                                                    |

| CPH    | 2      | 23   |     | Power     | Charge pump switching node. Connect a X7R, 0.022-µF, VM-rated ceramic                                                 |

| CPL    | 1      | 22   |     | Power     | capacitor from CPH to CPL.                                                                                            |

| DIR    | 22     | 19   | I   | Input     | Direction input. Logic level sets the direction of stepping; internal pulldown resistor.                              |

| DRVOFF | 23     | 20   | I   | Input     | Logic high to disable device outputs; logic low to enable; internal pullup to DVDD.                                   |

| DVDD   | 13     | 10   |     | Power     | Logic supply voltage. Connect a X7R, 0.47-µF, 6.3-V or 10-V rated ceramic capacitor to GND.                           |

| GND    | 12     | 9    | _   | Power     | Device ground. Connect to system ground.                                                                              |

| VREF   | 15     | 12   | I   | Input     | Current set reference input. Maximum value 3.3 V. DVDD can be used to provide VREF through a resistor divider.        |

| SCLK   | 20     | 17   | I   | Input     | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin. |

| SDI    | 19     | 16   | I   | Input     | Serial data input. Data is captured on the falling edge of the SCLK pin                                               |

| SDO    | 18     | 15   | 0   | Push Pull | Serial data output. Data is shifted out on the rising edge of the SCLK pin.                                           |

| STEP   | 21     | 18   | I   | Input     | Step input. A rising edge causes the indexer to advance one step; internal pulldown resistor.                         |

Copyright © 2019-2020, Texas Instruments Incorporated

DRV8889-Q1 ZHCSJO5B – NOVEMBER 2019 – REVISED JANUARY 2020

www.ti.com.cn

NSTRUMENTS

**Texas**

# Pin Functions (continued)

| PIN    |        |      |     |                                                                                                                     |                                                                                                                                                                     |

|--------|--------|------|-----|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | NO.    |      | I/O | TYPE                                                                                                                | DESCRIPTION                                                                                                                                                         |

| NAME   | HTSSOP | VQFN |     |                                                                                                                     |                                                                                                                                                                     |

| VCP    | 3      | 24   | _   | Power                                                                                                               | Charge pump output. Connect a X7R, 0.22- $\mu$ F, 16-V ceramic capacitor to VM.                                                                                     |

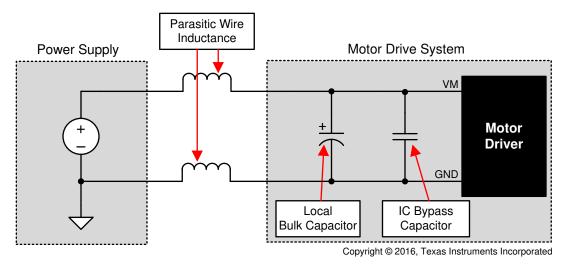

| VM     | 4, 11  | 1, 8 | _   | Power                                                                                                               | Power supply. Connect to motor supply voltage and bypass to GND with two $0.01$ - $\mu$ F ceramic capacitors (one for each pin) plus a bulk capacitor rated for VM. |

| VSDO   | 17     | 14   |     | Power                                                                                                               | Supply pin for SDO output. Connect to 5-V or 3.3-V depending on the desired logic level.                                                                            |

| nFAULT | 14     | 11   | 0   | Open<br>Drain                                                                                                       | Fault indication. Pulled logic low with fault condition; open-drain output requires an external pullup resistor.                                                    |

| nSCS   | 16     | 13   | I   | Input                                                                                                               | Serial chip select. An active low on this pin enables the serial interface communications. Internal pullup to DVDD.                                                 |

| nSLEEP | 24     | 21   | I   | Input Sleep mode input. Logic high to enable device; logic low to enter low sleep mode; internal pulldown resistor. |                                                                                                                                                                     |

| PAD    |        |      | -   | -                                                                                                                   | Thermal pad. Connect to system ground.                                                                                                                              |

#### DRV8889-Q1 ZHCSJO5B – NOVEMBER 2019 – REVISED JANUARY 2020

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                       | MIN      | MAX        | UNIT |

|-----------------------------------------------------------------------|----------|------------|------|

| Power supply voltage (VM)                                             | -0.3     | 50         | V    |

| Charge pump voltage (VCP, CPH)                                        | -0.3     | VM + 7     | V    |

| Charge pump negative switching pin (CPL)                              | -0.3     | VM         | V    |

| Charge pump negative switching pin (nSLEEP)                           | -0.3     | VM         | V    |

| Internal regulator voltage (DVDD)                                     | -0.3     | 5.75       | V    |

| SDO output reference voltage (VSDO)                                   | -0.3     | 5.75       | V    |

| Control pin voltage (STEP, DIR, DRVOFF, nFAULT, SDI, SDO, SCLK, nSCS) | -0.3     | 5.75       | V    |

| Open drain output current (nFAULT)                                    | 0        | 10         | mA   |

| Reference input pin voltage (VREF)                                    | -0.3     | 5.75       | V    |

| Continuous phase node pin voltage (AOUT1, AOUT2, BOUT1, BOUT2)        | -1.0     | VM + 1.0   | V    |

| Transient 100 ns phase node pin voltage (AOUT1, AOUT2, BOUT1, BOUT2)  | -3.0     | VM + 3.0   | V    |

| Peak drive current (AOUT1, AOUT2, BOUT1, BOUT2)                       | Internal | ly Limited | А    |

| Operating ambient temperature, T <sub>A</sub>                         | -40      | 125        | °C   |

| Operating junction temperature, T <sub>J</sub>                        | -40      | 150        | °C   |

| Storage temperature, T <sub>stg</sub>                                 | -65      | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|        |                         |                                                         |                                         | VALUE | UNIT |

|--------|-------------------------|---------------------------------------------------------|-----------------------------------------|-------|------|

| V(FOD) |                         | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                                         | ±2000 |      |

|        | Electrostatic discharge |                                                         | Corner pins for PWP (1, 12, 13, and 24) | ±750  | V    |

|        |                         |                                                         | Other pins                              | ±500  |      |

(1) AECQ100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001specification.

ZHCSJO5B-NOVEMBER 2019-REVISED JANUARY 2020

www.ti.com.cn

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                                | MIN  | MAX                | UNIT |

|-------------------|------------------------------------------------|------|--------------------|------|

| $V_{VM}$          | Supply voltage range for normal (DC) operation | 4.5  | 45                 | V    |

| VI                | Logic level input voltage                      | 0    | 5.5                | V    |

| V <sub>SDO</sub>  | SDO buffer supply voltage                      | 2.9  | 5.5                | V    |

| V <sub>VREF</sub> | VREF voltage                                   | 0.05 | 3.3                | V    |

| $f_{STEP}$        | Applied STEP signal (STEP)                     | 0    | 100 <sup>(1)</sup> | kHz  |

| I <sub>FS</sub>   | Motor full-scale current (xOUTx)               | 0    | 1.5 <sup>(2)</sup> | А    |

| I <sub>rms</sub>  | Motor RMS current (xOUTx)                      | 0    | 1.1 <sup>(2)</sup> | А    |

| T <sub>A</sub>    | Operating ambient temperature                  | -40  | 125                | °C   |

| TJ                | Operating junction temperature                 | -40  | 150                | °C   |

STEP input can operate up to 500 kHz, but system bandwidth is limited by the motor load Power dissipation and thermal limits must be observed (1)

(2)

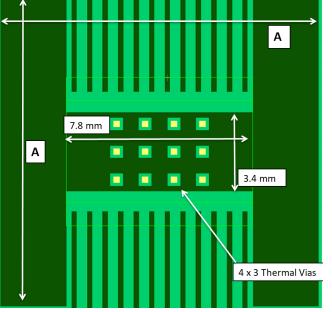

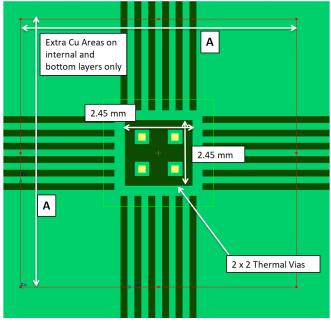

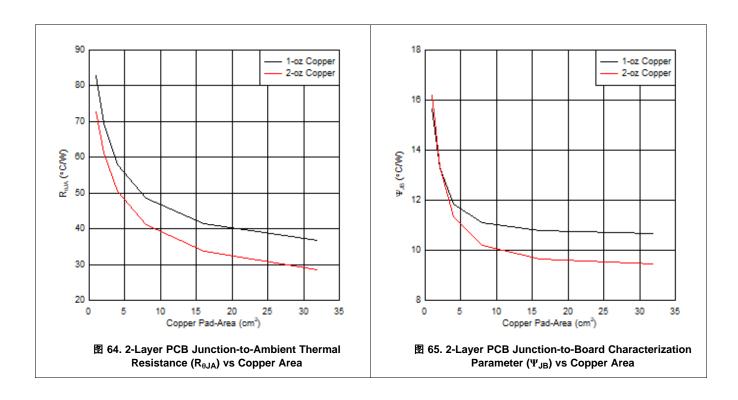

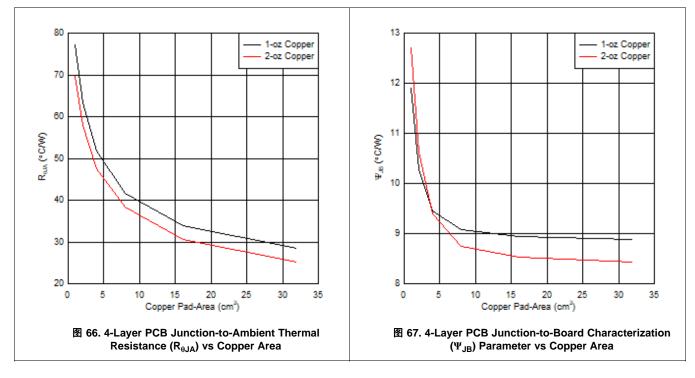

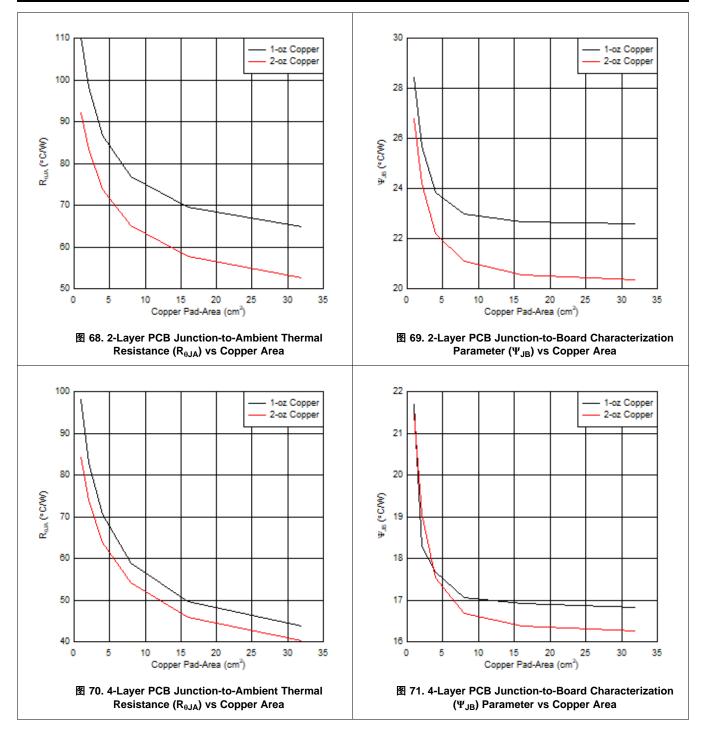

#### 6.4 Thermal Information

|                       |                                              | DRV888       |            |      |

|-----------------------|----------------------------------------------|--------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | RGE (VQFN) | UNIT |

|                       |                                              | 24 PINS      | 24 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 30.9         | 40.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 25.2         | 31.1       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 11.3         | 17.9       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.4          | 0.6        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 11.3         | 17.8       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.1          | 4.3        | °C/W |

(1) For more information about traditional and new thermalmetrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 6.5 Electrical Characteristics

|                     | PARAMETER                          | TEST CONDITIONS                          | MIN | TYP    | MAX | UNIT |

|---------------------|------------------------------------|------------------------------------------|-----|--------|-----|------|

| POWER S             | UPPLIES (VM, DVDD, VSDO)           | · · · · · ·                              |     |        | I   |      |

| I <sub>VM</sub>     | VM operating supply current        | DRVOFF = 0, nSLEEP = 1, No output        |     | 5      | 7   | mA   |

| I <sub>VMQ</sub>    | VM sleep mode supply current       | nSLEEP = 0                               |     | 2      | 4   | μA   |

| t <sub>SLEEP</sub>  | Sleep time                         | nSLEEP = 0 to sleep-mode                 | 75  |        |     | μs   |

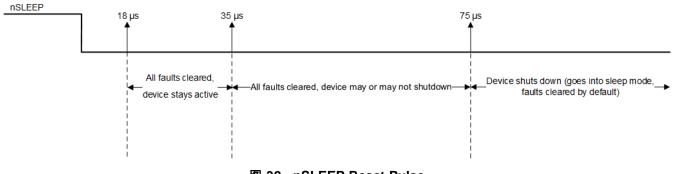

| t <sub>RESET</sub>  | nSLEEP reset pulse                 | nSLEEP low to only clear fault registers | 18  |        | 35  | μS   |

| t <sub>WAKE</sub>   | Wake-up time                       | nSLEEP = 1 to output transition          |     | 0.6    | 0.9 | ms   |

| t <sub>ON</sub>     | Turn-on time                       | VM > UVLO to output transition           |     | 0.6    | 0.9 | ms   |

| V <sub>DVDD</sub>   | Internal regulator voltage         | No external load, 6 V < $V_{VM}$ < 45 V  | 4.5 | 5      | 5.5 | V    |

| CHARGE I            | PUMP (VCP, CPH, CPL)               |                                          |     |        |     |      |

| V <sub>VCP</sub>    | VCP operating voltage              |                                          |     | VM + 5 |     | V    |

| f <sub>(VCP)</sub>  | Charge pump switching<br>frequency | V <sub>VM</sub> > UVLO; nSLEEP = 1       |     | 400    |     | kHz  |

| LOGIC-LE            | VEL INPUTS (STEP, DIR, nSLEEI      | P, nSCS, SCLK, SDI, DRVOFF)              |     |        |     |      |

| V <sub>IL</sub>     | Input logic-low voltage            |                                          | 0   |        | 0.6 | V    |

| V <sub>IH</sub>     | Input logic-high voltage           |                                          | 1.5 |        | 5.5 | V    |

| V <sub>HYS</sub>    | Input logic hysteresis             |                                          |     | 150    |     | mV   |

| I <sub>IL1</sub>    | Input logic-low current            | VIN = 0 V (nSCS, DRVOFF)                 | 8   |        | 12  | μA   |

| I <sub>IL2</sub>    | Input logic-low current            | VIN = 0 V                                | -1  |        | 1   | μA   |

| I <sub>IH1</sub>    | Input logic-high current           | VIN = DVDD (nSCS, DRVOFF)                |     |        | 500 | nA   |

| I <sub>IH2</sub>    | Input logic-high current           | VIN = 5 V                                |     |        | 50  | μA   |

| PUSH-PUL            | L OUTPUT (SDO)                     |                                          |     |        |     |      |

| R <sub>PD,SDO</sub> | Internal pull-down resistance      | 5mA load, with respect to GND            |     | 40     | 75  | Ω    |

| R <sub>PU,SDO</sub> | Internal pull-up resistance        | 5mA load, with respect to VSDO           |     | 30     | 60  | Ω    |

| I <sub>SDO</sub>    | SDO Leakage Current                | SDO = VSDO and 0V                        | -1  |        | 1   | μA   |

| CONTROL             | OUTPUTS (nFAULT)                   |                                          |     |        |     |      |

| V <sub>OL</sub>     | Output logic-low voltage           | I <sub>O</sub> = 5 mA                    |     |        | 0.4 | V    |

| I <sub>OH</sub>     | Output logic-high leakage          | V <sub>VM</sub> = 13.5 V                 | -1  |        | 1   | μA   |

ZHCSJO5B-NOVEMBER 2019-REVISED JANUARY 2020

www.ti.com.cn

INSTRUMENTS

Texas

# **Electrical Characteristics (continued)**

| Over recommended operating conditions unless otherwise noted | . Typical limits apply for $T_J = 25^{\circ}C$ and $V_{VM} = 13.5 \text{ V}$ |

|--------------------------------------------------------------|------------------------------------------------------------------------------|

|--------------------------------------------------------------|------------------------------------------------------------------------------|

|                       | PARAMETER                             | TEST CONDITIONS                                            | MIN  | TYP    | MAX  | UNIT |  |

|-----------------------|---------------------------------------|------------------------------------------------------------|------|--------|------|------|--|

|                       | RIVER OUTPUTS (AOUT1, AOUT            | r2, BOUT1, BOUT2)                                          | I    |        |      |      |  |

|                       |                                       | VM = 13.5 V, T <sub>J</sub> = 25°C, I <sub>O</sub> = -1 A  |      | 450    | 550  | mΩ   |  |

| R <sub>DS(ONH)</sub>  | High-side FET on resistance           | VM = 13.5 V, T <sub>J</sub> = 125°C, I <sub>O</sub> = -1 A |      | 700    | 850  | mΩ   |  |

|                       |                                       | VM = 13.5 V, T <sub>J</sub> = 150°C, I <sub>O</sub> = -1 A |      | 780    | 950  | mΩ   |  |

|                       |                                       | VM = 13.5 V, T <sub>J</sub> = 25°C, I <sub>O</sub> = 1 A   |      | 450    | 550  | mΩ   |  |

| R <sub>DS(ONL)</sub>  | Low-side FET on resistance            | VM = 13.5 V, T <sub>J</sub> = 125°C, I <sub>O</sub> = 1 A  |      | 700    | 850  | mΩ   |  |

| -(- )                 |                                       | VM = 13.5 V, T <sub>J</sub> = 150°C, I <sub>O</sub> = 1 A  |      | 780    | 950  | mΩ   |  |

|                       |                                       | SR = 00b, VM = 13.5 V, I <sub>O</sub> = 0.5 A              |      | 10     |      |      |  |

|                       |                                       | SR = 01b, VM = 13.5 V, I <sub>O</sub> = 0.5 A              |      | 35     |      |      |  |

| t <sub>SR</sub>       | Output slew rate                      | SR = 10b, VM = 13.5 V, I <sub>O</sub> = 0.5 A              |      | 50     |      | V/µs |  |

|                       |                                       | SR = 11b, VM = 13.5 V, I <sub>O</sub> = 0.5 A              |      | 105    |      |      |  |

|                       | RENT CONTROL (VREF)                   |                                                            | 1    |        |      |      |  |

| K <sub>V</sub>        | Transimpedance gain                   |                                                            |      | 2.2    |      | V/A  |  |

|                       | · •                                   | TOFF = 00b                                                 |      | 7      |      |      |  |

|                       |                                       | TOFF = 01b                                                 |      | 16     |      | μs   |  |

| t <sub>OFF</sub>      | PWM off-time                          | TOFF = 10b                                                 |      | 24     |      |      |  |

|                       |                                       | TOFF = 11b                                                 |      | 32     |      |      |  |

|                       |                                       | I <sub>O</sub> = 1.5 A, 10% to 20% current setting         | -13  |        | 10   |      |  |

| $\Delta I_{TRIP}$     | Current trip accuracy                 | I <sub>O</sub> = 1.5 A, 20% to 67% current setting         | -8   |        | 8    | %    |  |

|                       |                                       | $I_{O} = 1.5$ A, 67% to 100% current setting               | -7.5 |        | 7.5  | Ī    |  |

| I <sub>O,CH</sub>     | AOUT and BOUT current matching        | I <sub>O</sub> = 1.5 A                                     | -2.5 |        | 2.5  | %    |  |

| PROTECTI              | ON CIRCUITS                           |                                                            | l    |        |      |      |  |

|                       |                                       | VM falling, UVLO falling                                   | 4.15 | 4.25   | 4.35 |      |  |

| V <sub>UVLO</sub>     | VM UVLO lockout                       | VM rising, UVLO rising                                     | 4.25 | 4.35   | 4.45 | V    |  |

| V <sub>UVLO,HYS</sub> | Undervoltage hysteresis               | Rising to falling threshold                                |      | 100    |      | mV   |  |

| V <sub>RST</sub>      | VM UVLO reset                         | VM falling, device reset, no SPI communications            |      |        | 3.9  | V    |  |

| V <sub>CPUV</sub>     | Charge pump undervoltage              | VCP falling; CPUV report                                   |      | VM + 2 |      | V    |  |

| I <sub>OCP</sub>      | Overcurrent protection                | Current through any FET                                    | 2.4  |        |      | А    |  |

|                       |                                       | V <sub>VM</sub> < 37 V                                     |      | 3      |      |      |  |

| t <sub>OCP</sub>      | Overcurrent deglitch time             | V <sub>VM</sub> ≥ 37 V                                     |      | 0.5    |      | μS   |  |

| t <sub>RETRY</sub>    | Overcurrent retry time                | OCP_MODE = 1b                                              |      | 4      |      | ms   |  |

| t <sub>OL</sub>       | Open load detection time              | EN_OL = 1b                                                 |      |        | 200  | ms   |  |

| I <sub>OL</sub>       | Open load current threshold           |                                                            |      | 30     |      | mA   |  |

| T <sub>OTW</sub>      | Overtemperature warning               | Die temperature T <sub>.1</sub>                            | 135  | 150    | 165  | °C   |  |

| T <sub>UTW</sub>      | Undertemperature warning              | Die temperature T <sub>.1</sub>                            | -25  | -10    | 5    | °C   |  |

| T <sub>OTSD</sub>     | Thermal shutdown                      | Die temperature $T_1$                                      | 150  | 165    | 180  | °C   |  |

| T <sub>HYS_OTSD</sub> | Thermal shutdown hysteresis           | Die temperature $T_J$                                      |      | 20     |      | °C   |  |

| T <sub>HYS_OTW</sub>  | Overtemperature warning<br>hysteresis | Die temperature T <sub>J</sub>                             |      | 20     |      | °C   |  |

| T <sub>HYS_UTW</sub>  | Undertemperature warning hysteresis   | Die temperature T <sub>J</sub>                             |      | 10     |      | °C   |  |

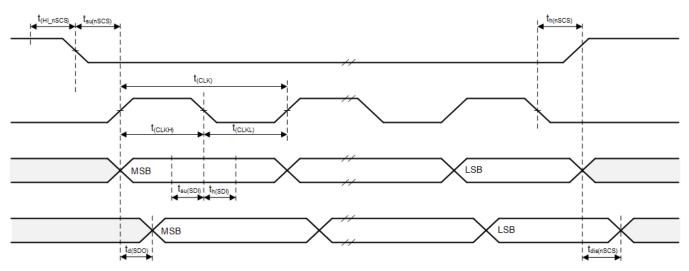

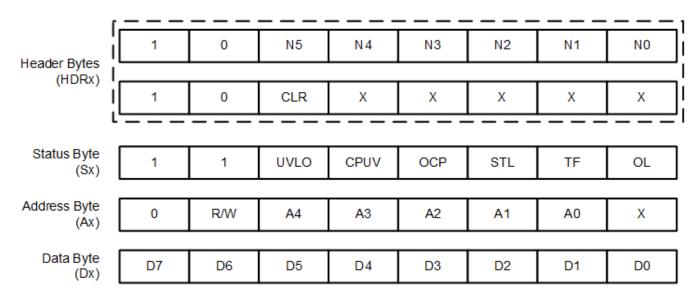

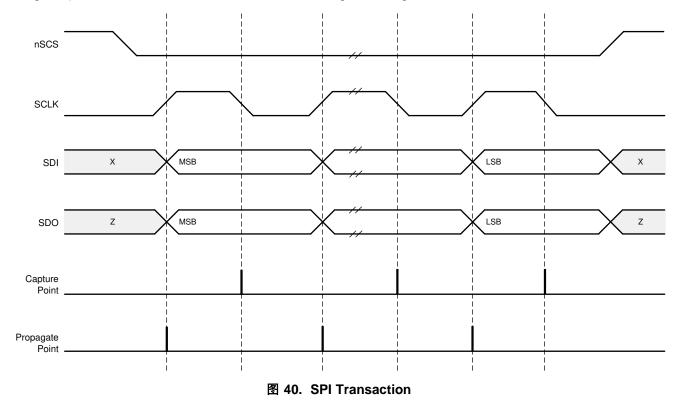

# 6.6 SPI Timing Requirements

|                        |                                                                      | MIN | NOM | MAX | UNIT |

|------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>(READY)</sub>   | SPI ready, VM > V <sub>RST</sub>                                     |     | 1   |     | ms   |

| t <sub>(CLK)</sub>     | SCLK minimum period                                                  | 100 |     |     | ns   |

| t <sub>(CLKH)</sub>    | SCLK minimum high time                                               | 50  |     |     | ns   |

| t <sub>(CLKL)</sub>    | SCLK minimum low time                                                | 50  |     |     | ns   |

| t <sub>su(SDI)</sub>   | SDI input setup time                                                 | 20  |     |     | ns   |

| t <sub>h(SDI)</sub>    | SDI input hold time                                                  | 30  |     |     | ns   |

| t <sub>d(SDO)</sub>    | SDO output delay time, SCLK high to SDO valid, $C_L = 20 \text{ pF}$ |     |     | 30  | ns   |

| t <sub>su(nSCS)</sub>  | nSCS input setup time                                                | 50  |     |     | ns   |

| t <sub>h(nSCS)</sub>   | nSCS input hold time                                                 | 50  |     |     | ns   |

| t <sub>(HI_nSCS)</sub> | nSCS minimum high time before active low                             |     |     | 2   | μs   |

| t <sub>dis(nSCS)</sub> | nSCS disable time, nSCS high to SDO high impedance                   |     | 10  |     | ns   |

ZHCSJO5B-NOVEMBER 2019-REVISED JANUARY 2020

www.ti.com.cn

**ISTRUMENTS**

**EXAS**

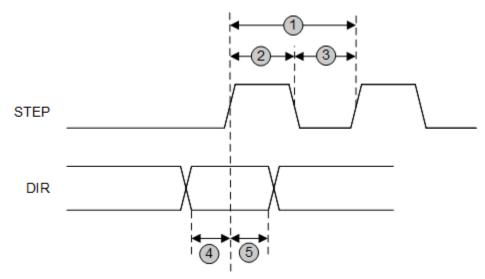

# 6.7 Indexer Timing Requirements

| Over recommended operating conditions unless otherwise noted | . Typical limits apply for $T_J = 25^{\circ}C$ and $V_{VM} = 13.5 \text{ V}$ |

|--------------------------------------------------------------|------------------------------------------------------------------------------|

|--------------------------------------------------------------|------------------------------------------------------------------------------|

| NO. |                          |                                | MIN | MAX                | UNIT |

|-----|--------------------------|--------------------------------|-----|--------------------|------|

| 1   | f <sub>step</sub>        | Step frequency                 |     | 500 <sup>(1)</sup> | kHz  |

| 2   | t <sub>WH(STEP)</sub>    | Pulse duration, STEP high      | 970 |                    | ns   |

| 3   | t <sub>WL(STEP)</sub>    | Pulse duration, STEP low       | 970 |                    | ns   |

| 4   | t <sub>SU(DIR, Mx)</sub> | Setup time, DIR to STEP rising | 200 |                    | ns   |

| 5   | t <sub>H(DIR, Mx)</sub>  | Hold time, DIR to STEP rising  | 200 |                    | ns   |

(1) STEP input can operate up to 500 kHz, but system bandwidth islimited by the motor load.

图 1. STEP and DIR Timing Diagram

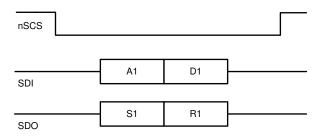

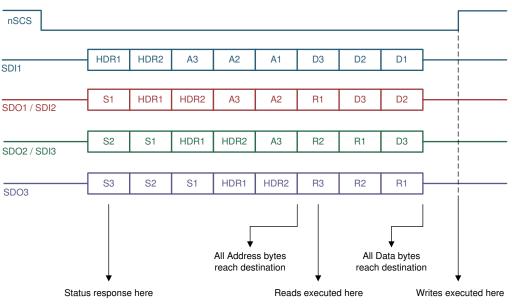

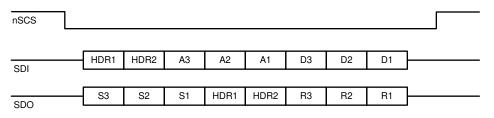

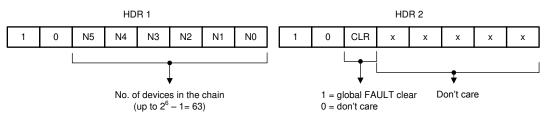

| 冬 | 2. | SPI | Slave-Mode | Timing | Definition |

|---|----|-----|------------|--------|------------|

|---|----|-----|------------|--------|------------|

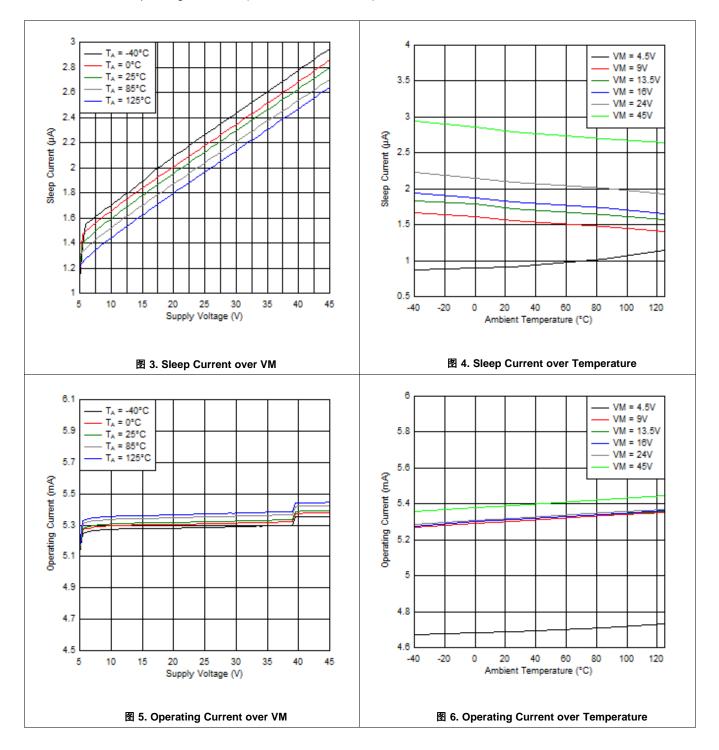

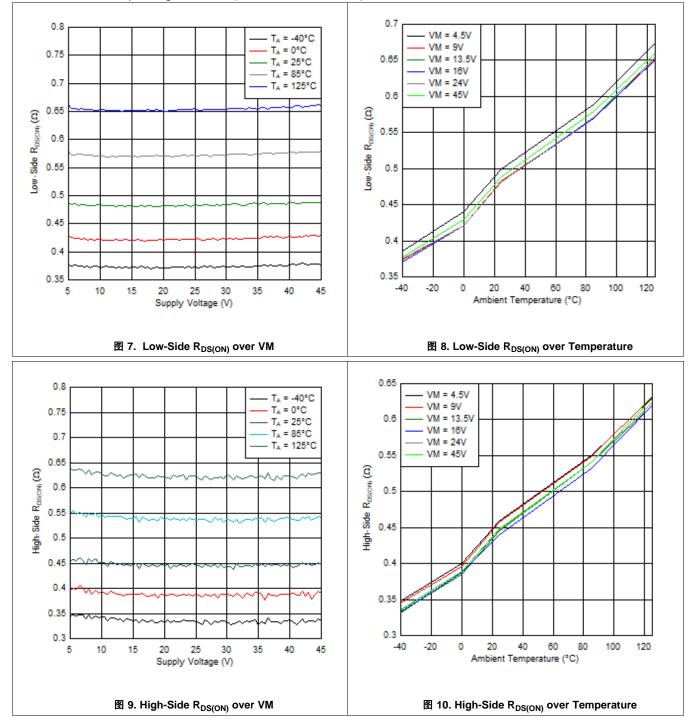

## 6.8 Typical Characteristics

Over recommended operating conditions (unless otherwise noted)

ZHCSJO5B-NOVEMBER 2019-REVISED JANUARY 2020

# Typical Characteristics (接下页)

Over recommended operating conditions (unless otherwise noted)

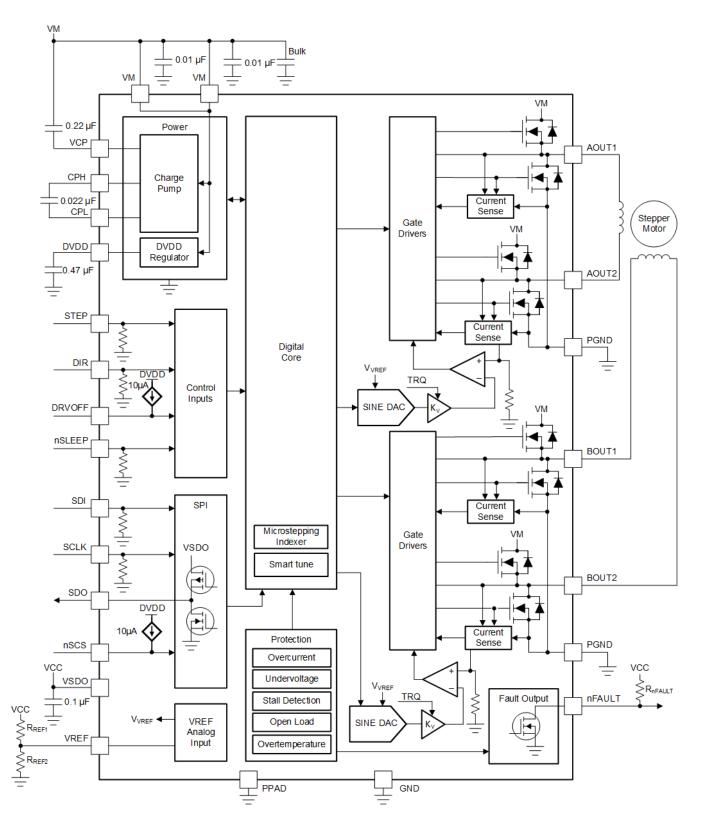

## 7 Detailed Description

## 7.1 Overview

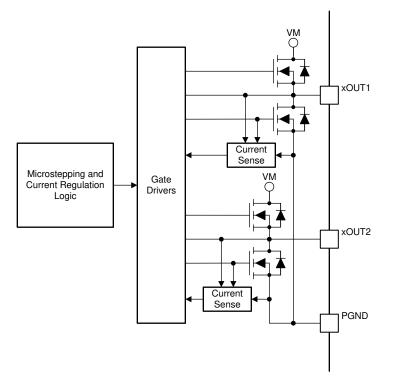

The DRV8889-Q1 device is an integrated motor-driver solution for bipolar stepper motors. The device integrates two N-channel power MOSFET H-bridges, integrated current sense and regulation circuitry, and a microstepping indexer. The DRV8889-Q1 device can be powered with a supply voltage from 4.5 to 45 V and is capable of providing an output current up to 2.4-A peak, 1.5-A full-scale, or 1.1-A root mean square (rms). The actual full-scale and rms current depends on the ambient temperature, supply voltage, and PCB thermal capability.

The device uses an integrated current-sense architecture which eliminates the need for two external power sense resistors. This architecture removes the power dissipated in the sense resistors by using a current mirror approach and using the internal power MOSFETs for current sensing. The current regulation set point is adjusted by the voltage at the VREF pin. These features reduces external component cost, board PCB size, and system power consumption.

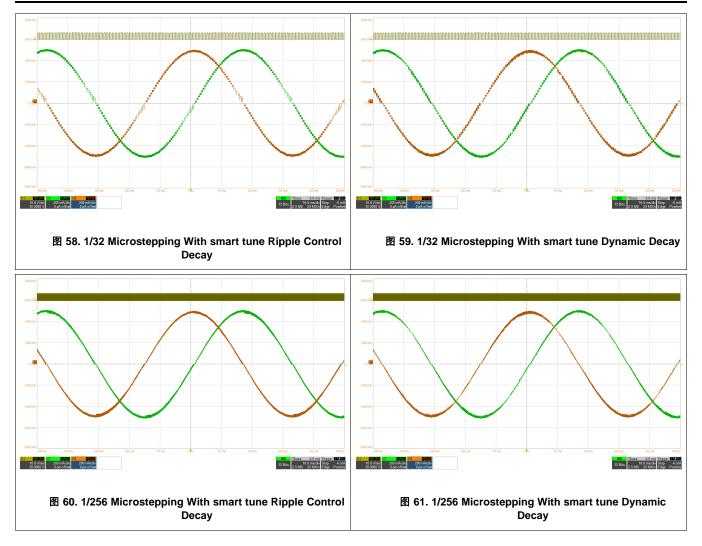

A simple STEP/DIR interface allows for an external controller to manage the direction and step rate of the stepper motor. The internal indexer can execute high-accuracy microstepping without requiring the external controller to manage the winding current level. The indexer is capable of full step, half step, and 1/4, 1/8, 1/16, 1/32, 1/64, 1/128 and 1/256 microstepping. In addition to a standard half stepping mode, a noncircular half stepping mode is available for increased torque output at higher motor RPM.

The current regulation is configurable between several decay modes. The decay mode can be selected as a slow-mixed, mixed decay, smart tune Ripple Control, or smart tune Dynamic Decay current regulation scheme. The slow-mixed decay mode uses slow decay on increasing steps and mixed decay on decreasing steps. The smart tune decay modes automatically adjust for optimal current regulation performance and compensate for motor variation and aging effects. Smart tune Ripple Control uses a variable off-time, ripple control scheme to minimize distortion of the motor winding current. Smart tune Dynamic Decay uses a fixed off-time, dynamic decay percentage scheme to minimize distortion of the motor winding current. In smart tune Ripple Control mode, the device can detect a motor overload stall condition or an end-of-line travel, by detecting back-emf phase shift between rising and falling current quadrants of the motor current.

The device integrates a spread spectrum clocking feature for both the internal digital oscillator and internal charge pump. This feature combined with output slew rate control minimizes the radiated emissions from the device.

A torque DAC feature allows the controller to scale the output current without needing to scale the VREF voltage reference. The torque DAC is accessed using a digital input pin which allows the controller to save system power by decreasing the motor current consumption when high output torque is not required.

A low-power sleep mode is included which allows the system to save power when not actively driving the motor.

# 7.2 Functional Block Diagram

## 7.3 Feature Description

表 1 lists the recommended external components for the DRV8889-Q1 device.

| COMPONENT                    | PIN 1              | PIN 2  | RECOMMENDED                                                                     |  |

|------------------------------|--------------------|--------|---------------------------------------------------------------------------------|--|

| C <sub>VM1</sub>             | VM                 | GND    | Two X7R, 0.01-µF, VM-rated ceramic capacitors                                   |  |

| C <sub>VM2</sub>             | VM                 | GND    | Bulk, VM-rated capacitor                                                        |  |

| C <sub>VCP</sub>             | VCP                | VM     | X7R, 0.22-µF, 16-V ceramic capacitor                                            |  |

| C <sub>SW</sub>              | CPH                | CPL    | X7R, 0.022-µF, VM-rated ceramic capacitor                                       |  |

| C <sub>DVDD</sub>            | DVDD               | GND    | X7R, 0.47-µF to 1-µF, 6.3-V ceramic capacitor                                   |  |

| R <sub>nFAULT</sub>          | VCC <sup>(1)</sup> | nFAULT | >4.7-kΩ resistor                                                                |  |

| R <sub>REF1</sub>            | VREF               | VCC    | Resistor to limit chopping current. It is recommended that the value of paralle |  |

| R <sub>REF2</sub> (Optional) | VREF               | GND    | combination of $R_{REF1}$ and $R_{REF2}$ should be less than 50-k $\Omega$ .    |  |

#### 表 1. DRV8889-Q1 External Components

(1) VCC is not a pin on the DRV8889-Q1 device, but a VCC supply voltage pullup is required for open-drain output nFAULT; nFAULT may be pulled up to DVDD

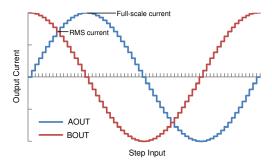

#### 7.3.1 Stepper Motor Driver Current Ratings

Stepper motor drivers can be classified using three different numbers to describe the output current: peak, rms, and full-scale.

#### 7.3.1.1 Peak Current Rating

The peak current in a stepper driver is limited by the overcurrent protection trip threshold  $I_{OCP}$ . The peak current describes any transient duration current pulse, for example when charging capacitance, when the overall duty cycle is very low. In general the minimum value of  $I_{OCP}$  specifies the peak current rating of the stepper motor driver.

For the DRV8889-Q1 device, the peak current rating is 2.4 A per bridge.

#### 7.3.1.2 rms Current Rating

The rms (average) current is determined by the thermal considerations of the IC. The rms current is calculated based on the  $R_{DS(ON)}$ , rise and fall time, PWM frequency, device quiescent current, and package thermal performance in a typical system at 25°C. The actual operating rms current may be higher or lower depending on heatsinking and ambient temperature.

For the DRV8889-Q1 device, the rms current rating is 1.1 A per bridge.

#### 7.3.1.3 Full-Scale Current Rating

The full-scale current describes the top of the sinusoid current waveform while microstepping. Because the sinusoid amplitude is related to the rms current, the full-scale current is also determined by the thermal considerations of the device. The full-scale current rating is approximately  $\sqrt{2} \times I_{RMS}$ .

For the DRV8889-Q1 device, the full-scale current rating is 1.5 A per bridge.

图 11. Full-Scale and RMS Current

DRV8889-Q1 ZHCSJO5B – NOVEMBER 2019 – REVISED JANUARY 2020

#### 7.3.2 PWM Motor Drivers

The device has drivers for two full H-bridges to drive the two windings of a bipolar stepper motor. 🛚 12 shows a block diagram of the circuitry.

图 12. PWM Motor Driver Block Diagram

#### 7.3.3 Microstepping Indexer

Built-in indexer logic in the device allows a number of different step modes. The MICROSTEP\_MODE bits in the SPI register are used to configure the step mode as shown in 表 2.

| At 2. Microscepping Settings |                                                  |  |  |  |  |

|------------------------------|--------------------------------------------------|--|--|--|--|

| MICROSTEP_MODE               | STEP MODE                                        |  |  |  |  |

| 0000b                        | Full step (2-phase excitation) with 100% current |  |  |  |  |

| 0001b                        | Full step (2-phase excitation) with 71% current  |  |  |  |  |

| 0010b                        | Non-circular 1/2 step                            |  |  |  |  |

| 0011b                        | 1/2 step                                         |  |  |  |  |

| 0100b                        | 1/4 step                                         |  |  |  |  |

| 0101b                        | 1/8 step                                         |  |  |  |  |

| 0110b                        | 1/16 step                                        |  |  |  |  |

| 0111b                        | 1/32 step                                        |  |  |  |  |

| 1000b                        | 1/64 step                                        |  |  |  |  |

| 1001b                        | 1/128 step                                       |  |  |  |  |

| 1010b                        | 1/256 step                                       |  |  |  |  |

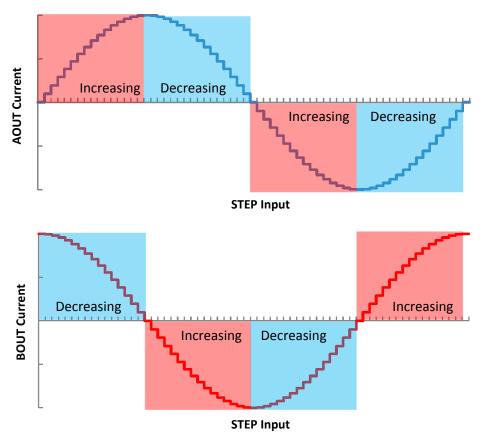

表 3 shows the relative current and step directions for full-step (71% current), 1/2 step, 1/4 step and 1/8 step operation. Higher microstepping resolutions follow the same pattern. The AOUT current is the sine of the electrical angle and the BOUT current is the cosine of the electrical angle. Positive current is defined as current flowing from the xOUT1 pin to the xOUT2 pin while driving.

At each rising edge of the STEP input the indexer travels to the next state in the table. The direction is shown with the DIR pin logic high. If the DIR pin is logic low, the sequence is reversed.

注 If the step mode is changed on the fly while stepping, the indexer advances to the next valid state for the new step mode setting at the rising edge of STEP.

注

While DIR = 0 and the electrical angle is at a full step angle (45, 135, 225, or 315 degrees), two rising edge pulses on the STEP pin are required in order to advance the indexer after changing from any microstep mode to the full step mode. The first pulse will induce no change in the electrical angle, the second pulse will move the indexer to the next full step angle.

The home state is an electrical angle of 45°. This state is entered after power-up, after exiting logic undervoltage lockout, or after exiting sleep mode.

| 1/8 STEP | 1/4 STEP | 1/2 STEP | FULL<br>STEP<br>71% | AOUT CURRENT<br>(% FULL-SCALE) | BOUT CURRENT<br>(% FULL-SCALE) | ELECTRICAL<br>ANGLE (DEGREES) |

|----------|----------|----------|---------------------|--------------------------------|--------------------------------|-------------------------------|

| 1        | 1        | 1        |                     | 0                              | 100                            | 0                             |

| 2        |          |          |                     | 20                             | 98                             | 11                            |

| 3        | 2        |          |                     | 38                             | 92                             | 23                            |

| 4        |          |          |                     | 56                             | 83                             | 34                            |

| 5        | 3        | 2        | 1                   | 71                             | 71                             | 45                            |

| 6        |          |          |                     | 83                             | 56                             | 56                            |

| 7        | 4        |          |                     | 92                             | 38                             | 68                            |

| 8        |          |          |                     | 98                             | 20                             | 79                            |

| 9        | 5        | 3        |                     | 100                            | 0                              | 90                            |

| 10       |          |          |                     | 98                             | -20                            | 101                           |

| 11       | 6        |          |                     | 92                             | -38                            | 113                           |

| 12       |          |          |                     | 83                             | -56                            | 124                           |

| 13       | 7        | 4        | 2                   | 71                             | -71                            | 135                           |

| 14       |          |          |                     | 56                             | -83                            | 146                           |

| 15       | 8        |          |                     | 38                             | -92                            | 158                           |

| 16       |          |          |                     | 20                             | -98                            | 169                           |

| 17       | 9        | 5        |                     | 0                              | -100                           | 180                           |

| 18       |          |          |                     | -20                            | -98                            | 191                           |

| 19       | 10       |          |                     | -38                            | -92                            | 203                           |

| 20       |          |          |                     | -56                            | -83                            | 214                           |

| 21       | 11       | 6        | 3                   | -71                            | -71                            | 225                           |

| 22       |          |          |                     | -83                            | -56                            | 236                           |

| 23       | 12       |          |                     | -92                            | -38                            | 248                           |

| 24       |          |          |                     | -98                            | -20                            | 259                           |

| 25       | 13       | 7        |                     | -100                           | 0                              | 270                           |

| 26       |          |          |                     | -98                            | 20                             | 281                           |

| 表 3. Relative Current and Step Directions | 表 3. | Relative | Current | and | Step | Directions |

|-------------------------------------------|------|----------|---------|-----|------|------------|

|-------------------------------------------|------|----------|---------|-----|------|------------|

| 1/8 STEP | 1/4 STEP | 1/2 STEP | FULL<br>STEP<br>71% | AOUT CURRENT<br>(% FULL-SCALE) | BOUT CURRENT<br>(% FULL-SCALE) | ELECTRICAL<br>ANGLE (DEGREES) |

|----------|----------|----------|---------------------|--------------------------------|--------------------------------|-------------------------------|

| 27       | 14       |          |                     | -92                            | 38                             | 293                           |

| 28       |          |          |                     | -83                            | 56                             | 304                           |

| 29       | 15       | 8        | 4                   | -71                            | 71                             | 315                           |

| 30       |          |          |                     | -56                            | 83                             | 326                           |

| 31       | 16       |          |                     | -38                            | 92                             | 338                           |

| 32       |          |          |                     | -20                            | 98                             | 349                           |

#### 表 3. Relative Current and Step Directions (接下页)

表 4 shows the full step operation with 100% full-scale current. This stepping mode consumes more power than full-step mode with 71% current, but provides a higher torque at high motor RPM.

| 表 4. Full Step | with 100% | Current |

|----------------|-----------|---------|

|----------------|-----------|---------|

| FULL<br>STEP<br>100% | AOUT CURRENT<br>(% FULL-SCALE) | BOUT CURRENT<br>(% FULL-SCALE) | ELECTRICAL ANGLE<br>(DEGREES) |

|----------------------|--------------------------------|--------------------------------|-------------------------------|

| 1                    | 100                            | 100                            | 45                            |

| 2                    | -100                           | 100                            | 135                           |

| 3                    | -100                           | -100                           | 225                           |

| 4                    | 100                            | -100                           | 315                           |

表 5 shows the noncircular 1/2–step operation. This stepping mode consumes more power than circular 1/2-step operation, but provides a higher torque at high motor RPM.

| NON-CIRCULAR 1/2-STEP | AOUT CURRENT<br>(% FULL-SCALE) | BOUT CURRENT<br>(% FULL-SCALE) | ELECTRICAL ANGLE<br>(DEGREES) |  |  |  |

|-----------------------|--------------------------------|--------------------------------|-------------------------------|--|--|--|

| 1                     | 0                              | 100                            | 0                             |  |  |  |

| 2                     | 100                            | 100                            | 45                            |  |  |  |

| 3                     | 100                            | 0                              | 90                            |  |  |  |

| 4                     | 100                            | -100                           | 135                           |  |  |  |

| 5                     | 0                              | -100                           | 180                           |  |  |  |

| 6                     | -100                           | -100                           | 225                           |  |  |  |

| 7                     | -100                           | 0                              | 270                           |  |  |  |

| 8                     | -100                           | 100                            | 315                           |  |  |  |

## 表 5. Non-Circular 1/2-Stepping Current

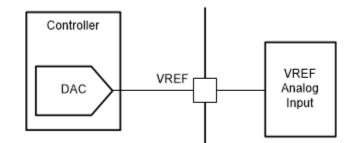

#### 7.3.4 Controlling VREF with an MCU DAC

In some cases, the full-scale output current may need to be changed between many different values, depending on motor speed and loading. The voltage of the VREF pin can be adjusted in the system to change the full-scale current.

In this mode of operation, as the DAC voltage increases, the full-scale regulation current increases as well. For proper operation, the output of the DAC should not rise above 3.3 V.

图 13. Controlling VREF with a DAC Resource

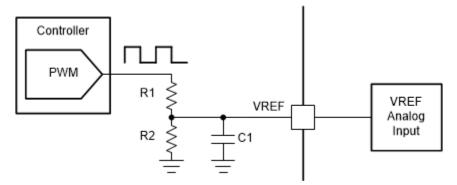

The VREF pin can also be adjusted using a PWM signal and low-pass filter. The R-C time constant for the low-pass filter should be longer than 10 times the period of the PWM signal.

图 14. Controlling VREF With a PWM Resource

#### 7.3.5 Current Regulation

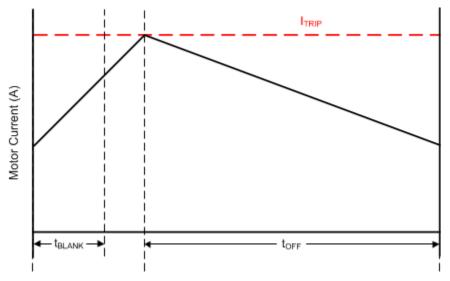

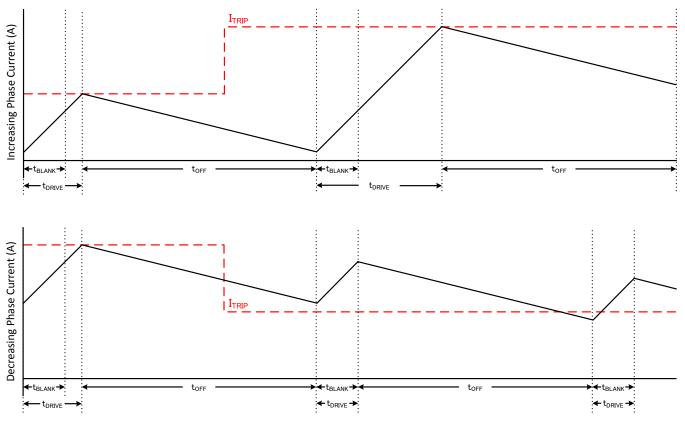

The current through the motor windings is regulated by a PWM current-regulation circuit. When an H-bridge is enabled, current rises through the winding at a rate dependent on the DC voltage, inductance of the winding, and the magnitude of the back EMF present. When the current hits the current regulation threshold, the bridge enters a decay mode for a period of time determined by the TOFF register setting and the selected decay mode to decrease the current. After the off-time expires, the bridge is re-enabled, starting another PWM cycle.

图 15. Current Chopping Waveform

The PWM regulation current is set by a comparator which monitors the voltage across the current sense MOSFETs in parallel with the low-side power MOSFETs. The current sense MOSFETs are biased with a reference current that is the output of a current-mode sine-weighted DAC whose full-scale reference current is set by the voltage at the VREF pin. In addition, the TRQ\_DAC register can further scale the reference current.

Use 公式 1 to calculate the full-scale regulation current.

$$I_{FS}(A) = \frac{V_{REF}(V)}{K_{V}(V/A)} \times TRQ_{DAC}(\%) = \frac{V_{REF}(V) \times TRQ_{DAC}(\%)}{2.2(V/A)}$$

(1)

The TRQ\_DAC is adjusted via the SPI register. 表 6 lists the current scalar value for different inputs.

| TRQ_DAC | CURRENT SCALAR (TRQ) |

|---------|----------------------|

| 0000b   | 100%                 |

| 0001b   | 93.75%               |

| 0010b   | 87.5%                |

| 0011b   | 81.25%               |

| 0100b   | 75%                  |

| 0101b   | 68.75%               |

| 0110b   | 62.5                 |

| 0111b   | 56.25%               |

| 1000b   | 50%                  |

| 1001b   | 43.75%               |

| 1010b   | 37.5%                |

| 1011b   | 31.25%               |

#### 表 6. Torque DAC Settings

| 表 6. To | orque [ | DAC | Settings | (接下页) |

|---------|---------|-----|----------|-------|

|---------|---------|-----|----------|-------|

| TRQ_DAC | CURRENT SCALAR (TRQ) |

|---------|----------------------|

| 1100b   | 25%                  |

| 1101b   | 18.75%               |

| 1110b   | 12.5%                |

| 1111b   | 6.25%                |

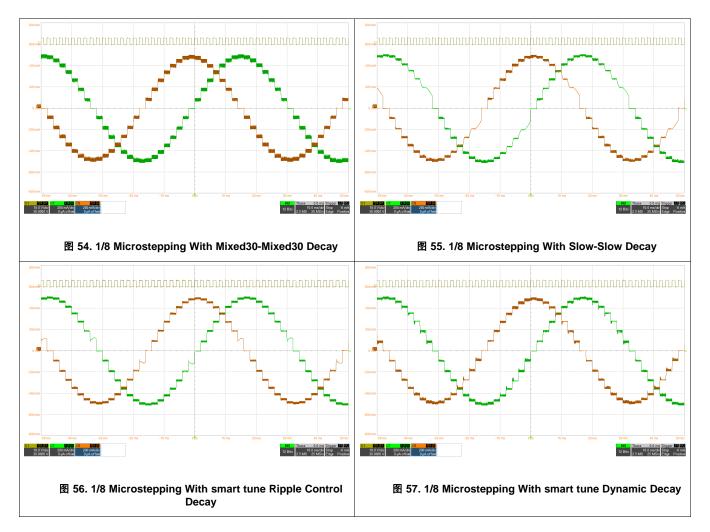

#### 7.3.6 Decay Modes

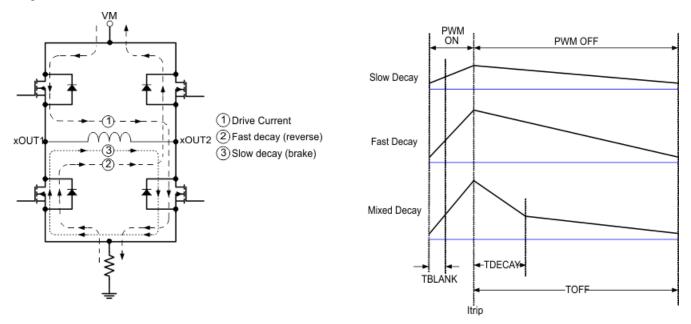

During PWM current chopping, the H-bridge is enabled to drive through the motor winding until the PWM current chopping threshold is reached. This is shown in 🛛 16, Item 1.

图 16. Decay Modes

The decay mode is selected by the DECAY register as shown in 表 7.

| DECAY          | INCREASING STEPS          | DECREASING STEPS          |  |  |  |  |  |

|----------------|---------------------------|---------------------------|--|--|--|--|--|

| 000b           | Slow decay                | Slow decay                |  |  |  |  |  |

| 001b           | Slow decay                | Mixed decay: 30% fast     |  |  |  |  |  |

| 010b           | Slow decay                | Mixed decay: 60% fast     |  |  |  |  |  |

| 011b           | Slow decay                | Fast decay                |  |  |  |  |  |

| 100b           | Mixed decay: 30% fast     | Mixed decay: 30% fast     |  |  |  |  |  |

| 101b           | Mixed decay: 60% fast     | Mixed decay: 60% fast     |  |  |  |  |  |

| 110b           | Smart tune Dynamic Decay  | Smart tune Dynamic Decay  |  |  |  |  |  |

| 111b (default) | Smart tune Ripple Control | Smart tune Ripple Control |  |  |  |  |  |

表 7. Decay Mode Settings

**DRV8889-Q1**

#### www.ti.com.cn

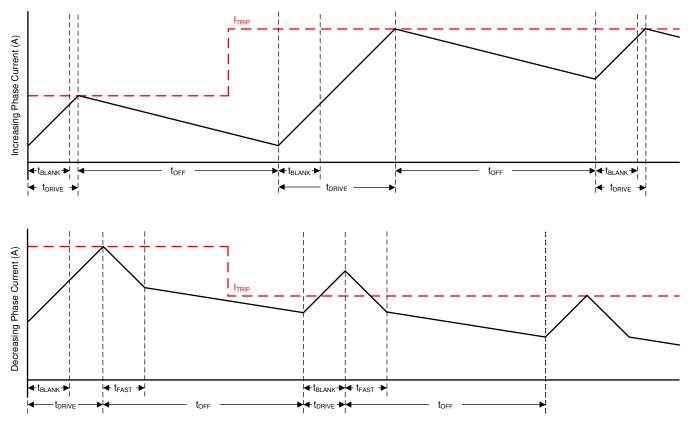

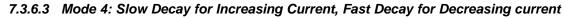

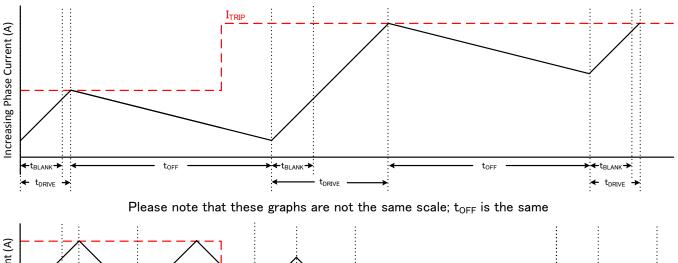

17 defines increasing and decreasing current. For the slow-mixed decay mode, the decay mode is set as slow during increasing current steps and mixed decay during decreasing current steps. In full step and noncircular 1/2step operation, the decay mode corresponding to decreasing steps is always used.

图 17. Definition of Increasing and Decreasing Steps

## 7.3.6.1 Slow Decay for Increasing and Decreasing Current

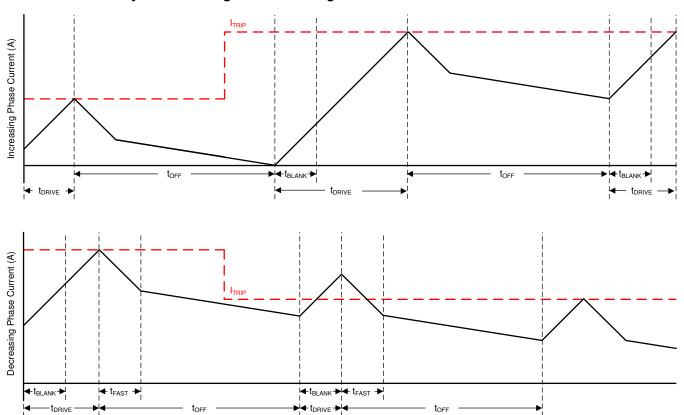

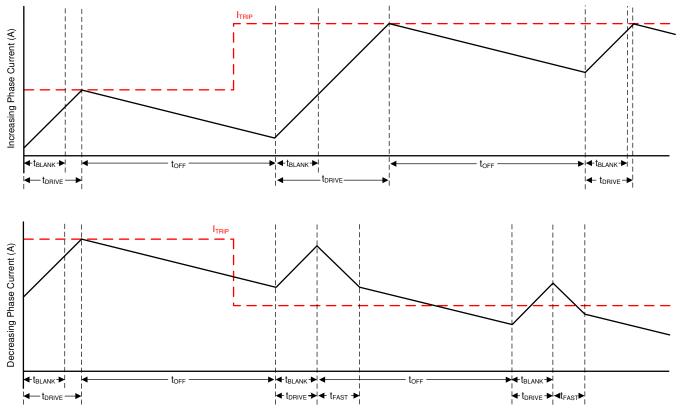

图 18. Slow/Slow Decay Mode

During slow decay, both of the low-side FETs of the H-bridge are turned on, allowing the current to be recirculated.

Slow decay exhibits the least current ripple of the decay modes for a given  $t_{OFF}$ . However on decreasing current steps, slow decay will take a long time to settle to the new  $I_{TRIP}$  level because the current decreases very slowly. If the current at the end of the off time is above the ITRIP level, slow decay will be extended for another off time duration and so on, till the current at the end of the off time is below ITRIP level.

In cases where current is held for a long time (no input in the STEP pin) or at very low stepping speeds, slow decay may not properly regulate current because no back-EMF is present across the motor windings. In this state, motor current can rise very quickly, and may require a large off-time. In some cases this may cause a loss of current regulation, and a more aggressive decay mode is recommended.

#### 7.3.6.2 Slow Decay for Increasing Current, Mixed Decay for Decreasing Current

图 19. Slow-Mixed Decay Mode

Mixed decay begins as fast decay for a time, followed by slow decay for the remainder of the t<sub>OFF</sub> time. In this mode, mixed decay only occurs during decreasing current. Slow decay is used for increasing current.

This mode exhibits the same current ripple as slow decay for increasing current, because for increasing current, only slow decay is used. For decreasing current, the ripple is larger than slow decay, but smaller than fast decay. On decreasing current steps, mixed decay settles to the new  $I_{TRIP}$  level faster than slow decay.

During fast decay, the polarity of the H-bridge is reversed. The H-bridge will be turned off as current approaches zero in order to prevent current flow in the reverse direction. In this mode, fast decay only occurs during decreasing current. Slow decay is used for increasing current.

Fast decay exhibits the highest current ripple of the decay modes for a given t<sub>OFF</sub>. Transition time on decreasing current steps is much faster than slow decay since the current is allowed to decrease much faster.

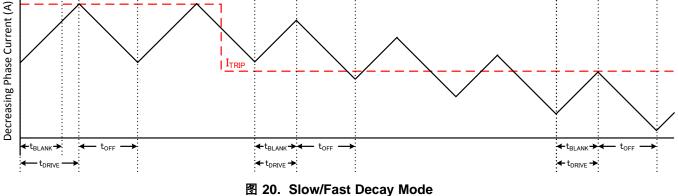

#### 7.3.6.4 Mixed Decay for Increasing and Decreasing Current

图 21. Mixed-Mixed Decay Mode

Mixed decay begins as fast decay for a time, followed by slow decay for the remainder of t<sub>OFF</sub>. In this mode, mixed decay occurs for both increasing and decreasing current steps.

This mode exhibits ripple larger than slow decay, but smaller than fast decay. On decreasing current steps, mixed decay settles to the new  $I_{TRIP}$  level faster than slow decay.

In cases where current is held for a long time (no input in the STEP pin) or at very low stepping speeds, slow decay may not properly regulate current because no back-EMF is present across the motor windings. In this state, motor current can rise very quickly, and requires an excessively large off-time. Increasing or decreasing mixed decay mode allows the current level to stay in regulation when no back-EMF is present across the motor windings.

#### 7.3.6.5 Smart tune Dynamic Decay

The smart tune current regulation schemes are advanced current-regulation control methods compared to traditional fixed off-time current regulation schemes. Smart tune current regulation schemes help the stepper motor driver adjust the decay scheme based on operating factors such as the ones listed as follows:

- · Motor winding resistance and inductance

- Motor aging effects

- Motor dynamic speed and load

- Motor supply voltage variation

- Motor back-EMF difference on rising and falling steps

- Step transitions

- Low-current versus high-current dl/dt

The device provides two different smart tune current regulation modes, named smart tune Dynamic Decay and smart tune Ripple Control.

图 22. Smart tune Dynamic Decay Mode

Smart tune Dynamic Decay greatly simplifies the decay mode selection by automatically configuring the decay mode between slow, mixed, and fast decay. In mixed decay, smart tune dynamically adjusts the fast decay percentage of the total mixed decay time. This feature eliminates motor tuning by automatically determining the best decay setting that results in the lowest ripple for the motor.

The decay mode setting is optimized iteratively each PWM cycle. If the motor current overshoots the target trip level, then the decay mode becomes more aggressive (add fast decay percentage) on the next cycle to prevent regulation loss. If a long drive time must occur to reach the target trip level, the decay mode becomes less aggressive (remove fast decay percentage) on the next cycle to operate with less ripple and more efficiently. On falling steps, smart tune Dynamic Decay automatically switches to fast decay to reach the next step quickly.

Smart tune Dynamic Decay is optimal for applications that require minimal current ripple but want to maintain a fixed frequency in the current regulation scheme.

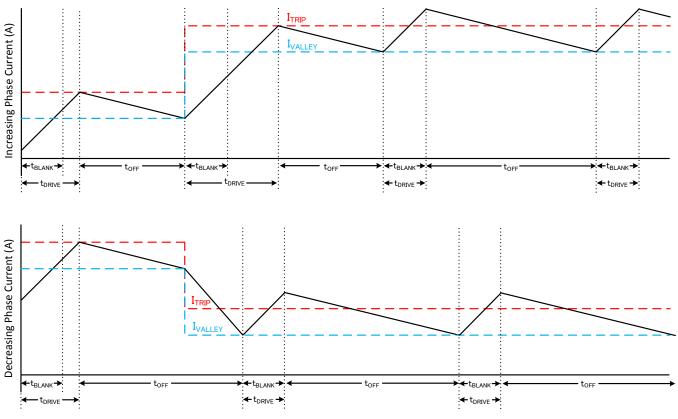

#### 7.3.6.6 Smart tune Ripple Control

图 23. Smart tune Ripple Control Decay Mode

Smart tune Ripple Control operates by setting an  $I_{VALLEY}$  level alongside the  $I_{TRIP}$  level. When the current level reaches  $I_{TRIP}$ , instead of entering slow decay until the  $t_{OFF}$  time expires, the driver enters slow decay until  $I_{VALLEY}$  is reached. Slow decay operates similar to mode 1 in which both low-side MOSFETs are turned on allowing the current to recirculate. In this mode,  $t_{OFF}$  varies depending on the current level and operating conditions.

This method allows much tighter regulation of the current level increasing motor efficiency and system performance. Smart tune Ripple Control can be used in systems that can tolerate a variable off-time regulation scheme to achieve small current ripple in the current regulation.

#### 7.3.7 Blanking Time

After the current is enabled (start of drive phase) in an H-bridge, the current sense comparator is ignored for a period of time ( $t_{BLANK}$ ) before enabling the current-sense circuitry. The blanking time also sets the minimum drive time of the PWM. When the device goes into a drive phase at the end of a slow-decay phase, the blanking time is roughly 500 ns. If the device goes into drive phase at the end of a fast-decay phase, the approximate blanking time is as shown in the following table -

| SLEW_RATE | Blanking Time (t <sub>BLANK</sub> ) |

|-----------|-------------------------------------|

| 00b       | 5.6 µs                              |

| 01b       | 2 µs                                |

| 10b       | 1.5 µs                              |

| 11b       | 860 ns                              |

#### 表 8. Blanking Time

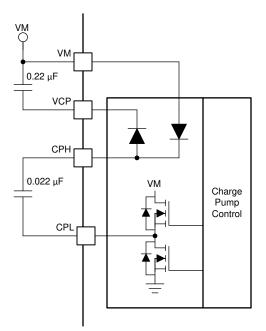

#### 7.3.8 Charge Pump

A charge pump is integrated to supply a high-side N-channel MOSFET gate-drive voltage. The charge pump requires a capacitor between the VM and VCP pins to act as the storage capacitor. Additionally a ceramic capacitor is required between the CPH and CPL pins to act as the flying capacitor.

图 24. Charge Pump Block Diagram

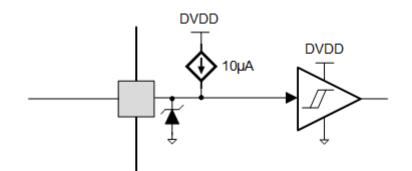

#### 7.3.9 Linear Voltage Regulators

A linear voltage regulator is integrated into the device. The DVDD regulator can be used to provide a reference voltage. DVDD can supply a maximum of 2 mA load. For proper operation, bypass the DVDD pin to GND using a ceramic capacitor.

The DVDD output is nominally 5-V. When the DVDD LDO current load exceeds 2 mA, the output voltage drops significantly.

#### 图 25. Linear Voltage Regulator Block Diagram

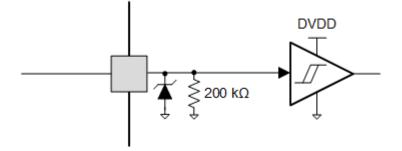

If logic level inputs must be tied permanently high, tying the input to the DVDD pin instead of an external regulator is preferred. This method saves power when the VM pin is not applied or in sleep mode: the DVDD regulator is disabled and current does not flow through the input pulldown resistors. For reference, logic level inputs have a typical pulldown of 200 k $\Omega$ .

The nSLEEP pin cannot be tied to DVDD, else the device will never exit sleep mode.

#### 7.3.10 Logic Level Pin Diagrams

图 26. Logic-Level Input Pin Diagram

图 27 shows the input structure for the logic-level pins DRVOFF, and nSCS.

图 27. Logic-Level with Internal Pull-up Input Pin Diagram

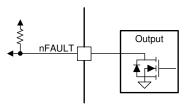

## 7.3.10.1 nFAULT Pin

The nFAULT pin has an open-drain output and should be pulled up to a 5-V or 3.3-V supply. When a fault is detected, the nFAULT pin is logic low. nFAULT pin will be high after power-up. For a 5-V pullup, the nFAULT pin can be tied to the DVDD pin with a resistor. For a 3.3-V pullup, an external 3.3-V supply must be used.

图 28. nFAULT Pin

## 7.3.11 Protection Circuits

The device is fully protected against supply undervoltage, charge pump undervoltage, output overcurrent, device overtemperature, and open load events.

It provides additional diagnostics in the form of stall detection.

7.3.11.1 VM Undervoltage Lockout (UVLO)

#### www.ti.com.cn

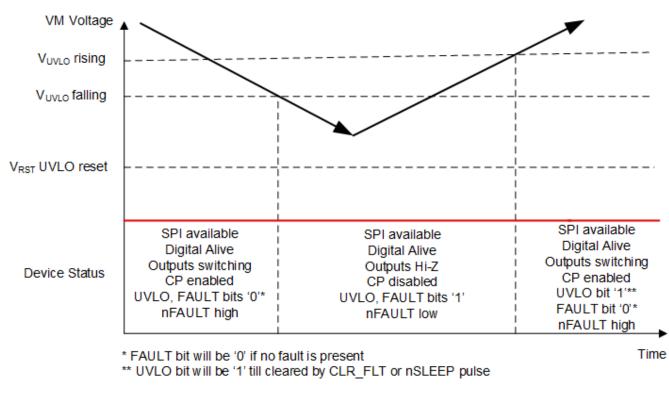

#### 图 29. Supply Voltage Ramp Profile

\* FAULT bit will be '0' if no fault is present

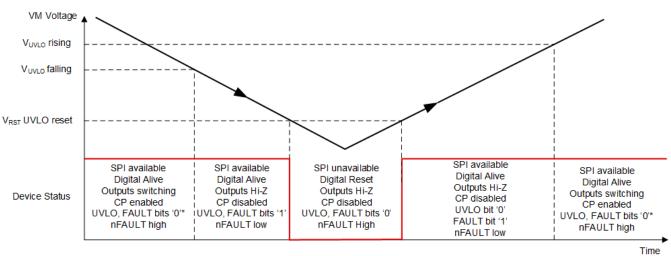

#### 图 30. Supply Voltage Ramp Profile

If at any time the voltage on the VM pin falls below the UVLO falling threshold voltage, all the outputs are disabled (High-Z) and the charge pump (CP) is disabled. Normal operation resumes (motor driver and charge pump) when the VM voltage recovers above the UVLO rising threshold voltage.

When the voltage on the VM pin falls below the UVLO falling threshold voltage (4.25 V typical), but is above the VM UVLO reset voltage ( $V_{RST}$ , 3.9 V maximum), SPI communication is available, the digital core of the device is alive, the FAULT and UVLO bits are made high in the SPI registers and the nFAULT pin is driven low, as shown in  $\mathbb{Z}$  29. From this condition, if the VM voltage recovers above the UVLO rising threshold voltage (4.35 V typical), nFAULT pin is released (is pulled-up to the external voltage), and the FAULT bit is reset, but the UVLO bit remains latched high until cleared through the CLR\_FLT bit or an nSLEEP reset pulse.

When the voltage on the VM pin falls below the VM UVLO reset voltage ( $V_{RST}$ , 3.9 V maximum), SPI communication is unavailable, the digital core is shutdown, the FAULT and UVLO bits are low and the nFAULT pin is high. During the subsequent power-up, when the VM voltage exceeds the  $V_{RST}$  voltage, the digital core comes alive, UVLO bit stays low but the FAULT bit is made high; and the nFAULT pin is pulled low, as shown in  $\mathbb{R}$  30. When the VM voltage exceeds the VM uvLO bit stays low and the nFAULT pin is pulled low.

#### 7.3.11.2 VCP Undervoltage Lockout (CPUV)

If at any time the voltage on the VCP pin falls below the CPUV voltage, all the outputs are disabled, and the nFAULT pin is driven low. The charge pump remains active during this condition. The FAULT and CPUV bits are made high in the SPI registers. Normal operation resumes (motor-driver operation and nFAULT released) when the VCP undervoltage condition is removed. The CPUV bit remains set until it is cleared through the CLR\_FLT bit or an nSLEEP reset pulse.

#### 7.3.11.3 Overcurrent Protection (OCP)

An analog current-limit circuit on each FET limits the current through the FET by removing the gate drive. If this current limit persists for longer than the  $t_{OCP}$  time, the FETs in that particular H-bridge are disabled and the nFAULT pin is driven low. The FAULT and OCP bits are latched high in the SPI registers. For xOUTx to VM short, corresponding OCP\_LSx\_x bit goes high in the DIAG Status 1 register. Similarly, for xOUTx to ground short, corresponding OCP\_HSx\_x bit goes high. For example, for AOUT1 to VM short, OCP\_LS1\_A bit goes high; and for BOUT2 to ground short, the OCP\_HS2\_B bit goes high. The charge pump remains active during this condition. The overcurrent protection can operate in two different modes: latched shutdown and automatic retry.

#### 7.3.11.3.1 Latched Shutdown (OCP\_MODE = 0b)

In this mode, after an OCP event, the relevant outputs are disabled and the nFAULT pin is driven low. Normal operation resumes after nSLEEP cycling or a power cycling. This is the default mode for an OCP event for the device.

#### 7.3.11.3.2 Automatic Retry (OCP\_MODE = 1b)

In this mode, after an OCP event, the relevant outputs are disabled and the nFAULT pin is driven low. Normal operation resumes automatically (motor-driver operation and nFAULT released) after the t<sub>RETRY</sub> time has elapsed and the fault condition is removed.

#### 7.3.11.4 Open-Load Detection (OL)

If the winding current in any coil drops below the open load current threshold  $(I_{OL})$  and the  $I_{TRIP}$  level set by the indexer, and if this condition persists for more than the open load detection time  $(t_{OL})$ , an open-load condition is detected. The EN\_OL bit must be '1' to enable open load detection. When an open load fault is detected, the OL and FAULT bits are latched high in the SPI register and the nFAULT pin is driven low. If the OL\_A bit is high, it indicates an open load fault in winding A, between AOUT1 and AOUT2. Similarly, an open load fault between BOUT1 and BOUT2 causes the OL\_B bit to go high. Normal operation resumes and the nFAULT line is released when the open load condition is removed and a clear faults command has been issued either through the CLR\_FLT bit or an nSLEEP reset pulse. The fault also clears when the device is power cycled or comes out of sleep mode.

If the motor is held at a position corresponding to 0°, 90°, 180° or 270° electrical angles, for more than the open load detection time, open load fault will be flagged, as one of the coil current is zero. This situation does not arise in full-step mode, because the coil currents are never zero.

#### 7.3.11.5 Stall Detection

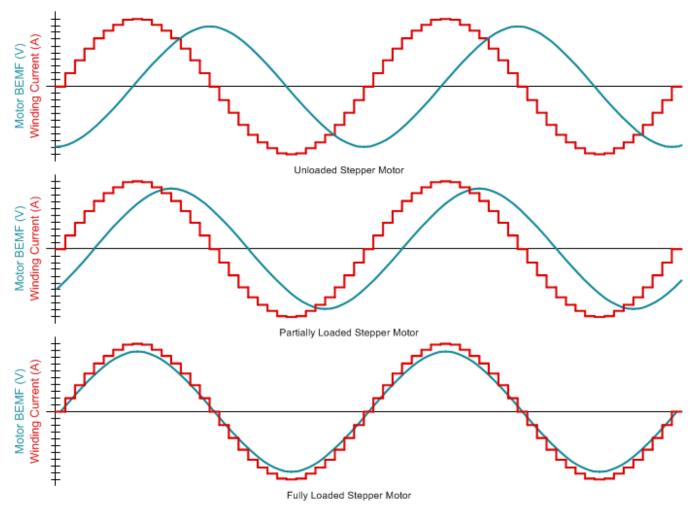

Stepper motors have a distinct relation between the winding current, back-EMF, and mechanical torque load of the motor, as shown in 🛛 31. As motor load approaches the torque capability of the motor at a given winding current, the back-EMF will move in phase with the winding current. By detecting back-emf phase shift between rising and falling current quadrants of the motor current, the DRV8889-Q1 can detect a motor overload stall condition or an end-of-line travel.

图 31. Stall Detection by Monitoring Motor Back-EMF

The Stall Detection algorithm works only when the device is programmed to operate in the smart tune Ripple Control decay mode. The EN\_STL bit in CTRL5 register has to be '1' to enable stall detection. The algorithm compares the back-EMF between the rising and falling current quadrants by monitoring PWM off time and generates a value represented by the 8-bit register TRQ\_COUNT. The comparison is done in such a way that the TRQ\_COUNT value is practically independent of motor current, motor winding resistance, ambient temperature and supply voltage. Full step mode of operation is supported by this algorithm.

For a lightly loaded motor, the TRQ\_COUNT will be a non-zero value. As the motor approaches stall condition, TRQ\_COUNT will approach zero and can be used to detect stall condition. If anytime TRQ\_COUNT falls below the stall threshold (represented by the 8-bit STALL\_TH register), device will detect stall and the STALL, STL and FAULT bits are latched high in the SPI register. To indicate stall detection fault on the nFAULT pin, the STL\_REP bit in CTRL5 register has to be '1'. When the STL\_REP bit is '1', the nFAULT pin will be driven low when stall is detected. In stalled condition, the motor shaft does not spin. The motor starts to spin again when the stall condition is removed and the motor is ramped from zero speed to its target speed. The nFAULT line is released and the fault registers are cleared when a clear faults command has been issued either through the CLR\_FLT bit or an nSLEEP reset pulse.

版权 © 2019–2020, Texas Instruments Incorporated

TRQ\_CNT gets calculated as an average from the latest four electrical half-cycles. Once calculated, it gets updated in the SPI register within 100 ns. After the latest TRQ\_CNT is updated, it retains the value in the SPI register for the next electrical half-cycle, after which the TRQ\_CNT is updated with a new value. The duration of the electrical half-cycle is dependent on microstepping and step-frequency. At the most, it takes two electrical cycles to detect stall.

Stall threshold can be set in two ways – either user can write the STALL\_TH bits, or let the algorithm learn the stall threshold value itself through the stall learning process. The stall learning process requires that the STL\_LRN bit in CTRL5 register is '1' and the motor is deliberately stalled for some time to allow the algorithm to learn the ideal stall threshold. The process takes 16 electrical cycles and at the end of a successful learning, loads the STALL\_TH register with the proper stall threshold bits. Also, the STL\_LRN\_OK bit goes high at the end of successful learning. It is recommended that users set the stall threshold using the stall learning process for proper stall threshold at one speed may not work well for another speed - therefore it is recommended to re-learn the stall threshold when the motor speed changes.

#### 7.3.11.6 Thermal Shutdown (OTSD)

If the die temperature exceeds the thermal shutdown limit ( $T_{OTSD}$ ) all MOSFETs in the H-bridge are disabled, and the nFAULT pin is driven low. The charge pump is disabled in this condition. In addition, the FAULT, TF and OTS bits are latched high. This protection feature cannot be disabled. The overtemperature protection can operate in two different modes: latched shutdown and automatic recovery.

#### 7.3.11.6.1 Latched Shutdown (OTSD\_MODE = 0b)

In this mode, after a OTSD event all the outputs are disabled and the nFAULT pin is driven low. The FAULT, TF and OTS bits are latched high in the SPI register. Normal operation resumes after nSLEEP cycling or a power cycling. This mode is the default mode for a OTSD event.

#### 7.3.11.6.2 Automatic Recovery (OTSD\_MODE = 1b)

In this mode, after a OTSD event all the outputs are disabled and the nFAULT pin is driven low. The FAULT, TF and OTS bits are latched high in the SPI register. Normal operation resumes (motor-driver operation and the nFAULT line released) when the junction temperature falls below the overtemperature threshold limit minus the hysteresis ( $T_{OTSD} - T_{HYS_OTSD}$ ). The FAULT, TF and OTS bits remains latched high indicating that a thermal event occurred until a clear faults command is issued either through the CLR FLT bit or an nSLEEP reset pulse.

#### 7.3.11.7 Overtemperature Warning (OTW)

If the die temperature exceeds the trip point of the overtemperature warning ( $T_{OTW}$ ), the OTW and TF bits are set in the SPI register. The device performs no additional action and continues to function. When the die temperature falls below the hysteresis point ( $T_{HYS_OTW}$ ) of the overtemperature warning, the OTW and TF bits clear automatically. The OTW bit can also be configured to report on the nFAULT pin, and set the FAULT bit in the device, by setting the TW\_REP bit to 1b through the SPI registers. The charge pump remains active during this condition.

#### 7.3.11.8 Undertemperature Warning (UTW)

If the die temperature falls below the trip point of the undertemperature warning ( $T_{UTW}$ ), the UTW and TF bits are set in the SPI register. The device performs no additional action and continues to function. When the die temperature exceeds the hysteresis point ( $T_{HYS_UTW}$ ) of the undertemperature warning, the UTW and TF bits clear automatically. The UTW bit can also be configured to report on the nFAULT pin, and set the FAULT bit in the device, by setting the TW\_REP bit to 1b through the SPI registers. The charge pump remains active during this condition.

| FAULT                      | CONDITION                                    | CONFIGU<br>RATION | ERROR<br>REPORT | H-BRIDGE | CHARGE<br>PUMP | INDEXER   | LOGIC                                 | RECOVERY                                             |

|----------------------------|----------------------------------------------|-------------------|-----------------|----------|----------------|-----------|---------------------------------------|------------------------------------------------------|

| VM undervoltage<br>(UVLO)  | VM < V <sub>UVLO</sub><br>(max 4.35 V)       | —                 | nFAULT /<br>SPI | Disabled | Disabled       | Disabled  | Reset<br>(V <sub>VM</sub> < 3.9<br>V) | Automatic: VM ><br>V <sub>UVLO</sub><br>(max 4.45 V) |

| VCP undervoltage<br>(CPUV) | VCP < V <sub>CPUV</sub><br>(typ VM + 2.25 V) | —                 | nFAULT /<br>SPI | Disabled | Operating      | Operating | Operating                             | VCP > V <sub>CPUV</sub><br>(typ VM + 2.7 V)          |

| 表 9. | Fault | Condition | Summary |

|------|-------|-----------|---------|

|------|-------|-----------|---------|

| FAULT             | CONDITION                           | CONFIGU<br>RATION  | ERROR<br>REPORT | H-BRIDGE  | CHARGE<br>PUMP | INDEXER   | LOGIC     | RECOVERY                                                                 |  |  |  |

|-------------------|-------------------------------------|--------------------|-----------------|-----------|----------------|-----------|-----------|--------------------------------------------------------------------------|--|--|--|

| Overcurrent (OCP) | I <sub>OUT</sub> > I <sub>OCP</sub> | OCP_MO<br>DE = 0b  | nFAULT /<br>SPI | Disabled  | Operating      | Operating | Operating | Latched: CLR_FLT<br>/ nSLEEP                                             |  |  |  |

|                   | (min 2.4 Å)                         | OCP_MO<br>DE = 1b  | nFAULT /<br>SPI | Disabled  | Operating      | Operating | Operating | Automatic retry:<br>t <sub>RETRY</sub>                                   |  |  |  |

| Open Load (OL)    | No load detected                    | EN_OL =<br>1b      | nFAULT /<br>SPI | Operating | Operating      | Operating | Operating | Report only                                                              |  |  |  |

| Stall Detection   | Stall / stuck motor                 | STL_REP<br>= 0b    | SPI             | Operating | Operating      | Operating | Operating | No action                                                                |  |  |  |

| (STALL)           |                                     | STL_REP<br>= 1b    | nFAULT /<br>SPI | Operating | Operating      | Operating | Operating | Report only                                                              |  |  |  |

| Overtemperature   | T <sub>J</sub> > T <sub>OTW</sub>   | TW_REP<br>= 1b     | nFAULT /<br>SPI | Operating | Operating      | Operating | Operating | No action                                                                |  |  |  |

| Warning (OTW)     |                                     | TW_REP<br>= 0b     | SPI             | Operating | Operating      | Operating | Operating | Automatic: T <sub>J</sub> <<br>T <sub>OTW</sub> - T <sub>HYS_OTW</sub>   |  |  |  |