# 2-mm x 2-mm 小外形尺寸无引线 (SON) 封装内的 3-MHz 2-A 降压转换器

查询样品: TLV62065-Q1

# 特性

- 符合汽车应用要求

- 具有下列结果的 AEC-Q100 测试指南:

- 器件温度 2 级: -40°C 至 105°C 的环境运行温度范围

- 器件人体模型 (HBM) 静电放电 (ESD) 分类等级 H2

- 器件充电器件模型 (CDM) ESD 分类等级 C3B

- V<sub>IN</sub> 范围从 2.9 V 至 5.5 V

- 效率高达 97%

- 省电模式 / MHz 固定脉宽调制 (PWM) 模式

- PWM 模式中的输出电压准确度为 ±2.0%

- 输出放电功能

- 典型值为 18µA 的静态电流

- 针对最低压降的 100% 占空比

- 要获得改进的特性集,请见 TPS62065

- 采用 2-mm x 2-mm x 0.75-mm SON 封装

# 应用范围

- 负载点 (POL)

- 笔记本电脑、掌上电脑

- 便携式媒体播放器

- 机顶盒

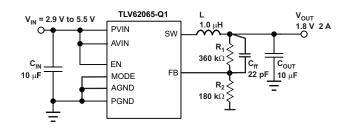

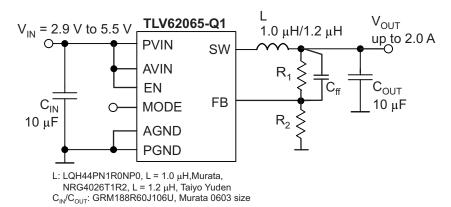

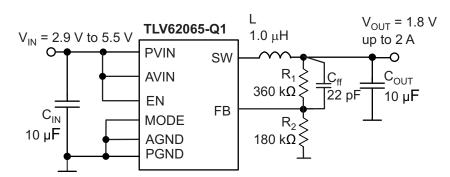

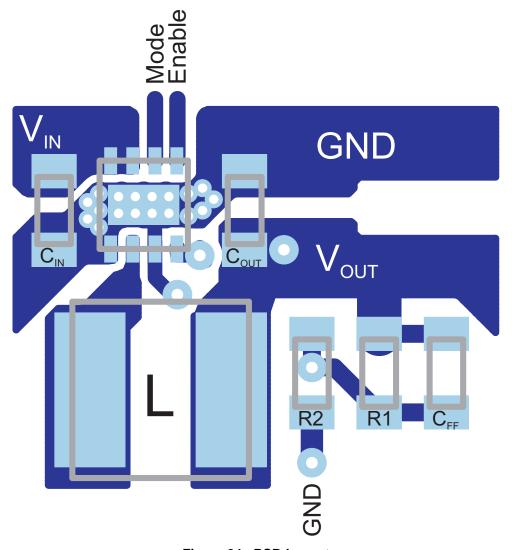

### TYPICAL APPLICATION CIRCUIT

### 说明

TLV62065-Q1 是一款具有 1.2-V 固定输出电压的高效、同步降压、dc-dc 转换器。 它提供高达 2 A 的输出电流。

借助于 2.9 V 至 5.5 V 的输入电压范围,此器件非常适合用于针对 5-V 或者 3.3-V 系统电源轨的电源转换。 TLV62065-Q1 运行在 3-MHz 固定频率下并在轻负载电流时进入省电模式运行以保持整个负载电流范围内的高效率。 对于低噪声应用,通过将 MODE 引脚上拉至高电平,可强制 TLV62065-Q1 进入固定频率 PWM 模式。

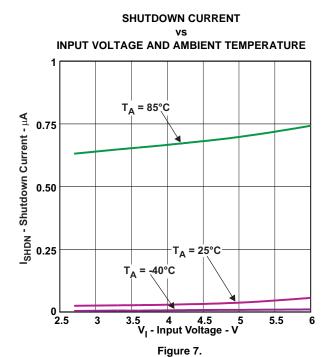

在关断模式下,流耗减至少于 **1µA** 并且一个内部电路 将输出电容器放电。

TLV62065-Q1具有 1-μH 电感器和 10-μF 输出电容器。

TLV62065-Q1 采用 2-mm x 2-mm x 0.75-mm 8-引脚 SON 封装。

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### ORDERING INFORMATION(1)

| T <sub>A</sub> | PAC       | KAGE         | ORDERABLE PART NUMBER | TOP-SIDE MARKING |   |  |

|----------------|-----------|--------------|-----------------------|------------------|---|--|

| –40°C to 105°C | WSON -DSG | Reel of 3000 | TLV62065TDSGRQ1       | SCD              | Ì |  |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                   |                                                                 | VAL        | UE                        | UNIT |

|-------------------|-----------------------------------------------------------------|------------|---------------------------|------|

|                   |                                                                 | MIN        | MAX                       |      |

| Voltage range (2) | AVIN, PVIN                                                      | -0.3       | 7                         |      |

|                   | EN, MODE, FB                                                    | -0.3 to    | V <sub>IN</sub> + 0.3 < 7 | V    |

|                   | SW                                                              | -0.3       | 7                         |      |

| Current (source)  | Peak output                                                     | Internally | limited                   | Α    |

| FCD seties        | Human-body model (HBM) AEC-Q100<br>Classification Level H2      |            | 2                         | kV   |

| ESD rating        | Charged-device model (CDM) AEC-Q100<br>Classification Level C3B |            | 750                       | V    |

| T                 | T <sub>J</sub>                                                  | -40        | 140                       | 00   |

| Temperature       | T <sub>stg</sub>                                                | -65        | 150                       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# THERMAL INFORMATION

|                       |                                              | TLV62065-Q1 |       |

|-----------------------|----------------------------------------------|-------------|-------|

|                       | THERMAL METRIC                               | DSG         | UNITS |

|                       |                                              | 8 PINS      |       |

| $\theta_{JA}$         | Junction-to-ambient thermal resistance       | 92.2        |       |

| $\theta_{JC(top)}$    | Junction-to-case(top) thermal resistance     | 70.4        |       |

| $\theta_{JB}$         | Junction-to-board thermal resistance         | 46.6        | 9004  |

| Ψлт                   | Junction-to-top characterization parameter   | 1.7         | °C/W  |

| ΨЈВ                   | Junction-to-board characterization parameter | 46.3        |       |

| $\theta_{JC(bottom)}$ | Junction-to-case(bottom) thermal resistance  | 39.7        |       |

<sup>(2)</sup> All voltage values are with respect to the network ground terminal.

### RECOMMENDED OPERATING CONDITIONS

|                                        |                                             | MIN | NOM | MAX             | UNIT |

|----------------------------------------|---------------------------------------------|-----|-----|-----------------|------|

| AV <sub>IN</sub> ,<br>PV <sub>IN</sub> | Supply voltage                              | 2.9 |     | 5.5             | V    |

|                                        | Output current capability                   |     |     | 2000            | mA   |

|                                        | Output voltage range for adjustable voltage | 0.8 |     | V <sub>IN</sub> | V    |

| L                                      | Effective inductance range                  | 0.7 | 1   | 1.6             | μΗ   |

| C <sub>OUT</sub>                       | Effective output-capacitance range          | 4.5 | 10  | 22              | μF   |

| T <sub>A</sub>                         | Operating ambient temperature (1)           | -40 |     | 105             | °C   |

| TJ                                     | Operating junction temperature              | -40 |     | 140             | °C   |

<sup>(1)</sup> In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A(max)})$  is dependent on the maximum operating junction temperature  $(T_{J(max)})$ , the maximum power dissipation of the device in the application (PD(max)), and the junction-to-ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A(max)} = T_{J(max)} - (\theta_{JA} \times P_{D(max)})$

### **ELECTRICAL CHARACTERISTICS**

Over full operating ambient temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for condition  $V_{IN}$  = EN = 3.6 V. External components  $C_{IN}$  = 10  $\mu F$  0603,  $C_{OUT}$  = 10  $\mu F$  0603, L = 1  $\mu H$ , see the parameter measurement information.

|                                                  | PARAMETER                                           | TEST CONDITIONS                                                                                                | MIN  | TYP  | MAX  | UNIT |  |

|--------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| SUPPLY                                           |                                                     |                                                                                                                |      |      |      |      |  |

| V <sub>IN</sub>                                  | Input voltage range                                 |                                                                                                                | 2.9  |      | 5.5  | V    |  |

| IQ                                               | Operating quiescent current                         | I <sub>OUT</sub> = 0 mA, device operating in PFM mode and not device not switching                             |      | 18   |      | μΑ   |  |

| I <sub>SD</sub>                                  | Shutdown current                                    | EN = GND, current into AVIN and PVIN combined                                                                  |      | 0.1  | 5    | μΑ   |  |

| V                                                |                                                     | Falling                                                                                                        | 1.73 | 1.78 | 1.83 | V    |  |

| V <sub>UVLO</sub> Undervoltage lockout threshold |                                                     | Rising                                                                                                         | 1.9  | 1.95 | 1.99 | V    |  |

| ENABLE, N                                        | IODE                                                |                                                                                                                |      |      | ·    |      |  |

| V <sub>IH</sub>                                  | High-level input voltage                            | 2.9 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                | 1    |      | 5.5  | V    |  |

| $V_{IL}$                                         | Low-level input voltage                             | 2.9 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                | 0    |      | 0.4  | V    |  |

| I <sub>IN</sub>                                  | Input bias current                                  | EN, MODE tied to GND or AVIN                                                                                   |      | 0.01 | 1    | μA   |  |

| POWER SV                                         | ИТСН                                                |                                                                                                                |      |      |      |      |  |

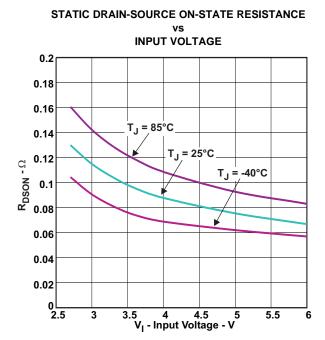

|                                                  |                                                     | $V_{IN} = 3.6 \text{ V}^{(1)}$                                                                                 |      | 120  | 180  |      |  |

| r <sub>DS(on)</sub>                              | High-side MOSFET on-resistance                      | $V_{IN} = 5 V^{(1)}$                                                                                           |      | 95   | 150  | mΩ   |  |

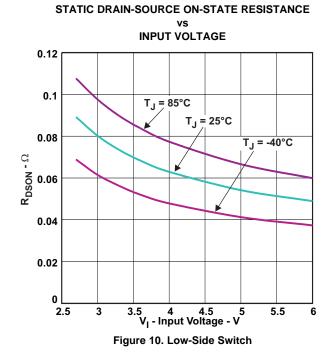

|                                                  |                                                     | $V_{IN} = 3.6 V^{(1)}$                                                                                         |      | 90   | 130  |      |  |

| r <sub>DS(on)</sub>                              | Low-side MOSFET on-resistance                       | $V_{IN} = 5 V^{(1)}$                                                                                           |      | 75   | 100  | mΩ   |  |

| I <sub>LIMF</sub>                                | Forward current limit MOSFET high-side and low-side | 3 V ≤ V <sub>IN</sub> ≤ 3.6 V                                                                                  | 2300 | 2750 |      | mA   |  |

| +                                                | Thermal shutdown                                    | Increasing junction temperature                                                                                |      | 150  |      |      |  |

| $T_{SD}$                                         | Thermal shutdown hysteresis                         | Decreasing junction temperature                                                                                |      | 10   |      | °C   |  |

| OSCILLATO                                        | OR .                                                |                                                                                                                |      |      |      |      |  |

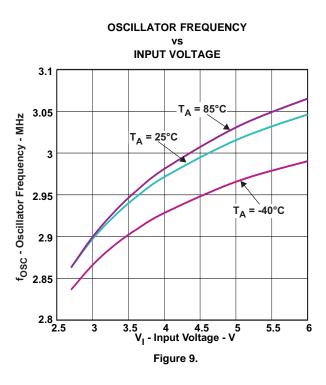

| f <sub>SW</sub>                                  | Oscillator frequency                                | 2.9 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                | 2.6  | 3    | 3.4  | MHz  |  |

| OUTPUT                                           |                                                     |                                                                                                                |      |      |      |      |  |

| $V_{ref}$                                        | Reference voltage                                   |                                                                                                                |      | 600  |      | mV   |  |

| V <sub>FB(PWM)</sub>                             | Feedback voltage, PWM mode                          | PWM operation, MODE = $V_{IN}$ ,<br>2.9 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V, 0-mA load                       | -2.0 | 0    | 2.0  | 0.4  |  |

| $V_{FB(PFM)}$                                    | Feedback voltage, PFM mode, voltage positioning     | k voltage, PFM mode, Device in PFM mode, voltage positioning active <sup>(2)</sup>                             |      | 1    |      | %    |  |

|                                                  | Load regulation                                     |                                                                                                                |      | -0.5 |      | %/A  |  |

| $V_{FB}$                                         | Line regulation                                     |                                                                                                                |      | 0    |      | %/V  |  |

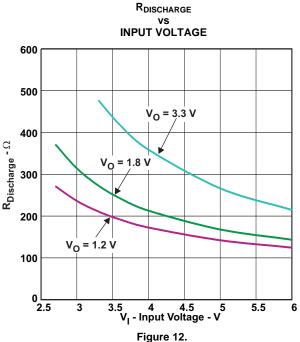

| R <sub>(Discharge)</sub>                         | Internal discharge resistor                         | Activated with EN = GND, 2.9 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V, 0.8 V $\leq$ V <sub>OUT</sub> $\leq$ 3.6 V |      | 200  |      | Ω    |  |

| t <sub>START</sub>                               | Start-up time                                       | Time from active EN to reach 95% of V <sub>OUT</sub>                                                           |      | 500  |      | μs   |  |

<sup>(1)</sup> Maximum value applies for  $T_J = 85$ °C.

<sup>(2)</sup> In PFM mode, the internal reference voltage is set to typ. 1.01 x V<sub>ref</sub>. See the parameter measurement information.

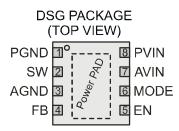

# **PIN ASSIGNMENTS**

# **TERMINAL FUNCTIONS**

| TER              | MINAL | 1/0 | DESCRIPTION                                                                                                                                                                                                            |

|------------------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.   | 1/0 | DESCRIPTION                                                                                                                                                                                                            |

| AGND             | 3     | IN  | Analog GND supply pin for the control circuit.                                                                                                                                                                         |

| AV <sub>IN</sub> | 7     | IN  | Analog $V_{\text{IN}}$ power supply for the control circuit. Must be connected to PVIN and input capacitor.                                                                                                            |

| EN               | 5     | IN  | This is the enable pin of the device. Pulling this pin low forces the device into shutdown mode. Pulling this pin high enables the device. This pin must be terminated.                                                |

| FB               | 4     | IN  | Feedback pin for the internal regulation loop. Connect the external resistor divider to this pin. In the case of fixed output voltage option, connect this pin directly to the output capacitor.                       |

| MODE             | 6     | IN  | MODE pin = high forces the device to operate in fixed-frequency PWM mode. MODE pin = low enables the power-save mode with automatic transition from PFM mode to fixed-frequency PWM mode. This pin must be terminated. |

| PGND             | 1     | PWR | GND supply pin for the output stage                                                                                                                                                                                    |

| PV <sub>IN</sub> | 8     | PWR | V <sub>IN</sub> power-supply pin for the output stage                                                                                                                                                                  |

| SW               | 2     | OUT | This is the switch pin and is connected to the internal MOSFET switches. Connect the external inductor between this terminal and the output capacitor.                                                                 |

| Thermal pad      | _     | _   | For good thermal performance, this pad must be soldered to the land pattern on the PCB. This pad should be used as device GND.                                                                                         |

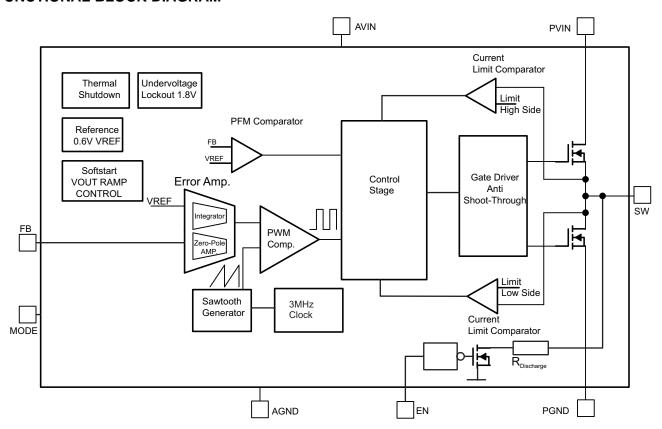

### **FUNCTIONAL BLOCK DIAGRAM**

# PARAMETER MEASUREMENT INFORMATION

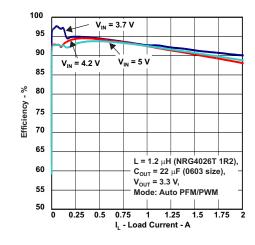

### **TYPICAL CHARACTERISTICS**

# **Table 1. Table of Graphs**

|                              |                                    |                                                                                                                            | FIGURE    |  |  |  |  |

|------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

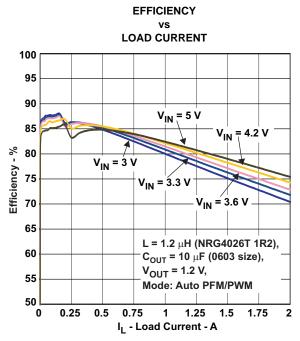

|                              |                                    | Load Current, V <sub>OUT</sub> = 1.2 V, Auto PF//PWM Mode, Linear Scale                                                    | Figure 1  |  |  |  |  |

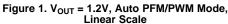

|                              | Efficiency                         | Load Current, V <sub>OUT</sub> = 1.8 V, Auto PFM/PWM Mode, Linear Scale                                                    | Figure 2  |  |  |  |  |

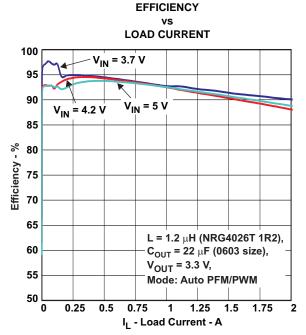

| 1                            |                                    | Load Current, V <sub>OUT</sub> = 3.3 V, PFM/PWM Mode, Linear Scale                                                         | Figure 3  |  |  |  |  |

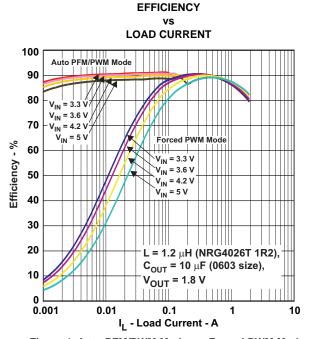

|                              |                                    | Load Current, V <sub>OUT</sub> = 1.8 V, Auto PFM/PWM Mode vs. Forced PWM Mode, Logarithmic Scale                           | Figure 4  |  |  |  |  |

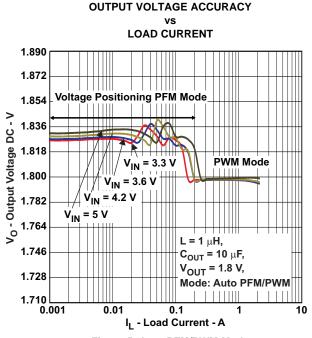

|                              | Output Valtage Assurage            | Load Current, V <sub>OUT</sub> = 1.8 V, Auto PFM/PWM Mode                                                                  | Figure 5  |  |  |  |  |

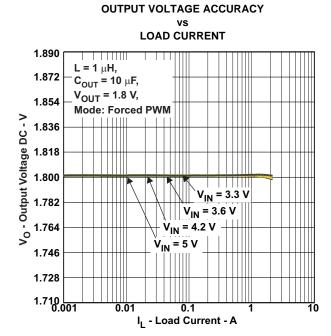

|                              | Output Voltage Accuracy            | Load Current, V <sub>OUT</sub> = 1.8 V, Forced PWM Mode                                                                    | Figure 6  |  |  |  |  |

|                              | Shutdown Current                   | Input Voltage and Ambient Temperature                                                                                      | Figure 7  |  |  |  |  |

|                              | Quiescent Current                  | Input Voltage                                                                                                              | Figure 8  |  |  |  |  |

|                              | Oscillator Frequency Input Voltage |                                                                                                                            |           |  |  |  |  |

| Static Drain-Source On-State |                                    | Input Voltage, Low-Side Switch                                                                                             | Figure 10 |  |  |  |  |

|                              | Resistance                         | Input Voltage, High-Side Switch                                                                                            | Figure 11 |  |  |  |  |

|                              | R <sub>DISCHARGE</sub>             | Input Voltage vs. V <sub>OUT</sub>                                                                                         | Figure 12 |  |  |  |  |

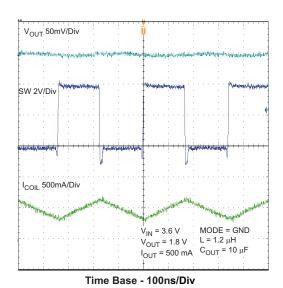

|                              | Typical Operation                  | PWM Mode, $V_{IN}$ = 3.6 V, $V_{OUT}$ = 1.8 V, 500 mA, L = 1.2 $\mu$ H, $C_{OUT}$ = 10 $\mu$ F                             | Figure 13 |  |  |  |  |

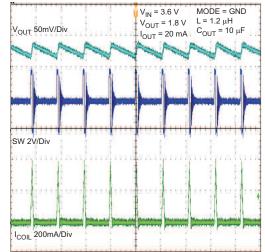

|                              | Typical Operation                  | PFM Mode, $V_{IN} = 3.6 \text{ V}$ , $V_{OUT} = 1.8 \text{ V}$ , 20 mA, $L = 1.2 \mu\text{H}$ , $C_{OUT} = 10 \mu\text{F}$ | Figure 14 |  |  |  |  |

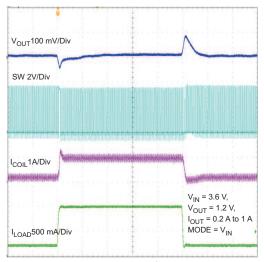

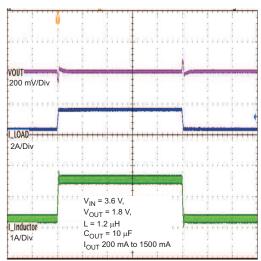

|                              |                                    | PWM Mode, $V_{IN}$ = 3.6 V, $V_{OUT}$ = 1.2 V, 0.2 mA to 1 A                                                               | Figure 15 |  |  |  |  |

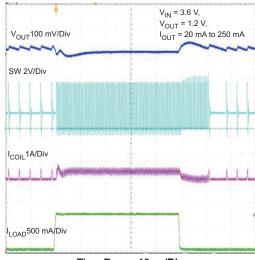

|                              | Load Transient                     | PFM Mode, $V_{IN}$ = 3.6 V, $V_{OUT}$ = 1.2 V, 20 mA to 250 mA                                                             | Figure 16 |  |  |  |  |

|                              |                                    | $V_{IN} = 3.6 \text{ V}, V_{OUT} = 1.8 \text{ V}, 200 \text{ mA to } 1500 \text{ mA}$                                      | Figure 17 |  |  |  |  |

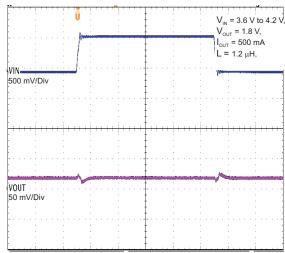

|                              | Line Transient                     | PWM Mode, $V_{IN}$ = 3.6 V to 4.2 V, $V_{OUT}$ = 1.8 V, 500 mA                                                             | Figure 18 |  |  |  |  |

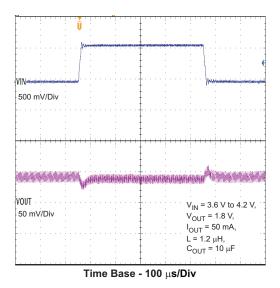

|                              | LINE HANSIETIL                     | PFM Mode, V <sub>IN</sub> = 3.6 V to 4.2 V, V <sub>OUT</sub> = 1.8 V, 500 mA                                               | Figure 19 |  |  |  |  |

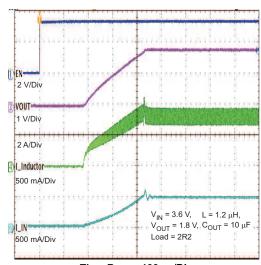

|                              | Startup into Load                  | $V_{IN} = 3.6 \text{ V}, V_{OUT} = 1.8 \text{ V}, Load = 2.2-\Omega$                                                       | Figure 20 |  |  |  |  |

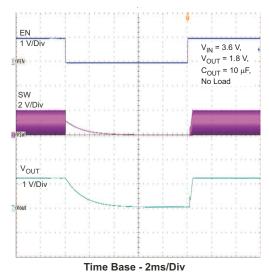

|                              | Output Discharge                   | V <sub>IN</sub> = 3.6 V, V <sub>OUT</sub> = 1.8 V, No Load                                                                 | Figure 21 |  |  |  |  |

Figure 2. V<sub>OUT</sub> = 1.8V, Auto PFM/PWM Mode, Linear Scale

Figure 3. V<sub>OUT</sub> = 3.3V, Auto PFM/PWM Mode, Linear Scale

Figure 5. Auto PFM/PWM Mode

Figure 4. Auto PFM/PWM Mode vs. Forced PWM Mode, Logarithmic Scale

Figure 6. Forced PWM Mode

Figure 11. High-Side Switch

Figure 13. Typical Operation (PWM Mode)

rigure 12.

Time Base - 4μs/Div

Figure 14. Typical Operation (PFM Mode)

Time Base - 10 µs/Div

Figure 15. Load Transient Response PWM Mode 0.2A To 1A

Time Base - 100µs/Div

Figure 17. Load Transient Response 200 mA To 1500 mA

Time Base - 10 µs/Div

Figure 16. Load Transient PFM Mode 20 mA to 250mA

Time Base - 100 µs/Div

Figure 18. Line Transient Response PWM Mode

Figure 19. Line Transient PFM Mode

Time Base - 100  $\mu$ s/Div

Figure 20. Start-Up Into Load – V<sub>OUT</sub> 1.8 V

Figure 21. Output Discharge

#### **DETAILED DESCRIPTION**

### **OPERATION**

The TLV62065-Q1 step-down converter operates with typically 3-MHz fixed-frequency pulse-width modulation (PWM) at moderate to heavy load currents. At light load currents, the converter can automatically enter power-save mode, and operates then in pulse-frequency mode (PFM).

During PWM operation, the converter uses a unique fast-response voltage-mode controller scheme with input voltage feed-forward to achieve good line and load regulation, allowing the use of small ceramic input and output capacitors. At the beginning of each clock cycle initiated by the clock signal, the high-side MOSFET switch is turned on. The current flows now from the input capacitor via the high-side MOSFET switch through the inductor to the output capacitor and load. During this phase, the current ramps up until the PWM comparator trips and the control logic turns off the switch. The current limit comparator also turns off the switch in case the current limit of the high-side MOSFET switch is exceeded. After a dead time preventing shoot-through current, the low-side MOSFET rectifier is turned on and the inductor current ramps down. The current flows now from the inductor to the output capacitor and to the load. It returns back to the inductor through the low-side MOSFET rectifier.

The next cycle is initiated by the clock signal again turning off the low-side MOSFET rectifier and turning on the high-side MOSFET switch.

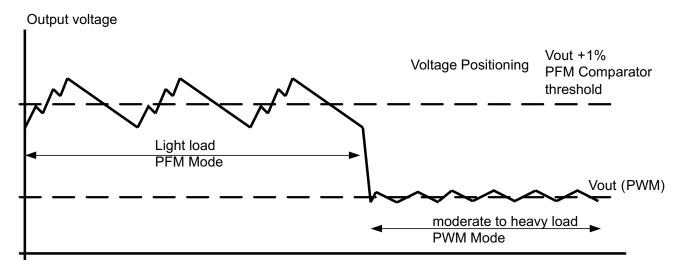

### **POWER SAVE MODE**

Pulling the TLV62065-Q1 MODE pin low enables power-save mode. If the load current decreases, the converter enters power-save mode operation automatically. In power-save mode, the converter skips switching and operates with reduced frequency in the PFM mode with a minimum quiescent current to maintain high efficiency. The converter positions the output voltage typically 1% above the nominal output voltage. This voltage-positioning feature minimizes voltage drops caused by a sudden load step.

The transition from PWM mode to PFM mode occurs once the inductor current in the low-side MOSFET switch becomes zero, which indicates discontinuous conduction mode.

In power-save mode, a PFM comparator monitors the output voltage. As the output voltage falls below the PFM comparator threshold of  $V_{OUTnominal} + 1\%$ , the device starts a PFM current pulse. For this, the high-side MOSFET switch turns on and the inductor current ramps up. After the on-time expires, the switch is turned off and the low-side MOSFET switch is turned on until the inductor current becomes zero.

The converter effectively delivers a current to the output capacitor and the load. If the load is below the delivered current, the output voltage rises. If the output voltage is equal to or higher than the PFM comparator threshold, the device stops switching and enters a sleep mode with typ. 18-µA current consumption.

In case the output voltage is still below the PFM comparator threshold, further PFM current pulses are generated until the PFM comparator threshold is reached. The converter starts switching again once the output voltage drops below the PFM comparator threshold due to the load current.

The PFM mode is exited and PWM mode entered in case the output current can no longer be supported in PFM mode.

Figure 22. Power Save Mode Operation with automatic Mode transition

### 100% Duty Cycle Low-Dropout Operation

The device starts to enter 100% duty cycle mode as the input voltage comes close to the nominal output voltage. In order to maintain the output voltage, the high-side MOSFET switch is turned on 100% for one or more cycles.

With further decreasing VIN, the high-side MOSFET switch is turned on completely. In this case, the converter offers a low input-to-output voltage differential. This is particularly useful in battery-powered applications to achieve longest operation time by taking full advantage of the whole battery voltage range.

The minimum input voltage to maintain regulation depends on the load current and output voltage, and can be calculated as:

$V_{IN}min = V_{O}max + I_{O}max \times (R_{DS(on)}max + R_{L})$

With:

I<sub>O</sub>max = maximum output current

$R_{DS(on)}$ max = maximum P-channel switch  $R_{DS(on)}$ .

$R_1 = DC$  resistance of the inductor

V<sub>O</sub>max = nominal output voltage plus maximum output voltage tolerance

### **Undervoltage Lockout**

The undervoltage lockout circuit prevents the device from malfunctioning at low input voltages and from excessive discharge of the battery. It disables the output stage of the converter once the falling VIN trips the undervoltage lockout threshold  $V_{UVLO}$ . The undervoltage lockout threshold  $V_{UVLO}$  for falling  $V_{IN}$  is typically 1.78 V. The device starts operation once the rising  $V_{IN}$  trips the undervoltage lockout threshold  $V_{UVLO}$  again at typically 1.95 V.

### **Output Capacitor Discharge**

With EN = GND, the device enters shutdown mode and disables all internal circuits. An internal resistor connects the SW pin is to PGND to discharge the output capacitor. This feature ensures start-up with a discharged output capacitor once the converter is enabled again and prevents *floating* charge on the output capacitor. The output voltage ramps up monotonic, starting from 0 V.

#### MODE SELECTION

The MODE pin allows mode selection between forced PWM mode and power-save mode.

Connecting this pin to GND enables the power-save mode with automatic transition between PWM and PFM mode. Pulling the MODE pin high forces the converter to operate in fixed-frequency PWM mode even at light load currents. This allows simple filtering of the switching frequency for noise-sensitive applications. In this mode, the efficiency is lower compared to the power-save mode during light loads.

The condition of the MODE pin can be changed during operation and allows efficient power management by adjusting the operation mode of the converter to the specific system requirements.

#### **ENABLE**

The device is enabled by setting EN pin to high. At first, the internal reference is activated and the internal analog circuits are settled. Afterwards, the soft start is activated and the output voltage is ramped up. The output voltages reaches 95% of its nominal value within  $t_{START}$  of typically 500  $\mu$ s after the device has been enabled. The EN input can be used to control power sequencing in a system with various dc-dc converters. The EN pin can be connected to the output of another converter, to drive the EN pin high and get a sequencing of supply rails. With EN = GND, the device enters shutdown mode. In this mode, all circuits are disabled and the SW pin is connected to PGND via an internal resistor to discharge the output.

### **SOFT START**

The TLV62065-Q1 has an internal soft-start circuit that controls the ramp-up of the output voltage. Once the converter is enabled and the input voltage is above the undervoltage lockout threshold,  $V_{UVLO}$ , the output voltage ramps up from 5% to 95% of its nominal value within  $t_{Ramp}$  of typ. 250  $\mu$ s.

This limits the inrush current in the converter during start-up and prevents possible input-voltage drops when a battery or high-impedance power source is used.

During soft start, the switch current limit is reduced to 1/3 of its nominal value,  $I_{LIMF}$ , until the output voltage reaches 1/3 of its nominal value. Once the output voltage trips this threshold, the device operates with its nominal current limit  $I_{LIMF}$ .

### INTERNAL CURRENT LIMIT / FOLD-BACK CURRENT LIMIT FOR SHORT-CIRCUIT PROTECTION

During normal operation, the high-side and low-side MOSFET switches are protected by their current limits,  $I_{LIMF}$ . Once the high-side MOSFET switch reaches its current limit, it is turned off and the low-side MOSFET switch is turned on. The high-side MOSFET switch can only turn on again once the current in the low-side MOSFET switch decreases below its current limit,  $I_{LIMF}$ . The device is capable of providing peak inductor currents up to its internal current limit  $I_{LIMF}$ .

As soon as the switch-current limits are hit and the output voltage falls below 1/3 of the nominal output voltage due to an overload or short-circuit condition, the foldback current limit is enabled. In this case, the switch-current limit is reduced to 1/3 of the nominal value, I<sub>LIME</sub>.

Because the short-circuit protection is enabled during start-up, the device does not deliver more than 1/3 of its nominal current limit, I<sub>LIMF</sub>, until the output voltage exceeds 1/3 of the nominal output voltage. This must be considered when a load which acts as a current sink is connected to the output of the converter.

#### THERMAL SHUTDOWN

As soon as the junction temperature,  $T_J$ , exceeds 150°C (typical) the device goes into thermal shutdown. In this mode, the high-side and low-side MOSFETs are turned off. The device continues its operation with a soft start once the junction temperature falls below the thermal shutdown hysteresis.

#### **APPLICATION INFORMATION**

Figure 23. TLV62065-Q1 1.8V Adjustable Output Voltage Configuration

### **OUTPUT VOLTAGE SETTING**

The output voltage can be calculated to:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R_1}{R_2}\right)$$

with an internal reference voltage V<sub>REF</sub> typically 0.6 V.

To minimize the current through the feedback divider network,  $R_2$  should be within the range of 120 k $\Omega$  to 360 k $\Omega$ . The sum of  $R_1$  and  $R_2$  should not exceed approximately 1 M $\Omega$ , to keep the network robust against noise. An external feed-forward capacitor  $C_{\rm ff}$  is required for optimum regulation performance. Lower resistor values can be used.  $R_1$  and  $C_{\rm ff}$  place a zero in the loop. The right value for  $C_{\rm ff}$  can be calculated as:

$$f_{c} = \frac{1}{2 \times \pi \times R_{2} \times C_{ff}} = 35kHz$$

$$C_{\rm ff} = \frac{1}{2 \times \pi \times R_2 \times 35 \text{kHz}}$$

### **OUTPUT FILTER DESIGN (INDUCTOR AND OUTPUT CAPACITOR)**

The internal compensation network of TLV62065-Q1 is optimized for an LC output filter with a corner frequency of:

$$f_c = \frac{1}{2 \times \pi \times \sqrt{(1 \mu H \times 10 \mu F)}} = 50 \text{kHz}$$

The part operates with nominal inductors of 1  $\mu$ H to 1.2  $\mu$ H and with 10  $\mu$ F to 22  $\mu$ F small X5R and X7R ceramic capacitors. See the lists of inductors and capacitors. The part is optimized for a 1- $\mu$ H inductor and 10- $\mu$ F output capacitor.

#### **Inductor Selection**

The inductor value has a direct effect on the ripple current. The selected inductor must be rated for its dc resistance and saturation current. The inductor ripple current ( $\Delta I_L$ ) decreases with higher V<sub>I</sub> or V<sub>O</sub>.

Equation 1 calculates the maximum inductor current in PWM mode under static load conditions. The saturation current of the inductor should be rated higher than the maximum inductor current as calculated with Equation 2. This is recommended because during heavy load transients the inductor current rises above the calculated value.

$$\Delta I_{L} = Vout \times \frac{1 - \frac{Vout}{Vin}}{L \times f}$$

(1)

$$I_{Lmax} = I_{outmax} + \frac{\Delta I_{L}}{2}$$

(2)

where:

f = Switching frequency (3 MHz typical)

L = Inductor value

$\Delta I_1$  = Peak-to-peak inductor ripple current

I<sub>Lmax</sub> = Maximum inductor current

A more conservative approach is to select the inductor current rating just for the switch-current limit I<sub>LIMF</sub> of the converter.

The total losses of the coil have a strong impact on the efficiency of the dc-dc conversion and consist of both the losses in the dc resistance  $R_{(DC)}$  and the following frequency-dependent components:

- The losses in the core material (magnetic hysteresis loss, especially at high switching frequencies)

- Additional losses in the conductor from the skin effect (current displacement at high frequencies)

- Magnetic field losses of the neighboring windings (proximity effect)

- Radiation losses

Table 2. List of Inductors

| DIMENSIONS [mm]                | INDUCTANCE µH        | INDUCTOR TYPE         | SUPPLIER    |  |  |

|--------------------------------|----------------------|-----------------------|-------------|--|--|

| $3.2 \times 2.5 \times 1$ max. | 1                    | LQM32PN (MLCC)        | Murata      |  |  |

| $3.7 \times 4 \times 1.8$ max. | 3.7 × 4 × 1.8 max. 1 |                       | Murata      |  |  |

| 4 x 4 x 2.6 max.               | 1.2                  | NRG4026T (wire wound) | Taiyo Yuden |  |  |

| 3.5 × 3.7 × 1.8 max.           | 1.2                  | DE3518 (wire wound)   | ТОКО        |  |  |

### **Output Capacitor Selection**

The advanced fast-response voltage-mode control scheme of the TLV62065-Q1 allows the use of tiny ceramic capacitors. Ceramic capacitors with low ESR values have the lowest output-voltage ripple and are recommended. The output capacitor requires either an X7R or X5R dielectric. Y5V- and Z5U-dielectric capacitors, aside from their wide variation in capacitance over temperature, become resistive at high frequencies and may not be used. For most applications, a nominal 10-µF or 22-µF capacitor is suitable. In small ceramic capacitors, the dc-bias effect decreases the effective capacitance. Therefore a 22-µF capacitor can be used for output voltages higher than 2 V; see the list of capacitors, Table 3.

In case additional ceramic capacitors in the supplied system are connected to the output of the dc-dc converter, the output capacitor  $C_{\text{OUT}}$  must be decreased in order not to exceed the recommended effective capacitance range. In this case, a loop stability analysis must be performed as described later.

At nominal load current, the device operates in PWM mode and the RMS ripple current is calculated as:

$$I_{\text{RMSCout}} = \text{Vout} \times \frac{1 - \frac{\text{Vout}}{\text{Vin}}}{\text{L} \times f} \times \frac{1}{2 \times \sqrt{3}}$$

(3)

#### **Input Capacitor Selection**

Because of the nature of the buck converter having a pulsating input current, a low-ESR input capacitor is required for best input voltage filtering and minimizing interference with other circuits caused by high input voltage spikes. For most applications a 10-µF ceramic capacitor is recommended. The input capacitor can be increased without any limit for better input voltage filtering.

Take care when using only small ceramic input capacitors. When a ceramic capacitor is used at the input and the power is being supplied through long wires, such as from a wall adapter, a load step at the output or VIN step on the input can induce ringing at the  $V_{IN}$  pin. This ringing can couple to the output and be mistaken as loop instability, or could even damage the part by exceeding the maximum ratings.

**CAPACITANCE TYPE** SIZE [mm] **SUPPLIER** 10 µF GRM188R60J106M  $0603: 1.6 \times 0.8 \times 0.8$ Murata 22 µF GRM188R60G226M  $0603: 1.6 \times 0.8 \times 0.8$ Murata 22 µF CL10A226MQ8NRNC  $0603: 1.6 \times 0.8 \times 0.8$ Samsung 10 µF CL10A106MQ8NRNC 0603:  $1.6 \times 0.8 \times 0.8$ Samsung

**Table 3. List of Capacitors**

### **CHECKING LOOP STABILITY**

The first step of circuit and stability evaluation is to look from a steady-state perspective at the following signal

- Switching node, SW

- Inductor current, I<sub>I</sub>

- Output ripple voltage, V<sub>OUT(AC)</sub>

These are the basic signals that must be measured when evaluating a switching converter. When the switching waveform shows large duty cycle jitter, or the output voltage or inductor current shows oscillations, the regulation loop may be unstable. This is often a result of board layout and/or wrong L-C output filter combinations. As a next step in the evaluation of the regulation loop, the transient response of the load is tested. During the time between the application of the load transient and the turnon of the P-channel MOSFET, the output capacitor must supply all of the current required by the load.  $V_{OUT}$  immediately shifts by an amount equal to  $\Delta_{I(LOAD)}$  x ESR, where ESR is the effective series resistance of  $C_{OUT}$ .  $\Delta_{I(LOAD)}$  begins to charge or discharge  $C_{O}$ , generating a feedback error signal used by the regulator to return  $V_{OUT}$  to its steady-state value. The results are most easily interpreted when the device operates in PWM mode at medium-to-high load currents.

During this recovery time,  $V_{OUT}$  can be monitored for settling time, overshoot, or ringing; that helps evaluate stability of the converter. Without any ringing, the loop has usually more than 45 $^{\circ}$  of phase margin.

#### LAYOUT CONSIDERATIONS

Figure 24. PCB Layout

As for all switching power supplies, the layout is an important step in the design. Proper function of the device demands careful attention to PCB layout. Care must be taken in board layout to get the specified performance. If the layout is not carefully done, the regulator could show poor line and/or load regulation, stability issues, as well as EMI and thermal problems. It is critical to provide a low-inductance, low-impedance ground path. Therefore, use wide and short traces for the main current paths. The input capacitor as well as the inductor and output capacitor should be placed as close as possible to the IC pins.

Connect the AGND and PGND pins of the device to the PowerPAD™ land of the PCB and use this pad as a star point. Use a common power node (PGND), and a different node (AGND) for the signal, to minimize the effects of ground noise. The FB divider network should be connected directly to the output capacitor and the FB line must be routed away from noisy components and traces (for example, the SW line).

Due to the small package of this converter and the overall small solution size, the thermal performance of the PCB layout is important. For good thermal performance PCB design of at least four layers is recommended. The thermal pad of the IC must be soldered on the power pad area on the PCB to achieve proper thermal connection. Additionally, for good thermal performance, the thermal pad on the PCB must be connected to an inner GND plane with sufficient via connections. See the documentation of the evaluation kit.

# **Revision History**

The following table summarizes the TLV62065-Q1 data sheet versions.

Note: Numbering may vary from previous versions.

| Version | Literature Number | Date         | Notes   |

|---------|-------------------|--------------|---------|

| *       | SLVSB92           | January 2011 | See (1) |

| A       | SLVSB92A          | March 2012   | See (2) |

- (1) TLV62065-Q1 Data Sheet, (SLVSB92) Initial release.

- TLV62065-Q1 Data Sheet, (SLVSB92A):

- (a) 特性 Update automotive qualitifcation description and add temperature grade

- (b) ABSOLUTE MAXIMUM RATINGS Update Absolute Maximum Ratings

(c) ELECTRICAL CHARACTERISTICS Update Electrical Characteristics Shutdown current max rating

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                     |              |                         |         |

| TLV62065TDSGRQ1  | ACTIVE | WSON         | DSG                | 8    | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 105   | SCD                     | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 5-Jan-2021

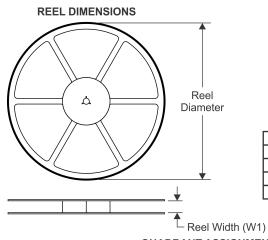

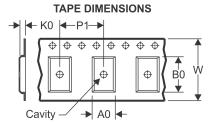

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

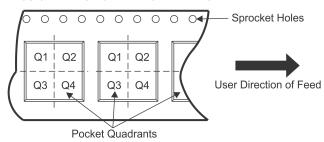

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device          | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLV62065TDSGRQ1 | WSON            | DSG                | 8 | 3000 | 179.0                    | 8.4                      | 2.2        | 2.2        | 1.2        | 4.0        | 8.0       | Q2               |

www.ti.com 5-Jan-2021

#### \*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLV62065TDSGRQ1 | WSON         | DSG             | 8    | 3000 | 213.0       | 191.0      | 35.0        |

2 x 2, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

PLASTIC SMALL OUTLINE - NO LEAD

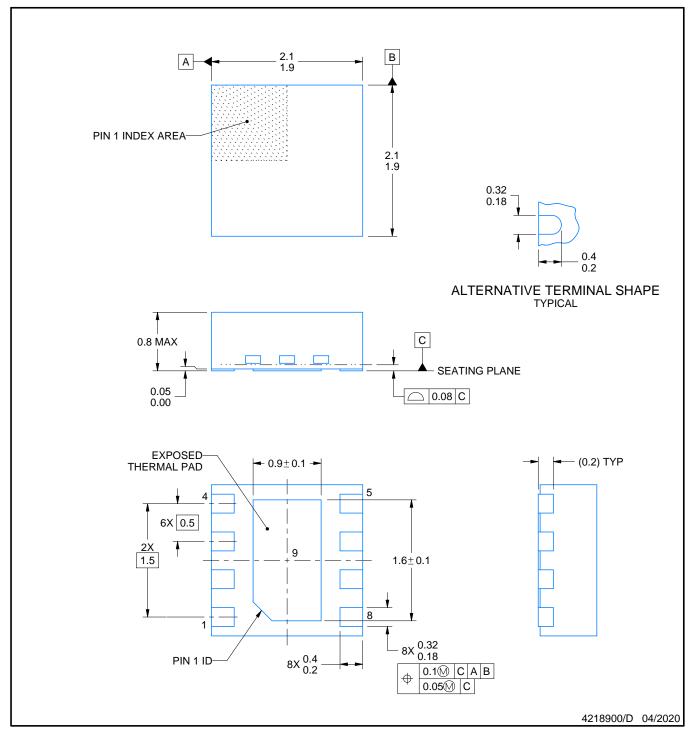

### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

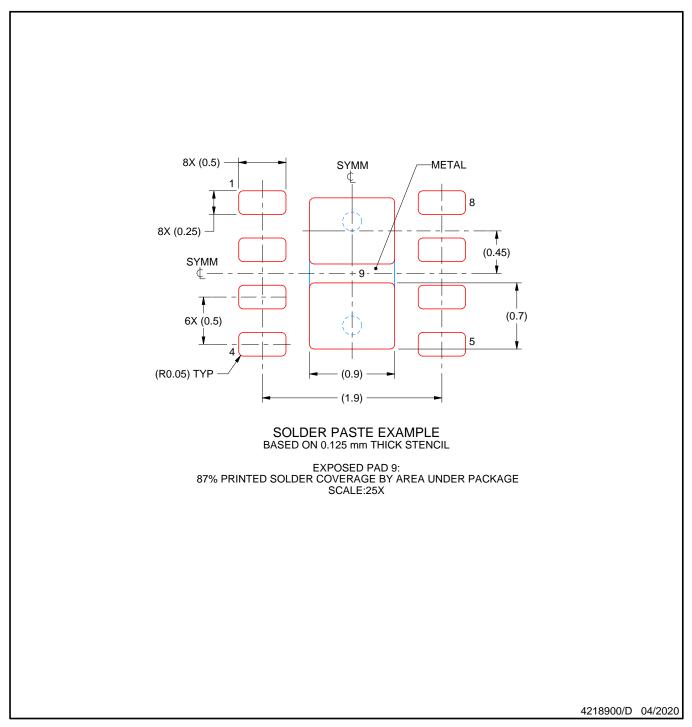

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

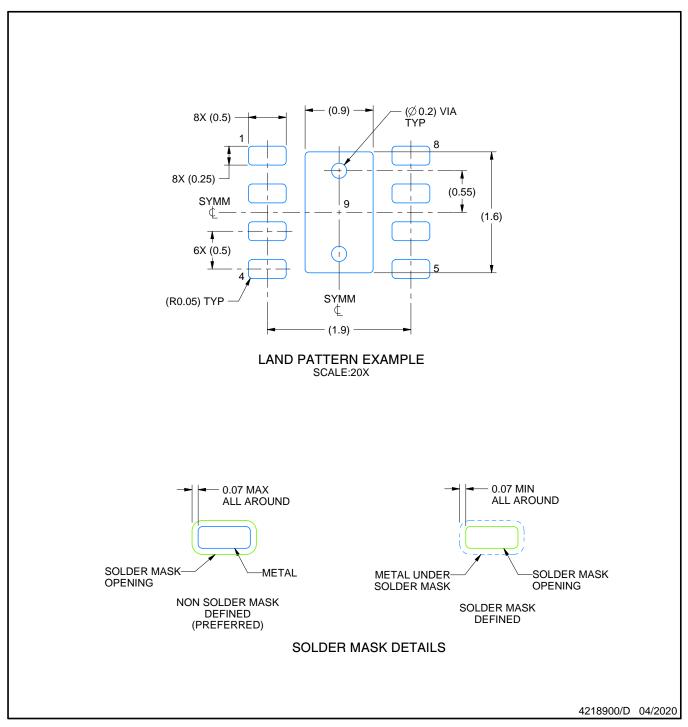

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# 重要声明和免责声明

TI 提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他安全、安保或其他要求。这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款 (https://www.ti.com.cn/zh-cn/legal/termsofsale.html) 或 ti.com.cn 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码:200122 Copyright © 2021 德州仪器半导体技术(上海)有限公司