# Digital Out Temperature Sensor with Single-Wire SensorPath<sup>™</sup> Bus

## **FEATURES**

- SensorPath INTERFACE

- FOUR ADDRESSES

- RESOLUTION: +0.25°C (10-bit)

- WIDE TEMPERATURE RANGE: -40°C to +125°C

- LOW QUIESCENT CURRENT: 110μA (typ)

- TEMPERATURE ACCURACY: ±2°C (max)

- EXTENDED SUPPLY RANGE: +2.7V to +5.5V

- MICRO-SIZE PACKAGES: SOT23-6 or MSOP-8

## APPLICATIONS

- MOTHERBOARDS

- VIDEO CARDS

- BASE STATIONS

- ROUTERS

## DESCRIPTION

The TMP141 is a digital output temperature sensor that utilizes the single-wire SensorPath interface. The TMP141 is capable of measuring temperatures within  $2^{\circ}$ C of accuracy over a temperature range of  $-25^{\circ}$ C to  $+85^{\circ}$ C and  $3^{\circ}$ C of accuracy over  $-40^{\circ}$ C to  $+125^{\circ}$ C. Low supply current, and a supply range from 2.7V to 5.5V, make the TMP141 an excellent candidate for a wide range of low-power applications. The TMP141 is available in SOT23-6 and MSOP-8 packages.

The TMP141 provides a simple, low-cost way to do temperature measurement/monitoring and is ideal as a part of an overall hardware health monitoring system. Up to four TMP141s can be attached to a SensorPath bus. A master configures the TMP141s and reads the temperature output from all devices. No external sensing components are needed for the TMP141 to measure and report temperature.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SensorPath is a trademark of National Semiconductor. All other trademarks are the property of their respective owners.

### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Supply Voltage+7V                                                        |

|--------------------------------------------------------------------------|

| Signal Input Terminals, Voltage <sup>(2)</sup> (V–) –0.5V to (V+) + 0.5V |

| Signal Input Terminals, Current <sup>(2)</sup>                           |

| Maximum Output Current (SWD low) 10mA                                    |

| Operating Temperature55°C to +127°C                                      |

| Storage Temperature60°C to +150°C                                        |

| Junction Temperature+150°C                                               |

| ESD Rating:                                                              |

| Human Body Model (HBM) 4000V                                             |

| Charged-Device Model 1000V                                               |

- (1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

- (2) Input terminals should not be driven beyond the power-supply rails. Input signals that can swing more than 0.5V beyond the supply rails should be current-limited to 10mA or less.

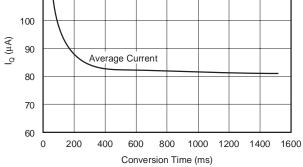

### **ORDERING INFORMATION(1)**

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| PRODUCT | PACKAGE-LEAD    | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|-----------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

|         | <b>COT</b> 22 C |                       | 4000 to 140500                    | <b>T</b> 4.44      | TMP141AIDBVT       | Tape and Reel, 250           |

| TMP141  | SOT23-6         | DBV                   | –40°C to +125°C                   | T141               | TMP141AIDBVR       | Tape and Reel, 3000          |

| TMD4 44 | N005 0          | DOK                   | 4000 10 - 40500                   | 7140               | TMP141AIDGKT       | Tape and Reel, 250           |

| TMP141  | MSOP-8          | DGK                   | –40°C to +125°C                   | T14G               | TMP141AIDGKR       | Tape and Reel, 3000          |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

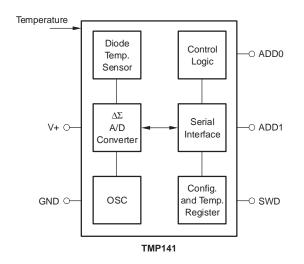

### **PIN CONFIGURATIONS**

### **ELECTRICAL CHARACTERISTICS**

At  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$  and  $V_S = +3.0V$  to +3.6V, unless otherwise noted.

|                                        |                      |                                                       |                    | TMP141 | i                    |      |

|----------------------------------------|----------------------|-------------------------------------------------------|--------------------|--------|----------------------|------|

| PARAMETER                              |                      | CONDITIONS                                            | MIN                | TYP    | MAX                  | UNIT |

| TEMPERATURE INPUT                      |                      |                                                       |                    |        |                      |      |

| Range                                  |                      |                                                       | -40                |        | +125                 | °C   |

| Error                                  | T <sub>ERROR</sub>   | $T = -25^{\circ}C$ to $+85^{\circ}C$                  |                    | ±0.2   | ±2                   | °C   |

|                                        |                      | $T = -40^{\circ}C$ to $+125^{\circ}C$                 |                    |        | ±3                   | °C   |

| vs Supply                              |                      |                                                       |                    | ±0.2   | ±0.5                 | °C/V |

| Resolution                             |                      |                                                       |                    | 10     |                      | Bits |

|                                        |                      |                                                       |                    | 0.25   |                      | °C   |

| Default Conversion Time                | <sup>t</sup> CONV    | See Table 4 for conversion time settings.             | 162                | 190    | 218                  | ms   |

| DIGITAL INPUT/OUTPUT PINS (SWD and )   | ADD pins)            |                                                       |                    |        |                      |      |

| Input/Output Capacitance               | C <sub>IN/OUT</sub>  |                                                       |                    | 3      |                      | pF   |

| SWD PIN                                |                      |                                                       |                    |        |                      |      |

| Input Leakage Current                  | ۱L                   | $GND < V_{IN} < V_{S}$                                |                    | 0.005  | 10                   | μΑ   |

|                                        | ۱L                   | $GND < V_{IN} < 5.5V$ and $V_S = GND/OPEN$            |                    | 0.005  |                      | μΑ   |

| Input Logic Level Voltage (High)       | VIH                  |                                                       | 2.1                |        | V <sub>S</sub> + 0.5 | V    |

|                                        |                      | $V_{S} = 2.7V \text{ to } 5.5V$                       | $0.6 \times V_{S}$ |        | V <sub>S</sub> + 0.5 | V    |

| Input Logic Level Voltage (Low)        | $V_{IL}$             |                                                       | -0.5               |        | 0.8                  | V    |

|                                        |                      | $V_{S} = 2.7V \text{ to } 5.5V$                       | -0.5               |        | $0.25 \times V_S$    | V    |

| Input Hysteresis                       | V <sub>HYST</sub>    | _                                                     |                    | 300    | _                    | mV   |

| Output Logic Level Voltage (Low)       | VOL                  | $I_{OL} = 4mA$                                        |                    |        | 0.4                  | V    |

|                                        |                      | $I_{OL} = 50\mu A$                                    |                    |        | 0.2                  | V    |

| Output OFF Current                     | I <sub>ОН</sub>      |                                                       |                    | 0.005  | 10                   | μΑ   |

| ADD0 and ADD1 PINS                     |                      |                                                       |                    |        |                      |      |

| Input Leakage Current                  | ۱L                   | $GND < V_{IN} < V_{S}$                                |                    | 0.005  | 10                   | μΑ   |

| Input Logic Level Voltage (High)       | VIH                  |                                                       | $0.9 \times V_{S}$ |        | V <sub>S</sub> + 0.5 | V    |

| Input Logic Level Voltage (Low)        | VIL                  |                                                       | -0.5               |        | $0.1 \times V_S$     | V    |

| SensorPath CHARACTERISTICS             |                      |                                                       |                    |        |                      |      |

| SWD Fall Time                          | t <sub>f</sub>       | $R_{PULL-UP} = 1.25 k\Omega \pm 30\%, C_{L} = 400 pF$ |                    |        | 300                  | ns   |

| SWD Rise Time                          | t <sub>r</sub>       | $R_{PULL-UP} = 1.25 k\Omega \pm 30\%, C_{L} = 400 pF$ |                    |        | 1000                 | ns   |

| Min. Inactive Time Between SWD Signals | <sup>t</sup> INACT   | Bus at High Level                                     | 11                 |        |                      | μs   |

| Master or TMP141 Reset Drive Time      | t <sub>RST</sub>     |                                                       | 354                |        |                      | μs   |

| TMP141 Detects Bus Activity            | t <sub>SFEdet</sub>  |                                                       |                    |        | 9.6                  | μs   |

| Master Drive Time                      |                      |                                                       |                    |        |                      |      |

| Data Bit 0 Write, Data Bit 0 Read      | t <sub>MtrO</sub>    |                                                       | 11.8               |        | 17                   | μs   |

| Data Bit 1 Write                       | t <sub>Mtr1</sub>    |                                                       | 35.4               |        | 48.9                 | μs   |

| Start Bit                              | t <sub>MtrS</sub>    |                                                       | 80                 |        | 109                  | μs   |

| TMP141 Drive Time                      |                      |                                                       |                    |        |                      |      |

| Data Bit 0–1 Read                      | t <sub>SLout1</sub>  |                                                       | 28.3               |        | 38.3                 | μs   |

| Attention Request                      | t <sub>SLoutA</sub>  |                                                       | 165                |        | 228                  | μs   |

| Reset                                  | <sup>t</sup> RST_MAX | After V <sub>S</sub> is Above 2.6V                    |                    | 95     | 500                  | ms   |

| POWER SUPPLY                           |                      |                                                       |                    |        |                      |      |

| Specified Voltage Range                |                      |                                                       | 3.0                |        | 3.6                  | V    |

| Operating Voltage Range                |                      |                                                       | 2.7                |        | 5.5                  | V    |

| Quiescent Current                      | lQ                   | Standby                                               |                    | 80     | 120                  | μA   |

|                                        | ~                    | While Converting <sup>(1)</sup>                       |                    | 110    | 170                  | μA   |

| Power-On Reset Voltage                 |                      |                                                       | 1.5                |        | 2.6                  | V    |

| TEMPERATURE RANGE                      |                      |                                                       |                    |        |                      |      |

| Specified Range                        |                      |                                                       | -40                |        | +125                 | °C   |

| Operating Range                        |                      |                                                       | -55                |        | +127                 | °C   |

| Storage Range                          |                      |                                                       | -60                |        | +150                 | °Č   |

| Thermal Resistance                     | $	heta_{JA}$         |                                                       |                    |        |                      | Ĩ    |

| MSOP-8                                 | ~JA                  |                                                       |                    | 150    |                      | °C/W |

| SOT23-6                                |                      |                                                       |                    | 200    |                      | °C/W |

(1) SensorPath activity only has a slight effect on quiescent current.

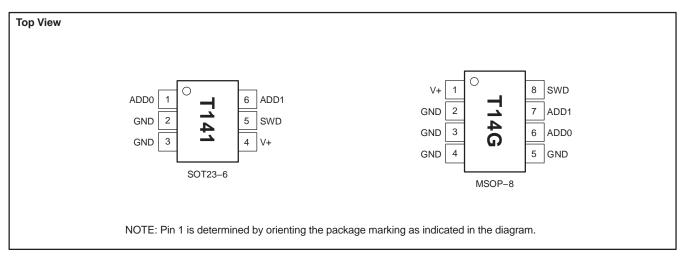

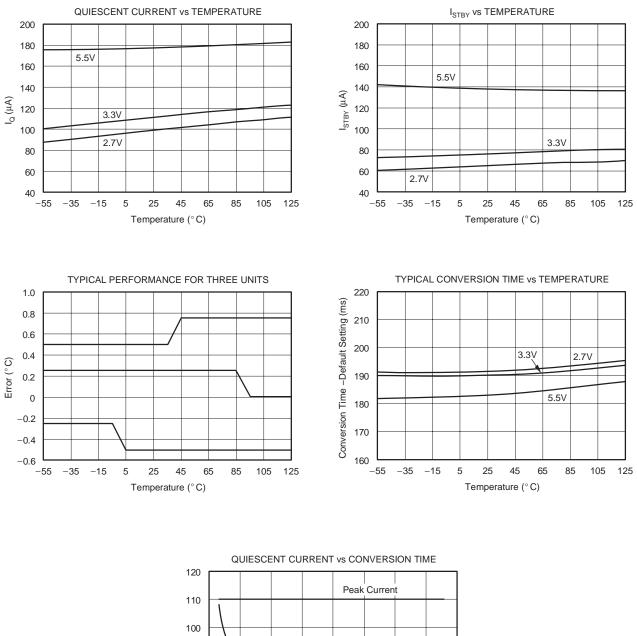

#### **TYPICAL CHARACTERISTICS**

At  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$  and  $V_S = +3.0V$  to +3.6V, unless otherwise noted.

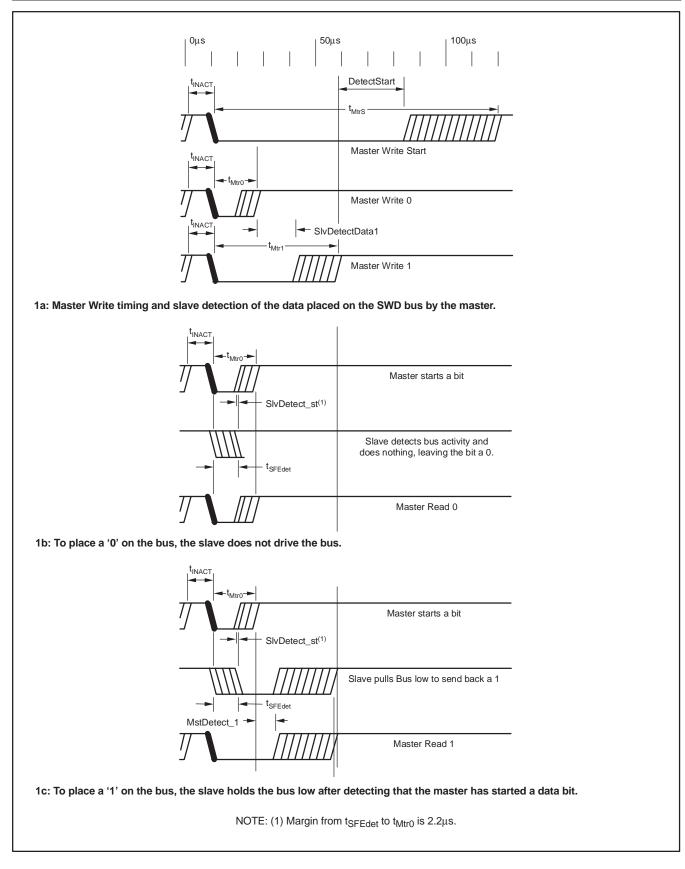

Figure 1. TMP141 Read and Write Signal Timing

## **OVERVIEW**

The TMP141 is a digital output temperature sensor that uses the single-wire SensorPath interface protocol. It does not require any external sensing components for measuring temperature. In order to minimize circuit board space, the TMP141 is offered in the MSOP-8 and SOT23-6 packages.

The primary usage of SensorPath-based systems is for systems that monitor hardware health. The predefined SensorPath functions are: temperature measurement, voltage measurement, and non-volatile memory. The specification allows for expansion by defining new functions or enlarging upon the predefined functions. The TMP141 implements the temperature measurement function with a resolution of 0.25°C.

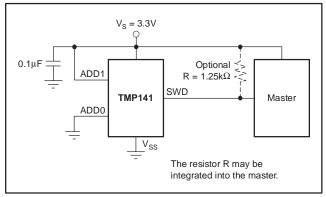

The SensorPath interface allows a master to read up to seven slave devices on a bus, four of which can be TMP141s. The master interrogates devices on the bus to determine what they are, their capabilities, and how they can be used. Devices on the Single-Wire Data (SWD) bus are open drain. Therefore, the SWD bus requires a  $1.25k\Omega$  pull-up resistor on the bus. This resistor may be provided by the master. If the pull-up resistor is not included within the master, an external resistor must be attached to the bus. A  $0.1\mu$ F capacitor is recommended for power-supply bypassing, as shown in Figure 3. Registers inside each device include information that identifies the device capabilities, manufacturer, part ID, and even device revision number.

Figure 3. Typical Connections of the TMP141

# TEMPERATURE SENSING AND CONVERSION

The TMP141 senses the absolute temperature by utilizing a diode which is part of the IC. Therefore, the sensing device of the TMP141 is the chip itself. Thermal paths run through the package leads as well as the plastic package, and the lower thermal resistance of metal causes the leads to provide the primary thermal path.

To maintain accuracy in applications that require air or surface temperature measurement, care should be taken that the package and leads thermally connect with the surface where the temperature measurement is desired. For example, a thermally-conductive adhesive assists in achieving accurate surface temperature measurements. Even without special precautions, because of the very low power consumption of the TMP141, self-heating will normally be well below 1LSB (0.25°C).

### TYPICAL APPLICATION

The TMP141 is normally used with the address pins wired high or low to select one of four possible addresses. The value read from the hardware pins plus one is stored in register 0 as the device number. When the master transmits a matching device number, the TMP141 will respond. In the example shown in Figure 3, ADD1:ADD0 are wired to 2h. In this example, 3h will be stored in register 0. When the master addresses device number 3, the TMP141 in Figure 3 will respond. The TMP141 will also work well in applications where ADD0:ADD1 are driven by logic levels since it reads these pins every time it does a conversion or bus transaction (see Table 2).

#### DIGITAL INTERFACE

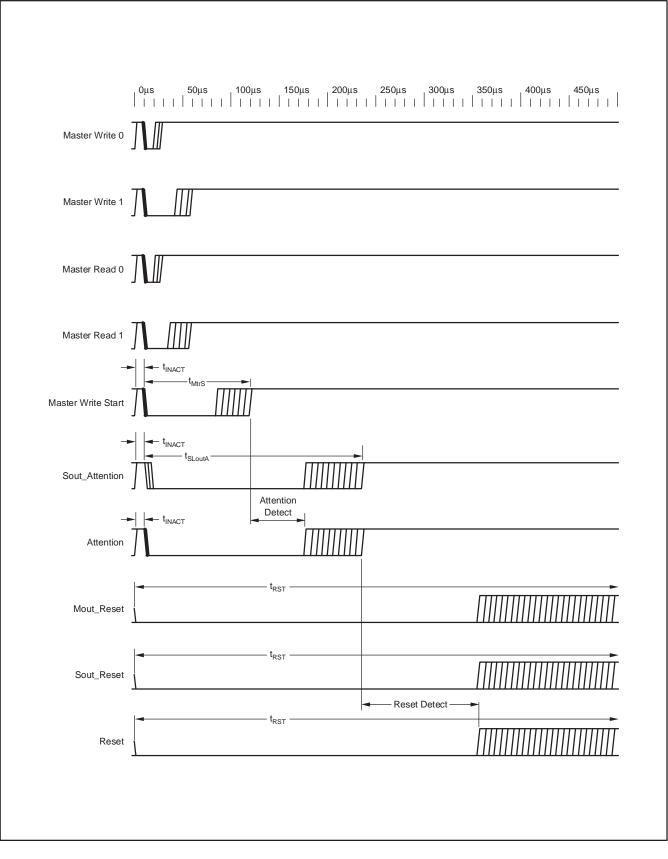

Up to four TMP141 devices can be connected to a single signaling line, which is called Single-Wire Data (SWD). This line is similar to the data line (SMBDAT) of the industry-standard SMBus. The SensorPath bus uses a power supply of 3.3V; therefore, the signaling levels are approximately 3.3V and 0V.

Data is encoded in a pulse width encoding scheme. All signaling is done by pulling the bus low for varying lengths of time. With the exception of Reset and Attention Request, the master starts all bits. Thus, when sending data, the TMP141 does not pull the bus low. Rather, when the TMP141 needs to send a '1', it first detects that the line has been pulled low by the master, and then holds the line low long enough to signal a '1'. To send a '0', the TMP141 simply leaves the bus alone; the master has already placed a '0' on the bus.

The SWD interface used on the TMP141 has five types of signals that are identified by the length of time that the line is held low. Conceptually, this device operates as a five-state signaling system. The more common signals have shorter durations in order to speed overall transmission. The five signals and their approximate times are:

- Data 0: Transmit a '0' bit (15µs)

- Data 1: Transmit a '1' bit (42μs)

- Start: Used by the master at the beginning of a transaction (95µs)

- Attention Request: May be used by the TMP141 to request service (196µs)

- Reset: Must be asserted by both the master and slave(s) after power up. It may be asserted at other times as needed (at least 348μs).

The bus must be inactive for at least  $11 \mu s$  before any signal.

#### Start

All devices on the bus continuously monitor the bus. The master also monitors the bus to verify that it is inactive before issuing a Start Bit. During the Start Bit, both the master and slave(s) monitor the bus to detect an Attention Request or a Reset. If there is an Attention Request, or a Reset, the current signal is not treated as a Start Bit. The master may reissue the Start Bit at a later time, but is not required to.

#### **Attention Request**

Any slave device may signal an Attention Request. Before sending an Attention Request, the slave monitors the bus to ensure that it is inactive. If an Attention Request coincides with a data bit from another device or a Start Bit from the master, the Attention Request will take precedence since the Attention Request signal holds the bus low longer. The master and all communicating slaves will monitor the bus to detect an Attention Request. The master monitors the bus in order to allow resending, in case the Attention Request started simultaneously with a Start Bit or a data bit. If the master was in the midst of a transaction when the Attention Request was asserted, the master can either continue with the transaction by repeating the bit that was extended by the Attention Request, initiating the next bit if a bit was not extended, or it can service the Attention Request by issuing a new start command for a new transaction.

#### **Power-On Reset**

All devices on the SWD bus, including the TMP141, are required to generate a Reset signal at power up. Reset aborts any operation in progress, and sets all registers to the default values. The device that holds SWD low the longest will define how long the Reset lasts. After a Reset, a slave device may not send an Attention Request until the master has sent at least 14 bits of data on the SWD bus.

#### **Device Reset**

The TMP141 will also Reset when the Reset bit is written to the Device Control Register (bit 0). All registers are set to the default value. The two least significant bits of the Device Control Register are the only locations that respond to a broadcast write command from the master.

A software-programmed reset of a device by writing to its Device Control Register will not cause a Reset signal on the bus.

### **BUS RESET**

A Bus Reset occurs when the TMP141 detects a Reset signal on the SWD bus. Upon Bus Reset, the TMP141 will abandon any communication in progress. Internal registers are not reset to their power-up values; thus, any error flags such as BER or ORUN will remain unaffected. If a conversion was in progress, it will continue to completion.

#### **Read and Write Transactions**

A complete Read transmission consists of a Start Bit, the device number, the Register Number, R/W = 1, the data bits, an even parity bit, and an Acknowledge bit. The most significant bit is sent first.

| START | DEVI | CE NUMBER REGISTER NUMBER |   |   |       |  |   | R/W | 8 or 16 DATA BITS | EP | ACK |   |   |  |  |

|-------|------|---------------------------|---|---|-------|--|---|-----|-------------------|----|-----|---|---|--|--|

| М     | М    | М                         | М | М | M M M |  | М | М   | М                 | М  | S S | S | М |  |  |

#### **Read Transaction**

A complete Write transmission consists of a Start Bit, the device number, the Register Number, R/W = 0, the data bits, an even parity bit, and an Acknowledge bit.

#### Write Transaction

| START | DEVICE NUMBER REGISTER NUMBER |   |   |   |   |   |   | R/W | 8 or 16 DATA BITS | EP | ACK |   |   |

|-------|-------------------------------|---|---|---|---|---|---|-----|-------------------|----|-----|---|---|

| М     | М                             | М | М | М | М | М | М | М   | М                 | М  | М М | М | S |

*M* indicates that the bit is initiated and controlled by the master. *S* indicates that the bit is initiated by the master but controlled by the slave; if the data is a '1', the slave lengthens the time that the bus is held low to signal a '1'.

The device number is three bits long. Device number 0 is reserved for a broadcast to all devices, leaving address space for seven slaves.

The Register Number is six bits long.

The R/W is a '1' for a read operation. The R/W bit is a '0' for a write operation.

All data bits are started by the master pulling the bus low. The TMP141 will detect the bus being low within time t<sub>SFEdet</sub>. If it is a read transaction and the TMP141 needs to send a '1' for that bit period, it will hold the bus low for time t<sub>SLout1</sub>.

In a Write operation, the data bits and parity are sent by the master. In a Read operation, the data bits and parity are sent by the TMP141. Data length is eight bits for registers 0, 4, and 20h. All other registers are 16 bits long. The number of bits transmitted or received depends on the length of the register: 8 bits for an 8-bit register and 16 bits for a 16-bit register.

Even parity (EP) is used on the SensorPath. The parity calculation includes all bits after the Start Bit, up to and including the parity bit. Thus, the parity calculation includes the device number, the Register Number,  $R/\overline{W}$ , the data bits, and the parity bit. In a Write operation, the TMP141 checks the parity sent by the master before generating the Acknowledge bit.

The Acknowledge bit is sent by the receiving unit. In a Write operation, the Acknowledge bit will come from the TMP141. In a Read operation, the master generates the Acknowledge bit.

#### ACKNOWLEDGE Bit Definition:

1: A complete data transmission was completed without a parity error.

0: An error was detected. (BER in the Status Register will be set. An Attention Request will be generated.)

## **APPLICATIONS INFORMATION**

| ADDRESS        |                             |                       | RESET |      |                                                           |           | BIT P      | OSITIC  | ON (MS   | B to th | he left. In       | a transn                 | nission, th | ne M  | SB is ser  | nt first.   | )       |            |               |   |   |

|----------------|-----------------------------|-----------------------|-------|------|-----------------------------------------------------------|-----------|------------|---------|----------|---------|-------------------|--------------------------|-------------|-------|------------|-------------|---------|------------|---------------|---|---|

| (hex)          | NAME                        | R/W                   | (hex) | 15   | 14                                                        | 13        | 12         | 11      | 10       | 9       | 8                 | 7                        | 6           | 5     | 4          | 3           | 2       | 1          | 0             |   |   |

|                | Device                      | _                     | 1(1)  |      |                                                           |           |            |         |          |         |                   |                          | Res         | serve | ed         | See Table 2 |         |            |               |   |   |

| 0              | Number                      | R                     | 1(1)  |      | Not Available (this register is 8 bits long) 0 0 0        |           |            |         |          |         | 0                 | 0                        | 0           | AS2   | AS1        | AS0         |         |            |               |   |   |

| 1              | Manufacturer<br>ID          | R                     | 104C  | 0    | 0                                                         | 0         | 1          | 0       | 0        | 0       | 0                 | 0                        | 1           | 0     | 0          | 1           | 1       | 0          | 0             |   |   |

| 2              | Device ID                   | R                     | 8D    |      | Re                                                        | evision I | D          |         |          |         |                   |                          | De          | vice  | ID         |             |         | •          |               |   |   |

| 2              | 2 Device ID R               | ĸ                     | 00    | 0    | 0                                                         | 0         | 0          | 0       | 0        | 0       | 0                 | 1                        | 0           | 0     | 0          | 1           | 1       | 0          | 1             |   |   |

| 3              | Capabilities                | R                     | 1     |      | -                                                         | -         | -          |         | Re       | eserve  | d                 |                          | -           |       |            |             | Fu      | nction 1   |               |   |   |

| 5 Capabilities | ĸ                           | n                     | г     | ĸ    | 1                                                         | 0         | 0          | 0       | 0        | 0       | 0                 | 0                        | 0           | 0     | 0          | 0           | 0       | 0          | 0             | 0 | 1 |

| 4              | Status                      | R                     | 0     |      | Not Available (this register is 8 bits long) BER 0 0 ORUN |           |            |         |          |         |                   |                          | 0           | 0     | 0          | SF1         |         |            |               |   |   |

| 5              | Device                      | Device<br>Control R/W | 0     |      |                                                           |           |            |         | Reserv   | red     |                   |                          |             |       | ENAB       | Res         | Low     | Shut       | Reset         |   |   |

| 5              | Control                     |                       | Ū     | 0    | 0                                                         | 0         | 0          | 0       | 0        | 0       | 0                 | 0                        | 0           | 0     | LINAD      | 0           | Pwr     | Down       | Reset         |   |   |

| 8              | Temperature<br>Capabilities | R                     | 014A  |      |                                                           | Re        | eserved    |         |          |         | Internal<br>Sense | R <sub>OUT</sub><br>Size | Sign        | R     | esult is10 | Bits        | Reso    | olution Is | 0.25°C        |   |   |

|                | Capabilities                |                       |       | 0    | 0                                                         | 0         | 0          | 0       | 0        | 0       | 1                 | 0                        | 1           | 0     | 0          | 1           | 0       | 1          | 0             |   |   |

| 9              | Temperature                 | mperature R           | 0     | Sign | 64°C                                                      | 32°C      | 16°C       | 8°C     | 4°C      | 2°C     | 1°C               | 0.5°C                    | 0.25°C      |       |            | Re          | eserved |            |               |   |   |

| 9              | Readout                     | ĸ                     | 0     | Sign | 64°C                                                      | 3210      | 10.0       | 0.0     | 4.0      | 2.0     | PC                | 0.5 °C                   | 0.25°C      | 0     | 0          | 0           | 0       | 0          | 0             |   |   |

| А              | Temperature                 | R/W                   | 0     |      |                                                           |           |            |         |          |         |                   |                          |             |       |            |             |         | EN S       | AT E          |   |   |

| A              | Control                     | F\/ V V               | 0     | 0    | 0                                                         | 0         | 0          | 0       | 0        | 0       | 0                 | 0                        | 0           | 0     | 0          | 0           | 0       | EN_3       | AI_E          |   |   |

| B–1F           | Reserved                    | R                     |       |      |                                                           |           |            |         |          |         | Un                | defined                  |             |       |            |             |         |            |               |   |   |

| 20             | Conversion<br>Rate          | R/W                   | 2(2)  |      | Not A                                                     | Available | e (this re | egister | is 8 bit | s long) | )                 | 0                        | 0           | 0     | 0          | 0           | 0       |            | ersion<br>ate |   |   |

| 21–3F          | Undefined                   |                       |       |      |                                                           |           |            |         |          |         | Un                | defined                  |             |       |            |             |         | •          |               |   |   |

#### Table 1. Register Set Summary

(1) See Table 2 for the value of register 0 at Reset.

(2) See Table 4 for the conversion rate settings.

### **REGISTER DETAILS**

#### Register 0: Device Number (Read-Only)

Register 0 is an 8-bit register. The device number is created from the inputs at the address pins. The result is placed in Register 0 according to Table 2.

| ADD1:ADD0 | AS2:AS0<br>BITS 2:0 |

|-----------|---------------------|

| 00        | 001                 |

| 01        | 010                 |

| 10        | 011                 |

| 11        | 100                 |

ADD1 and ADD0 are the physical pins used to define the address to which the TMP141 responds to—they are not the actual addresses. AS2:AS0 is the address to which the device responds.

Device number 000b is the broadcast address reserved for communicating with all devices, and can be responded to by all slave devices. The TMP141 ignores a broadcast Read transaction. A broadcast Write message may be used to write to the Device Control Register, which is the only register which responds to broadcast messages (see the *Device Control Register* description).

### Register 1: Manufacturer ID (Read-Only)

The Manufacturer ID for Texas Instruments is 104Ch.

#### Register 2: Device ID (Read-Only)

The device ID is unique for each device produced by TI. Bits 10:0 contain 8Dh, which is the identifier for the TMP141. Bits 15:11 identify the revision of the die and will be incremented upon device revision.

#### Register 3: Capabilities (Read-Only)

Function 1 for the TMP141 is temperature measurement; this is the only function defined for the TMP141. This register has the value of 1h.

#### Register 4: Device Status (Read-Only)

This is an 8-bit register with the following bits defined:

**Bit 7, Bus Error (BER):** This bit is set whenever there is an error indication in the Acknowledge bit of either received or transmitted data. A bus error is cleared when the master reads the Device Status Register or sends Device Reset.

Bits 6-5: Reserved. These bits read as '0'.

**Bit 4, Overrun (ORUN):** This flag is set when another temperature conversion is completed before the previous conversion has been read by the master. This error is cleared by Device Reset, or by reading the temperature result from the Temperature Readout register.

Bits 3–1: Reserved. These bits read as '0'.

**Bit 0, Status Function 1 (SF1):** This flag is set when a temperature conversion is completed, and the data is stored in the Readout register. It is reset either when the master reads the temperature conversion, or when the TMP141 is reset.

#### Register 5: Device Control (Read/Write)

Bits 15-5: Reserved. These bits read as '0'.

**Bit 4, Enable Function 1 (ENAB):** This bit enables temperature measurement; the default setting is disabled. To begin temperature measurement, a '1' must be written to this bit. The enable sensor bit (EN\_S) in the Temperature Control register must also be set to enable the sensor. (Bits cannot be written individually; a Write operation affects the entire register.)

Bit 3: Reserved. This bit reads as '0'.

**Bit 2, Low-Power Mode:** When this bit is set, the operation of all functions slow down in order to conserve power. Default is '0' for normal speed operation. (See Table 4.)

**Bit 1, Shutdown:** When this bit is set, all functions are disabled, placing the TMP141 in the lowest possible power consumption mode. Default is '0'; this is normal operation. To exit shutdown, write a '0' to this location.

**Bit 0, Reset:** When this bit is set, the TMP141 performs a Device Reset. During Reset, any operation is progress is aborted, and all registers are set to their default values. This bit self-clears when the Reset operation is completed. It is not necessary to do a Device Reset after power-up.

**Bits 1–0:** These bits are the only location in the TMP141 that accepts a broadcast Write message.

#### SBAS347A - MARCH 2005 - REVISED JULY 2006

#### Register 8: Temperature Capabilities (Read-Only)

Bits 15-9: Reserved. These bits read as '0'.

**Bit 8:** This bit is set, indicating that the internal temperature sensing is the only option available.

**Bit 7:** This bit is '0'; it indicates that the TMP141 Temperature Readout register is 16 bits.

**Bit 6:** This bit is set to indicate that signed two's complement is the format of the temperature data.

**Bits 5–3:** These bits are 001b; they indicate that the temperature data is 10 bits long.

**Bits 2–0:** These bits are 010b, and indicate that the temperature data resolution is 0.25°C.

#### Register 9: Temperature Readout (Read-Only)

The TMP141 outputs 10 bits of precision to a resolution of  $0.25^{\circ}$ C. This 10-bit format covers a range from +127.75°C to -128°C. Negative numbers are in two's complement. Table 3 shows some examples of the Temperature Data format.

Data is left-justified, meaning that the ten bits of data are in the most significant bits of this register. The temperature data is contained in Bits 15:6. Bits 5:0 always read as '0'.

| TEMPERATURE              | BINARY       | HEX  |

|--------------------------|--------------|------|

| +127.75°C <sup>(1)</sup> | 01 1111 1111 | 1FFh |

| +125.00°C                | 01 1111 0100 | 1F4h |

| +100.0°C                 | 01 1001 0000 | 190h |

| +1.0°C                   | 00 0000 0100 | 004h |

| +0.25°C                  | 00 0000 0001 | 001h |

| 0°C                      | 00 0000 0000 | 000h |

| −0.25°C                  | 11 1111 1111 | 3FFh |

| -1.0°C                   | 11 1111 1100 | 3FCh |

| -100°C                   | 10 0111 0000 | 270h |

| -128°C <sup>(1)</sup>    | 10 0000 0000 | 200h |

Table 3. Data Format Example

(1) Both -128°C and +127.75°C are beyond the specified operating range of -40°C to +125°C. This table only illustrates the format of the data.

#### **Register Ah: Temperature Control (Read/Write) Bits 15–2:** Reserved. These bits read as '0'.

**Bit 1, Enable Sensor (EN\_S):** Default is '0', which is the disabled state. In addition to setting this bit, the enable bit in register 5 must also be set in order to measure temperature.

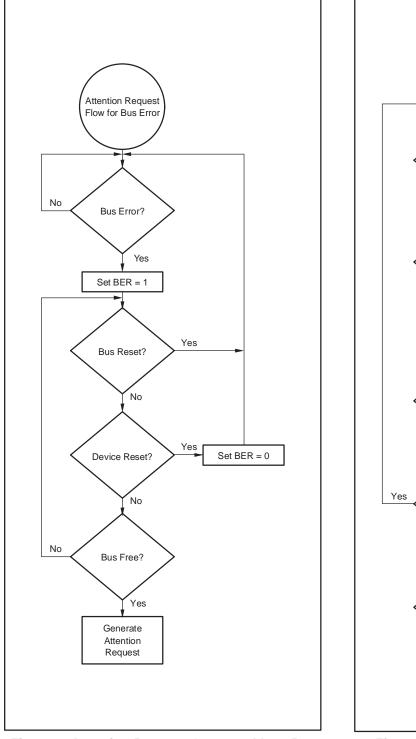

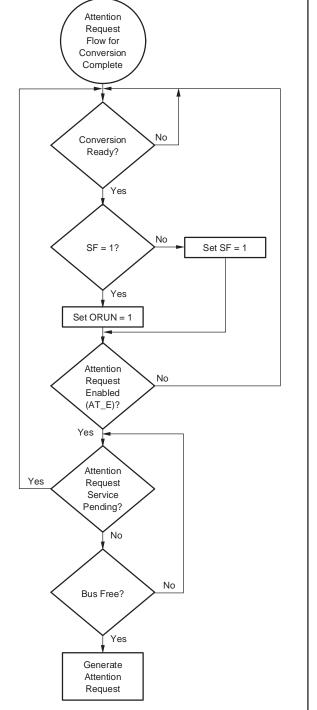

**Bit 0, Attention Enable (AT\_E):** Default is disabled. When this bit is set, and the sensor is enabled (bit 1), the TMP141 will generate Attention Requests. If enabled, an Attention Request will be generated when a bit is set in the Device Status register (register 4). See Figure 5 for the details on the conditions for generating an Attention Request.

Note: A bus error always attempts to generate an Attention Request.

(For more information on the Attention Request conditions, see the flowcharts in Figure 4 and Figure 5, and the information on Exception Handling on page 14.)

The rules for generating an Attention Request are different, depending on whether it was caused by a bus error or a temperature conversion. A bus error always attempts to generate an Attention Request, whereas a conversion or a conversion overrun has several conditions that may prevent the assertion of Attention Request. These differences are illustrated in Figure 4 and Figure 5.

#### Register 20h: Conversion Rate (Read/Write)

The conversion rate is controlled by both the low-power bit in the Device Control register, and the Conversion Rate setting in the Conversion Rate register. This register is device-specific, and therefore not defined by the SensorPath specification. The conversion rate for a given application is chosen based on system requirements and limitations, such as the thermal response time of the system (including the TMP141).

| Table 4 | Conversion | Time | Settings |

|---------|------------|------|----------|

|---------|------------|------|----------|

| LOW-POWER<br>MODE<br>(register 5, bit 2) | CONVERSION<br>RATE SETTING<br>(register 20h, bits<br>1–0 binary) | TYPICAL<br>CONVERSION<br>TIME<br>(ms) |

|------------------------------------------|------------------------------------------------------------------|---------------------------------------|

| 0                                        | 00                                                               | 64                                    |

| 1                                        | 00                                                               | 96                                    |

| 0                                        | 01                                                               | 96                                    |

| 1                                        | 01                                                               | 382                                   |

| 0                                        | 10                                                               | 190 (default)                         |

| 1                                        | 10                                                               | 766                                   |

| 0                                        | 11                                                               | 382                                   |

| 1                                        | 11                                                               | 1532                                  |

Figure 4. Attention Request Generated by a Bus Error

Figure 5. Attention Request Generated by a Conversion Complete

## **EXCEPTION HANDLING**

### ATTENTION REQUEST

Two conditions can cause the TM141 to generate an Attention Request: a conversion completion and a bus error.

Upon completion of a conversion, an Attention Request may be asserted if an Attention Request is enabled (bit 0 in the Temperature Control register), if the bus is inactive, and if there has not been an Attention Request on the bus since the Device Status register was last read or the last bus reset.

A slave generates an Attention Request by holding the bus low for time  $t_{SLoutA}$ . Because it is longer than any other signal (except Reset), it takes priority over the other bus signals (Start, Data 1, and Data 0).

### ATTENTION REQUEST SERVICE

The master is required to read the status register of all slaves after an Attention Request to determine which slave sent the request. While an Attention Request service is pending, no slave can generate another Attention Request to request a read of its Temperature Readout register. However, Attention Requests caused by bus errors will continue to be generated.

### ACKNOWLEDGE (ACK)

During a Read transaction, the master sends the ACK bit to indicate that the even parity (EP) bit was received, found to be correct when compared to the data preceding it, and no conflict was detected on the bus. During a Write transaction, the slave sends the ACK bit with the same meaning as when the master sends it. A transaction is considered *complete* only when the ACK bit is received. If an ACK bit of '1' is not received during a Write transaction, the TMP141 will not perform any internal operations based on that transaction. A transaction with an Acknowledge bit of 0 is not considered *complete* by the TMP141, and the following actions are performed:

- 1. The bus error bit in the TMP141 Device Status register is set.

- 2. The TMP141 generates an Attention Request before (or together with) the Start Bit of the next transaction.

A transaction that was not positively acknowledged is also not considered *complete* by the master (that is, the master will not use data that it received from a transaction that was not acknowledged). The transaction may be repeated by the master after detecting the source of the Attention Request (the TMP141 or other slave that has a set BER bit in the Device Status Register). Note that the SensorPath protocol neither forces, nor automates re-execution of, the transaction by the master.

#### **Incomplete Transactions:**

If the TMP141 receives a Start Bit during a transaction, it aborts the current transaction, and begins a new one. This process is not recommended, but is a legal operation. No error will be generated.

If excess bits are received, the extra bits are ignored. The TMP141 expects the parity (EP) and acknowledge (ACK) bits in the usual places. However, in such cases, there is usually a parity error, and the transaction is not acknowledged. Error handling proceeds as described in the *Acknowledge* section.

If insufficient bits are received, the TMP141 will wait indefinitely for the missing bits. If the master starts a new transaction before those bits are received, the TMP141 abandons the current transaction, and begins the new transaction. No error is generated.

## GLOSSARY

**ACK (Acknowledge Bit):** The bit that concludes a transmission indicating whether any errors were detected in the transmission. A '1' indicates that no errors were found; a '0' indicates an error. An acknowledge error causes BER to be set. BER will be set regardless of whether the device or the master generates the acknowledge error.

**AT\_E (Attention Enable):** This is the LSB in the Temperature Control register (bit 0, register Ah). When set, the TMP141 will generate Attention Requests. If enabled, an Attention Request will be generated when a conversion is complete.

**BER (Bus Error):** A flag that is set when the TMP141 either generates or receives an Acknowledge error (bit 7 in the Status register).

**EN\_S: (Sensor Enable Bit):** This is bit 1 in the Temperature Control register. When set, temperature measurement is enabled. Default setting is disabled. To report temperature, ENAB must also be set.

**ENAB (Enable Temperature Sensing):** This is a bit in the Device Control register. In the case of the TMP141, function 1 is temperature measurement. Setting this bit will enable temperature measurement (bit 4 in the Device Control register). The sensor should also be turned on by the Sensor Enable flag (bit 1) in the Temperature Control register.

**Even Parity:** The number of bits in a transmission that are '1' is even. The SensorPath uses even parity. All bits after the start bit (up to and including the parity bit) are included in this calculation, but the ACK bit is not.

**ORUN (Overrun Error):** This flag is set when a temperature conversion is completed before the previous conversion has been read by the master (bit 4 in the Device Status register). If other conditions are met, overrun will generate an Attention Request.

**PCI SIG (assigned identifiers):** The ID for Texas Instruments is 104Ch. This number is programmed into the Manufacturer ID register. Other IDs can be fond at http://www.pcisig.com/membership/vid\_search/. This number enables identification of the device manufacturer (which can be useful in determining the features of a device) and to perform manufacturer-specific operations. There are no vendor-specific operations for the TMP141—all of the operations conform to industry standards.

**Pulse Width Encoding:** A signaling scheme whereby the information is differentiated by the width of the pulse. In the case of SensorPath, the pulses are created by pulling the bus low. The length of time that it is low determines the meaning of that pulse. See the *Digital Interface* section on page 8.

**SF1 (Status Function One):** This flag is set when a temperature conversion is completed, and the data is stored in the Readout register. It is reset when the master reads the temperature conversion, or when the TMP141 is reset.

**Shutdown Mode:** A very low-power state entered when the master writes to the shutdown bit (bit 1) in the Device Control register. In the shutdown state, temperature conversions are stopped. The TMP141 consumes the lowest possible power in this state (see also *Low-Power Mode* on page 11).

**SWCLK:** Single-Wire Clock, an optional signal used only when the SensorPath is used in synchronous mode. The TMP141 does not use and does not support this option. Systems that use SWCLK are using a two-wire SensorPath bus.

**SWD (Single-Wire Data):** The line used to communicate between master and slave devices as required by the specified SensorPath. Five types of signals go over this line (Zero, One, Start, Attention Request, and Reset). Signals are differentiated by the length of time that they hold the bus low. This is the only line used to communicate between the slaves, such as the TMP141, and the master. A  $1.25k\Omega$  pull-up resistor may be integrated into the master, or it may be external.

**Synchronous Mode:** An optional mode used with SensorPath devices that do not meet the  $\pm$ 15% clock timing accuracy requirement. The TMP141 clock meets the clock accuracy requirement, and therefore does not support the synchronous mode (see *SWCLK*).

4-Feb-2021

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|---------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                 | (6)                           |                     |              |                         |         |

| TMP141AIDBVT     | ACTIVE        | SOT-23       | DBV                | 6    | 250            | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 125   | T141                    | Samples |

| TMP141AIDGKR     | ACTIVE        | VSSOP        | DGK                | 8    | 2500           | RoHS & Green    | NIPDAU   NIPDAUAG             | Level-2-260C-1 YEAR | -40 to 125   | T14G                    | Samples |

| TMP141AIDGKT     | ACTIVE        | VSSOP        | DGK                | 8    | 250            | RoHS & Green    | NIPDAUAG                      | Level-2-260C-1 YEAR | -40 to 125   | T14G                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

www.ti.com

4-Feb-2021

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

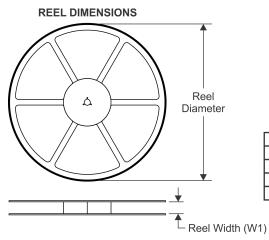

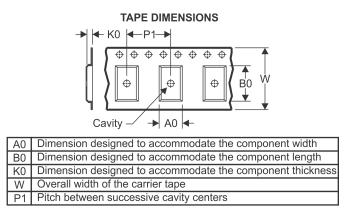

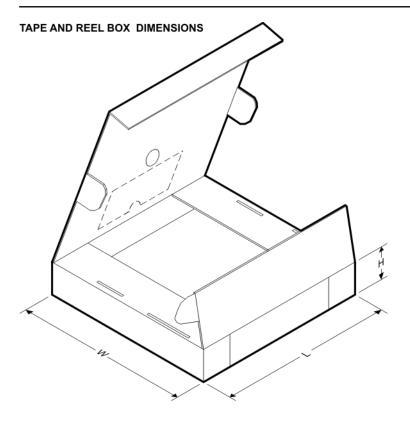

### TAPE AND REEL INFORMATION

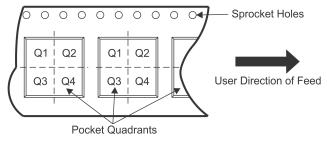

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TMP141AIDBVT                | SOT-23          | DBV                | 6 | 250  | 180.0                    | 8.4                      | 3.15       | 3.1        | 1.55       | 4.0        | 8.0       | Q3               |

| TMP141AIDGKR                | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TMP141AIDGKT                | VSSOP           | DGK                | 8 | 250  | 180.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

## PACKAGE MATERIALS INFORMATION

18-Nov-2020

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TMP141AIDBVT | SOT-23       | DBV             | 6    | 250  | 210.0       | 185.0      | 35.0        |

| TMP141AIDGKR | VSSOP        | DGK             | 8    | 2500 | 853.0       | 449.0      | 35.0        |

| TMP141AIDGKT | VSSOP        | DGK             | 8    | 250  | 210.0       | 185.0      | 35.0        |

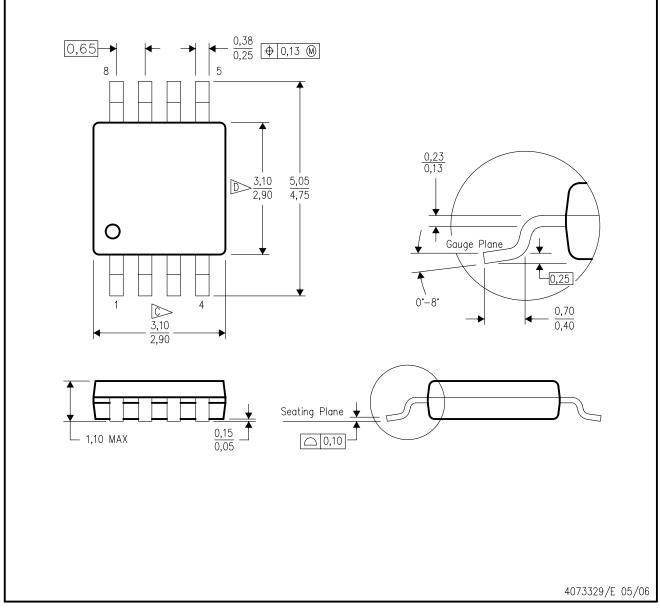

DGK (S-PDSO-G8)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- D Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

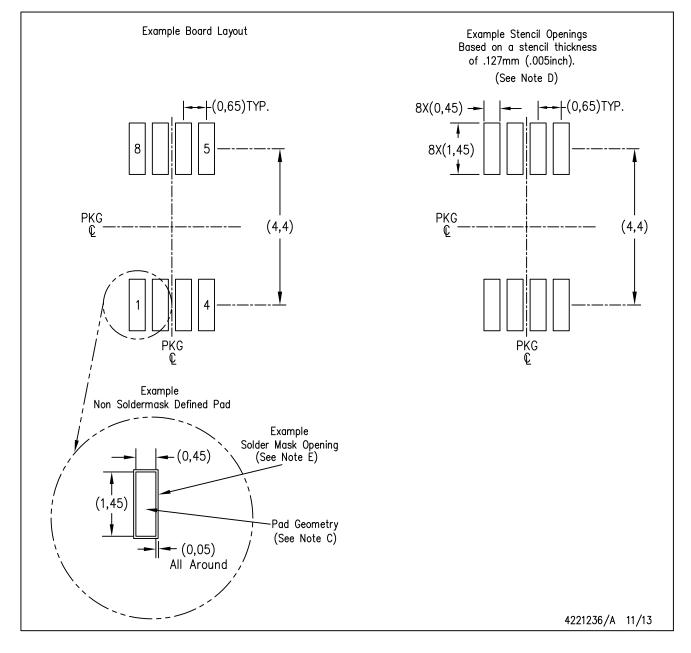

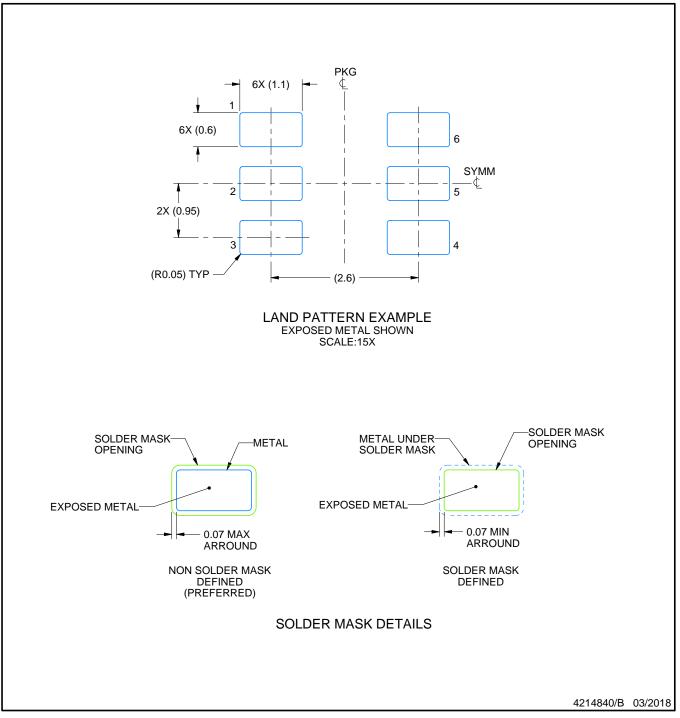

## DGK (S-PDSO-G8)

## PLASTIC SMALL OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

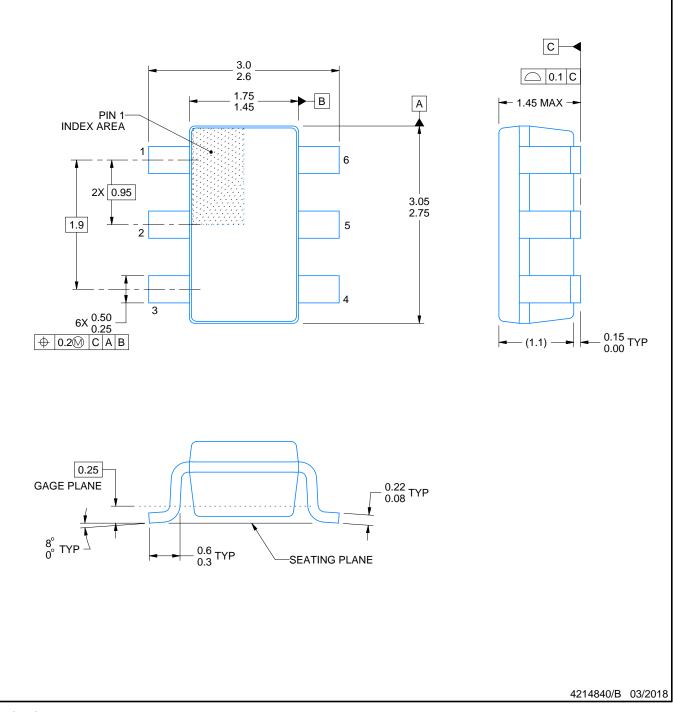

## **DBV0006A**

## **PACKAGE OUTLINE**

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.2. This drawing is subject to change without notice.3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- 4. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation. 5. Refernce JEDEC MO-178.

## **DBV0006A**

## **EXAMPLE BOARD LAYOUT**

### SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

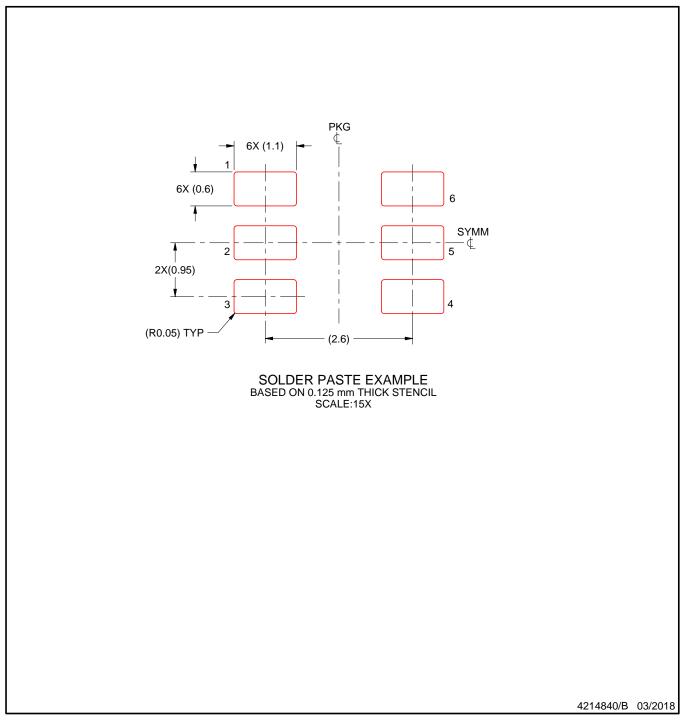

## **DBV0006A**

## **EXAMPLE STENCIL DESIGN**

### SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated